利用FPGA來實現(xiàn)USB 2.0接口的方式一般有兩種,一是借助外圍的USB接口芯片,二是FPGA內(nèi)部實現(xiàn)USB協(xié)議控制器,外部通過USB的PHY芯片來實現(xiàn)接口。

對于第一種方式,F(xiàn)PGA不需要實現(xiàn)USB通信協(xié)議,開發(fā)的風(fēng)險小,而且性能穩(wěn)定,因此被大部分設(shè)計者所采用。而第二種方式需要購買USB的IP核,門檻較高。如果自己開發(fā)基于FPGA的USB協(xié)議棧,風(fēng)險高,而且兼容性和穩(wěn)定性很難保證。

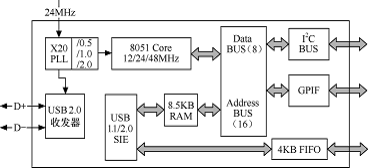

目前市場上的USB 2.0接口芯片廠家和型號比較多,其中Cypress Semiconductor公司的EZ-USB FX2(CY7C68013)是世界上第一款集成USB 2.0的微處理器,它集成了USB 2.0收發(fā)器、SIE(串行接口引擎)、增強的8051微控制器和可編程的外圍接口。

FX2這種獨創(chuàng)性結(jié)構(gòu)可使數(shù)據(jù)傳輸率達到56MByte/s,即USB 2.0允許的最大帶寬。在FX2中,智能SIE可以硬件處理許多USB 1.1和USB 2.0協(xié)議,從而減少了開發(fā)時間、確保了USB的兼容性。

GPIF(General Programmable Interface)和主/從端點FIFO(8位或16位數(shù)據(jù)總線)為ATA、UTOPIA、EPP、PCMCIA和DSP等提供了簡單和無縫連接接口。

CY7C68013結(jié)構(gòu)圖如圖10.4所示。FPGA與CY7C68013的電路連接關(guān)系可以參考本書2.2.11小節(jié)的內(nèi)容。

圖10.4CY7C68013FX2結(jié)構(gòu)示意圖

10.3.2FX2接口芯片的SlaveFIFO傳輸模式

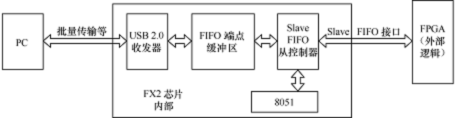

當(dāng)FPGA與FX2芯片相連時,只需要利用FX2作為一個USB 2.0數(shù)據(jù)通道來實現(xiàn)與主機的高速通信。FPGA能夠提供滿足Slave FIFO要求的傳輸時序,可以作為Slave FIFO主控制器。`

Slave FIFO傳輸?shù)氖疽鈭D如圖10.5所示。

圖10.5SlaveFIFO傳輸?shù)氖疽鈭D

在這種方式下,F(xiàn)X2內(nèi)嵌的8051固件的功能只是配置Slave FIFO相關(guān)的寄存器以及控制FX2何時工作在Slave FIFO模式下。一旦8051固件將相關(guān)的寄存器配置完畢,且使自身工作在Slave FIFO模式下后,F(xiàn)PGA就可按照Slave FIFO的傳輸時序,高速與主機進行通信,而在通信過程中不需要8051固件的參與。

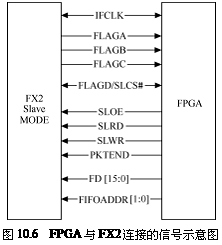

在Slave FIFO方式下,F(xiàn)PGA與FX2的連接信號圖如圖10.6所示。

下面是信號線的說明。

IFCLK:FX2輸出的時鐘,可作為通信的同步時鐘。

FLAGA、FLAGB、FLAGC、FLAGD:FX2輸出的FIFO狀態(tài)信息,如滿、空等。

SLCS:FIFO的片選信號,外部邏輯控制,當(dāng)SLCS輸出高時,不可進行數(shù)據(jù)傳輸。

SLOE:FIFO輸出使能,外部邏輯控制,當(dāng)SLOE無效時,數(shù)據(jù)線不輸出有效數(shù)據(jù)。

SLRD:FIFO讀信號,外部邏輯控制,同步讀時,F(xiàn)IFO指針在SLRD有效時的每個IFCLK的上升沿遞增,異步讀時,F(xiàn)IFO讀指針在SLRD的每個有效至無效的跳變沿時遞增。

SLWR:FIFO寫信號,外部邏輯控制,同步寫時,在SLWR有效時的每個IFCLK的上升沿時數(shù)據(jù)被寫入,F(xiàn)IFO指針遞增,異步寫時,在SLWR的每個有效至無效的跳變沿時數(shù)據(jù)被寫入,F(xiàn)IFO寫指針遞增。

PKTEND:包結(jié)束信號,外部邏輯控制,在正常情況下,外部邏輯向FX2的FIFO中寫數(shù),當(dāng)寫入FIFO端點的字節(jié)數(shù)等于FX2固件設(shè)定的包大小時,數(shù)據(jù)將自動被打成一包進行傳輸,但有時外部邏輯可能需要傳輸一個字節(jié)數(shù)小于FX2固件設(shè)定的包大小的包,這時,它只需在寫入一定數(shù)目的字節(jié)后,聲明此信號,此時FX2硬件不管外部邏輯寫入了多少字節(jié),都自動將之打成一包進行傳輸。

FD[15:0]:數(shù)據(jù)線。

FIFOADR[1:0]:選擇4個FIFO端點的地址線,外部邏輯控制。

10.3.3SlaveFIFO模式的典型操作時序

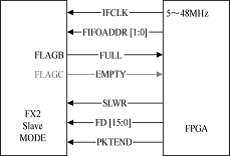

1.同步SlaveFIFO寫操作

同步Slave FIFO寫的標準連接圖如圖10.7所示。

同步Slave FIFO寫的標準時序如下。

· IDLE:當(dāng)寫事件發(fā)生時,進狀態(tài)1。

·狀態(tài)1:使FIFOADR[1:0]指向IN FIFO,進狀態(tài)2。

·狀態(tài)2:如FIFO滿,在當(dāng)前狀態(tài)等待,否則進狀態(tài)3。

·狀態(tài)3:驅(qū)動數(shù)據(jù)到數(shù)據(jù)線上,使SLWR有效,持續(xù)一個IFCLK周期,進狀態(tài)4。

·狀態(tài)4:如需傳輸更多的數(shù),進狀態(tài)2,否則進狀態(tài)IDLE。

狀態(tài)跳轉(zhuǎn)示意圖如圖10.8所示。

圖10.7同步SlaveFIFO寫的標準連接圖 圖10.8同步SlaveFIFO寫的標準時序

假定FX2設(shè)定包大小為512字節(jié),當(dāng)FPGA向FIFO端點中寫入的數(shù)據(jù)達512字節(jié)時,F(xiàn)X2硬件自動將已寫入的512字節(jié)打成一包準備進行傳輸。這個動作就和在普通傳輸中,F(xiàn)X2固件向FIFO端點中寫入512字節(jié)后,把512這個數(shù)寫入EPxBC中一樣,只不過這個過程是由硬件自動完成的。在這里可以看出“FX2固件不參與數(shù)據(jù)傳輸過程”的含義了。外部邏輯只需按上面的時序圖所示的時序向FIFO端點中一個一個字節(jié)(或字)地寫數(shù),寫到一定數(shù)量,F(xiàn)X2硬件自動將數(shù)據(jù)打包傳輸,這一切均不需固件的參與,由此實現(xiàn)高速數(shù)據(jù)傳輸。

2.同步SlaveFIFO讀操作

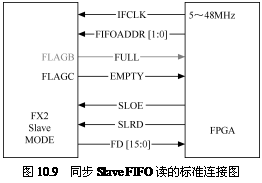

同步Slave FIFO讀的標準連接圖如圖10.9所示。

同步Slave FIFO讀的標準時序如下。

· IDLE:當(dāng)讀事件發(fā)生時,進狀態(tài)1。

·狀態(tài)1:使FIFOADR[1:0]指向OUT FIFO,進狀態(tài)2。

·狀態(tài)2:使SLOE有效,如FIFO空,在當(dāng)前狀態(tài)等待,否則進狀態(tài)3,

·狀態(tài)3:從數(shù)據(jù)線上讀數(shù),使SLRD有效,持續(xù)一個IFCLK周期,以遞增FIFO讀指針,進狀態(tài)4。

·狀態(tài)4:如需傳輸更多的數(shù),進狀態(tài)2,否則進狀態(tài)IDLE。

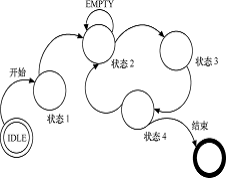

狀態(tài)跳轉(zhuǎn)示意圖如圖10.10所示。

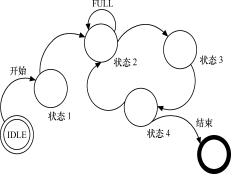

3.異步SlaveFIFO寫操作

異步Slave FIFO寫的標準連接圖如圖10.11所示。

圖10.10同步SlaveFIFO讀狀態(tài)跳轉(zhuǎn)示意圖 圖10.11異步SlaveFIFO寫的標準連接圖

異步Slave FIFO寫的標準時序如下。

· IDLE:當(dāng)寫事件發(fā)生時,進狀態(tài)1。

·狀態(tài)1:使FIFOADR[1:0]指向IN FIFO,進狀態(tài)2。

·狀態(tài)2:如FIFO滿,在當(dāng)前狀態(tài)等待,否則進狀態(tài)3。

·狀態(tài)3:驅(qū)動數(shù)據(jù)到數(shù)據(jù)線上,使SLWR有效,再無效,以使FIFO寫指針遞增,進狀態(tài)4。

·狀態(tài)4:如需傳輸更多的數(shù),進狀態(tài)2,否則進狀態(tài)IDLE。

狀態(tài)跳轉(zhuǎn)示意圖如圖10.12所示。

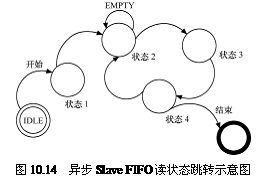

4.異步SlaveFIFO讀操作

異步Slave FIFO讀的標準連接如圖10.13所示。

圖10.12異步SlaveFIFO寫狀態(tài)跳轉(zhuǎn)示意圖圖10.13異步SlaveFIFO讀的標準連接圖

異步Slave FIFO讀的標準時序如下。

· IDLE:當(dāng)讀事件發(fā)生時,進狀態(tài)1。

·狀態(tài)1:使FIFOADR[1:0]指向OUT FIFO,進狀態(tài)2。

·狀態(tài)2:如FIFO空,在當(dāng)前狀態(tài)等待,否則進狀態(tài)3。

·狀態(tài)3:使SLOE有效,使SLRD有效,從數(shù)據(jù)線上讀數(shù),再使SLRD無效,以遞增FIFO讀指針,再使SLOE無效,進狀態(tài)4。

·狀態(tài)4:如需傳輸更多的數(shù),進狀態(tài)2,否則進狀態(tài)IDLE。

狀態(tài)跳轉(zhuǎn)示意圖如圖10.14所示。

10.3.4FX2的固件程序設(shè)計

在FX2芯片的固件程序設(shè)計中,最關(guān)鍵的就是系統(tǒng)初始化函數(shù)TD_Init(void),下面講解這個函數(shù)的部分代碼。

//時鐘設(shè)置

CPUCS=0x12;//48MHzCLKOUT輸出使能

IFCONFIG=0x43;//使用外部時鐘,IFCLK輸入不反向

SYNCDELAY;//同步延遲

EP2CFG=0xA0;//需要設(shè)定為4緩沖,每個緩沖區(qū)大小為512字節(jié)

SYNCDELAY;

EP4CFG=0x00;

SYNCDELAY;

EP6CFG=0xE0;

SYNCDELAY;

EP8CFG=0x00;

SYNCDELAY;

FIFORESET=0x80;//激活NAK-ALL避免競爭

SYNCDELAY;

FIFORESET=0x02;//復(fù)位FIFO2

SYNCDELAY;

FIFORESET=0x06;//復(fù)位FIFO6

SYNCDELAY;

FIFORESET=0x00;//取消激活NAK-ALL

SYNCDELAY;

PINFLAGSAB=0xE6;//FLAGA設(shè)定為EP6PF,FLAGB設(shè)定為EP6FF

SYNCDELAY;

PINFLAGSCD=0xf8;//FLAGC設(shè)定為EP2EF,FLAGD保留

SYNCDELAY;

PORTACFG|=0x00;//SLCS有效

SYNCDELAY;

FIFOPINPOLAR=0x00;//所有信號低電平有效

SYNCDELAY;

10.3.5USB2.0接口的典型應(yīng)用

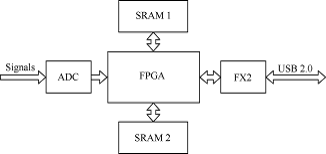

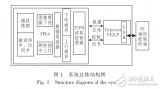

由于USB 2.0接口的數(shù)據(jù)傳輸速度快,而且使用方便,因此被廣泛應(yīng)用于各種便攜設(shè)備中。例如,基于USB 2.0接口的數(shù)據(jù)采集終端,可以將各種類型的數(shù)據(jù)采集到電腦主機中進行處理和結(jié)果顯示,其典型的結(jié)構(gòu)如圖10.15所示。

圖10.15基于USB2.0接口的數(shù)據(jù)采集終端結(jié)構(gòu)框圖

-

FPGA

+關(guān)注

關(guān)注

1629文章

21748瀏覽量

603795 -

usb

+關(guān)注

關(guān)注

60文章

7950瀏覽量

264858 -

通信接口

+關(guān)注

關(guān)注

3文章

239瀏覽量

30999

原文標題:利用FPGA實現(xiàn)USB 2.0通信接口

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設(shè)計論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

高云半導(dǎo)體宣布發(fā)布USB 2.0接口解決方案

FPGA應(yīng)用開發(fā)入門與典型實例pdf免費下載(華清遠見編寫)

基于Verilog的FPGA與USB 2.0高速接口設(shè)計

基于USB接口技術(shù)的無線通信設(shè)計與實現(xiàn)

基于USB2.0的數(shù)據(jù)傳輸接口轉(zhuǎn)換系統(tǒng)

基于FPGA的USB2.0控制器設(shè)計

IR-UWB通信系統(tǒng)高速USB接口的設(shè)計與實現(xiàn)

FPGA的嵌入式系統(tǒng)USB接口設(shè)計

基于USB2.0芯片CY7C68013的高速數(shù)據(jù)通信接口設(shè)計

基于FPGA NANO2開發(fā)板實現(xiàn)USB2.0接口通信的設(shè)計方案

基于Verilog的FPGA與USB 2.0高速接口設(shè)計資料下載

利用FPGA實現(xiàn)USB 2.0通信接口

利用FPGA實現(xiàn)USB 2.0通信接口

評論