TSV 三維封裝技術特點鮮明、性能好、前景廣闊, 是未來發展方向,但是 TSV 堆疊芯片這種結構和工 藝復雜性的提高,為三維封裝的可靠性控制帶來了 挑戰。主要體現在以下 4 個方面 :(1) TSV 孔質量和 信賴性保證難度大 ;(2) 多層芯片堆疊結構的機械穩 定性控制難度大 ;(3) 芯片間熱管理和散熱解決方案 復雜 ;(4) 芯片測試和故障隔離、定位困難。

2.1 TSV 孔的質量和可靠性問題

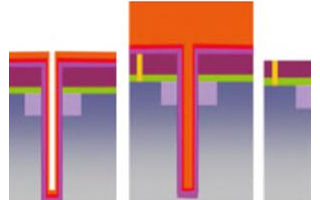

作為三維集成電路中的垂直互連通道,TSV 孔 的質量和可靠性對系統性能至關重要。隨著集成度 的不斷提升,TSV 孔的關鍵尺寸正在向著超高縱橫 比 ( 深寬比大于 20:1) 和微米級甚至亞微米級孔徑 ( 小 于 10μm) 發展。這給 TSV 孔的制造工藝帶來了巨 大挑戰。當前 TSV 孔存在的主要質量與可靠性問題 集中在以下 4 個方面。

(1)TSV 孔的形狀和側壁角度難以精確控制 ;

(2) 絕緣層與阻擋層的保形性與界面粘附力難以保證 ;

(3)TSV 孔內部難以實現無空洞的充填 ;

(4)TSV 周邊多余的填充材料難以清除。

TSV 孔存在的上述工藝缺陷會導致其在后續操 作和使用中出現兩大類可靠性問題 :

(1)TSV 的絕緣層不連續或有缺陷,會使 TSV導體與芯片的體硅之間發生漏電,或者 TSV 和地之間的短路可能會導致功能異常。

(2)TSV 通孔中或連接通孔導電材料存在空洞, 空洞可以隨著時間推移而增長,從而導致開路。

這兩類故障機制削弱了 TSV 的導電可靠性 , 是 影響三維集成電路可靠性的主要因素,也是當前研 究的重點難題。

2.2 三維堆疊過程中的質量問題

TSV 堆疊芯片在進行三維封裝制造過程中,一 般包括多個物理平面間互連堆疊起來工藝,這一堆 疊的過程可以由晶圓—晶圓 (Wafer to Wafer,W2W)、 芯片—晶圓 (Die to Wafer,D2W) 或芯片—芯片 (Die to Die,D2D) 等方式實現,制造過程比傳統 2D 封裝 的集成電路復雜,也更容易產生缺陷和失效。當前 的質量問題主要有以下 5 個方面。

(1) 電應力問題 :TSV 實質是穿過硅襯底的金屬 線 ( 一般采用 Cu),其周圍需要采用隔離介質 ( 一般 采用 SiO2) 防止 Cu 離子向硅芯片擴散。但這就形成 了金屬—氧化物—半導體 (MOS) 結構。這個 MOS 結構電容會導致 :TSV 信號通過耦合的形式干擾周圍器件,產生信號失真 ;MOS 電容通道中的漏電流 增加,提高了芯片的靜態功耗。

(2) 熱應力問題 :在 TSV 制作過程中,首先需 要在硅晶圓上刻蝕窄而深的孔,然后填充上隔離材 料,最后電鍍 Cu。TSV 和硅片經多次熱循環,最 后的退火和冷卻過程會給整個結構帶來巨大的溫差 (250 ℃ )。由于金屬材料尤其是銅 (Cu) 和硅片熱膨 脹系數 (CTE) 的不匹配,會在 TSV 周圍的硅襯底內 引入很大的熱應力,從而影響熱載流子遷移率、器 件性能以及長期可靠性。

(3) 機械應力問題 :TSV 是使芯片疊層連接到其 他疊層和單元。所有這些界面可能來自不同的芯片, 在鍵合過程中,機械應力的存在使芯片間界面開裂 或 TSV 垂直互連處鍵合材料的失效,封裝結構的機 械穩定性降低,從而導致 TSV 堆疊芯片的短路或開 路失效。

(4) 熱管理問題 :TSV 三維集成電路通過垂直堆 疊,極大地提高了單位面積的芯片密度,這導致相 比二維集成電路,三維集成電路中的熱密度急劇增 加。疊加使用的垂直鍵合材料本身熱導率低 , 難以進 行有效的熱傳遞,尤其是距離散熱器最遠的頂層芯 片存在嚴重的熱累積問題,熱密度過高會導致芯片 性能衰減、加速老化以及潛在的永久失效。

(5) 電性能測試問題 :在 TSV 三維堆疊封裝結 構中 , 多個芯片被垂直堆疊和互連,這使得確保每個 芯片的電性能符合規范,以及測試最終堆疊后芯片 的整體電性能變得非常具有挑戰。主要的測試難點 包括 :堆疊前各個裸片的測試重復性與可靠性較差 ;堆疊芯片后信號無法直接進行探針測試 ;故障的定 位與隔離難度大。

目前國際上有 JEDEC 于 2009 年發布的 JEP 158— 2009 “3D chip stack with through-silicon vias(TSVS) :Identitying,evaluating and understanding reliability interactions ”(《硅通孔 3D 堆疊芯片 可靠性的相互 作用的識別、評估和理解》),專門針對 TSV 三維封 裝的可靠性評估與保障。

該標準提出根據 TSV 三維堆疊芯片產品、工藝 的實際情況,由 TSV 三維堆疊芯片生產商編制試驗 方案,確定采用的試驗方法、試驗條件、抽樣數、 失效判據以及需關注的特定失效模式。

對 TSV 三維封裝進行可靠性驗證試驗時,可以 采用專門設計的試驗結構或直接使用產品級 TSV 堆 疊芯片。與產品級芯片相比,精心設計的試驗結構 在進行失效檢測和分析時具有明顯的優勢 :試驗結 構通過精確控制敏感區域,可以有效放大某一失效 機制的特征 ;試驗結構針對特定缺陷設計相應的傳 感與監測機制,可以實現目標的實時檢測 ;試驗失 敗后,可以通過預埋的分析單元讓失效部位得以快 速準確地定位和分類。

相比之下,在產品級芯片的電參數測試中檢測 出異常情況,要準確定位與識別 TSV 相關的故障機 制幾乎是不可能的。因此,合理設計的 TSV 專用試 驗結構,將大大提高工藝流程中缺陷檢測效率與質 量提升速度,是開發與驗證 TSV 制程的重要手段。

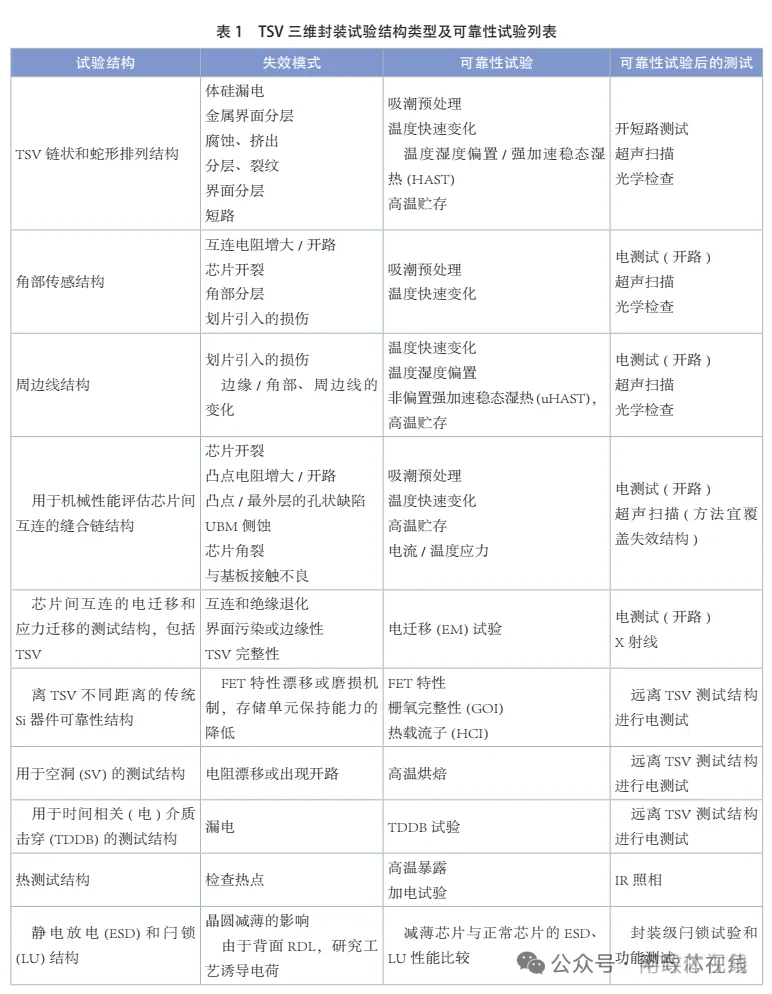

根據 TSV 堆疊芯片工藝中失效模式,JEP 158— 2009 給出了可靠性應力以及推薦的檢測方法,見下表。

為了有針對性地檢測 TSV 三維封裝的故障模 式 , 可以設計特定的試驗結構 ( 見表 1) 進行可靠性驗證試驗。這些試驗結構通過精心布局,可以放大 某一故障機制的特征。例如,鏈狀或蛇形的 TSV 結 構,可以用于檢測“體硅漏電”“金屬界面分層”等 電遷移故障。對專門設計的試驗結構進行吸潮預處 理、溫度快速變化、溫度濕度偏置 / 強加速穩態濕熱 (HAST)、高溫貯存等試驗,完成后再進行開短路測試、 超聲掃描、光學檢查,檢查導電性能的損傷,結構 內部的空洞缺陷以及界面的分層或裂紋。通過電學 測試與物理分析的結合,可以明確對應特定可靠性 試驗后,TSV 結構中的缺陷類型、位置、失效機制等, 從而對工藝過程進行優化。

通過這種針對性的可靠性驗證方案,讓企業充 分考量并驗證 TSV 三維封裝產品中的潛在故障機制、 故障模式,是保證產品質量的有效手段。JEP 158— 2009 標準的制定可以幫助制造商和用戶更好地了解 TSV 技術的可靠性和相互作用,改善 TSV 技術的可 靠性和穩定性,推動了三維封裝技術的工業化進程 與風險控制,該標準對于 TSV 三維堆疊芯片的制造 和應用具有重要的指導意義。

但是 JEP 158—2009 也有局限性,如 :沒有給出 明確的可靠性試驗類型選取參考 ;缺乏針對不同故 障機制的標準化試驗條件推薦 ;未規定明確的判定 試驗結構失效的量化標準。

這些內容的缺失會導致不同 TSV 堆疊芯片生產 企業,在確立可靠性驗證方案時存在明顯差異 :采用 的試驗類型及嚴苛條件可能不同 ;判定試驗結構失 效的界限不一致。因此,這將導致不同廠商的 TSV 產品可靠性水平與工藝成熟度難以在行業內實現 統一。

-

芯片

+關注

關注

456文章

50884瀏覽量

424154 -

堆疊

+關注

關注

0文章

35瀏覽量

16603 -

TSV

+關注

關注

4文章

113瀏覽量

81484

原文標題:TSV 三維堆疊芯片的可靠性問題

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

三維測量在醫療領域的應用

三維測量技術在工業中的應用

三維掃描與建模的區別 三維掃描在工業中的應用

流場調控導熱微結構取向:三維堆疊芯片高效散熱新方案

三維堆疊封裝新突破:混合鍵合技術揭秘!

硅通孔三維互連與集成技術

友思特方案 基于三維點云實現PCB裝配螺絲視覺檢測

起點,經過點,終點,三點xyz,畫三維圓弧。

泰來三維|數字化工廠_煤礦三維掃描數字化解決方案

泰來三維|三維掃描服務_三維掃描助力園區改造公園

三維掃描服務項目-工廠三維掃描建模

泰來三維|文物三維掃描,文物三維模型怎樣制作

TSV與異構集成技術的前沿進展與趨勢展望

TSV三維堆疊芯片的可靠性問題

TSV三維堆疊芯片的可靠性問題

評論