本文是意法半導體公司發布的關于其微控制器 EMC 設計指南的應用筆記,主要介紹了 EMC 相關定義、意法半導體微控制器的 EMC 特性、設計策略、應用的 EMC 指南以及結論等內容,旨在幫助應用設計者獲得最佳 EMC 性能。

文檔下載:ST微控制器EMC設計指南

*附件:an1709-emc-design-guide-for-stm8-stm32-and-legacy-mcus-stmicroelectronics.pdf

1. EMC 定義

- EMC :系統在電磁干擾下正常工作且不干擾其他設備的能力。

- EMS :器件對電氣干擾和傳導電氣噪聲的耐受能力,通過 ESD 和 FTB 測試衡量。

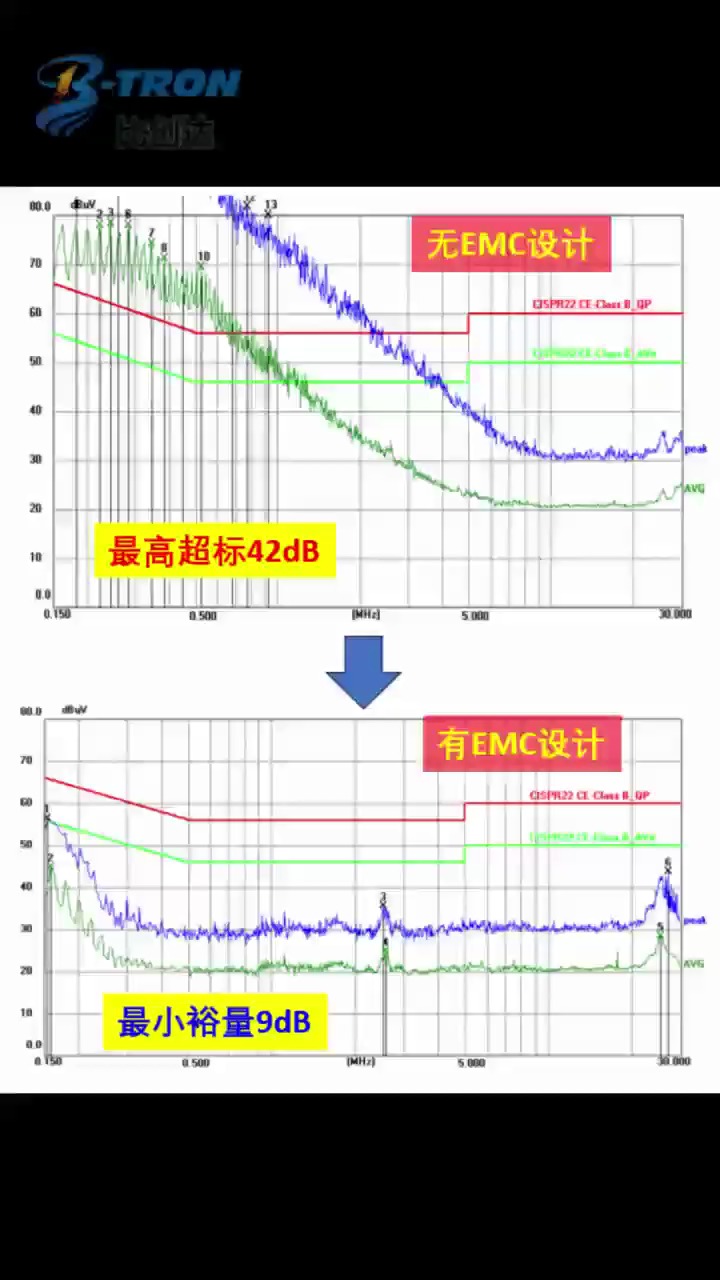

- EMI :設備產生的傳導或輻射電氣噪聲水平,包括傳導發射和輻射發射。

2. 意法半導體微控制器的 EMC 特性

- 電磁敏感性(EMS)

- 功能性 EMS 測試

- 功能性靜電放電測試(F_ESD 測試) :對新微控制器每個引腳進行正極或負極單次放電測試,使用符合 IEC 61000 - 4 - 2 標準的 NSG 435 發生器,依據表 1 標準參考。

- 快速瞬變脈沖群測試 :通過電容耦合網絡對微控制器電源線施加干擾,符合表 2 中 EN61000 - 4 - 4 / IEC 61000 - 4 - 4 標準,尖峰頻率 5kHz,每 300ms 產生持續 15ms 突發尖峰(75 個尖峰)。

- 嚴重性級別和類別 :根據測試電壓與 IEC 標準關系定義,如 ESD(IEC 61000 - 4 - 2)和 FTB(IEC 61000 - 4 - 4)測試電壓對應不同嚴重性級別,同時根據 EN 50082 - 2 標準將 ESD 干擾下 MCU 行為分為 A、B、C、D 類,依據可接受限值和目標級別判斷器件性能,相關信息在數據手冊中按表 5、6 格式呈現。

- 門鎖(LU)

- 絕對電氣敏感性 :評估元件對 ESD 導致破壞的耐受能力,使用自動 ESD 測試儀按標準(如 JESD22 - A114A/A115A)對引腳組合放電,樣本大小與供電引腳數目有關,模擬人體模型(HBM)和充電器件模型(CDM),測試后在生產測試儀上確認參數符合數據手冊。

- 功能性 EMS 測試

- 電磁干擾(EMI)

3. ST MCU 設計策略和 EMC 特性

- 敏感性

- 發射

4. 基于 MCU 的應用的 EMC 指南

- 硬件

- ESD 保護的處理預防措施 :參考應用筆記 AN1181 獲取詳細程序。

- 固件 :參考 ST 網站專用應用筆記 AN1015。

- EMC 相關機構的網站鏈接 :提供 FCC、EIA、SAE、IEC、CENELEC、JEDEC 等機構網站鏈接。

5. 結論

開發微控制器應用時應盡早考慮 EMC 要求,ST 微控制器數據手冊信息有助于選擇元件,需采取硬件和固件預防措施優化 EMC 和系統穩定性。

6. EMC設計策略進行詳細的整理和總結

意法半導體微控制器的 EMC 設計策略涵蓋敏感性和發射兩個方面,旨在提高微控制器在電磁環境中的穩定性和可靠性,同時降低其對其他設備的電磁干擾。以下是對這些策略的詳細整理和總結:

敏感性設計策略

- 欠壓復位(BOR)

- 功能與原理 :確保微控制器始終在安全工作區內運行。當 VDD 低于最低工作 VDD 時,微控制器可能無法正常工作,而 BOR 電路在 VDD 低于特定閾值(VIT + 或 VIT - )時,會使微控制器進入復位狀態,以防止不可預測行為。例如,當 VDD 上升時,低于 VIT + 時產生復位;當 VDD 下降時,低于 VIT 時產生復位。

- 遲滯特性 :設有多個遲滯級別,避免微控制器重啟時發生振蕩。這有助于穩定微控制器的復位過程,確保其在電源波動時能正確響應。

- 配置方式 :電壓閾值可通過選項字節配置為低、中或高,以適應不同應用需求。

- 復位引腳狀態 :在欠壓復位期間,NRST 引腳保持低電平,允許 MCU 復位其他器件,同時也為外部復位電路提供了一種控制手段。

- 優勢與應用場景 :BOR 功能使 MCU 在面對電源干擾時更加穩健,適用于對穩定性要求較高的應用場景,且在一定程度上可減少外部復位硬件的需求。

- 可編程電壓檢測器(PVD)

- 功能概述 :在電源受到外部噪聲干擾時,提前預警并采取相應措施,確保微控制器行為安全,從而提升 EMS 性能。

- 閾值與預警機制 :PVD 閾值高于 BOR 值約 200mV,當 VDD 達到 PVD 閾值時,會生成中斷,通知應用軟件采取操作,如準備關閉應用或執行其他安全措施,直到電源恢復正常。

- 中斷特性 :PVD 比較器輸出通過實時狀態位(PVDO)供應用軟件讀取,該位只讀。中斷的產生與電壓上升時間(trv)有關,若 trv 不足特定 CPU 周期數,在達到 VIT+(PVD) 時可能不生成中斷;若 trv 足夠長,根據 PVD 中斷使能的時機,可能收到一個或兩個中斷。

- 與 BOR 的協同工作 :與 BOR 協同工作,在電源波動時提供更精細的控制和保護,避免微控制器因電源問題出現異常。

- I/O 功能和屬性

- 靜電放電和閂鎖防護

- 保護接口設計

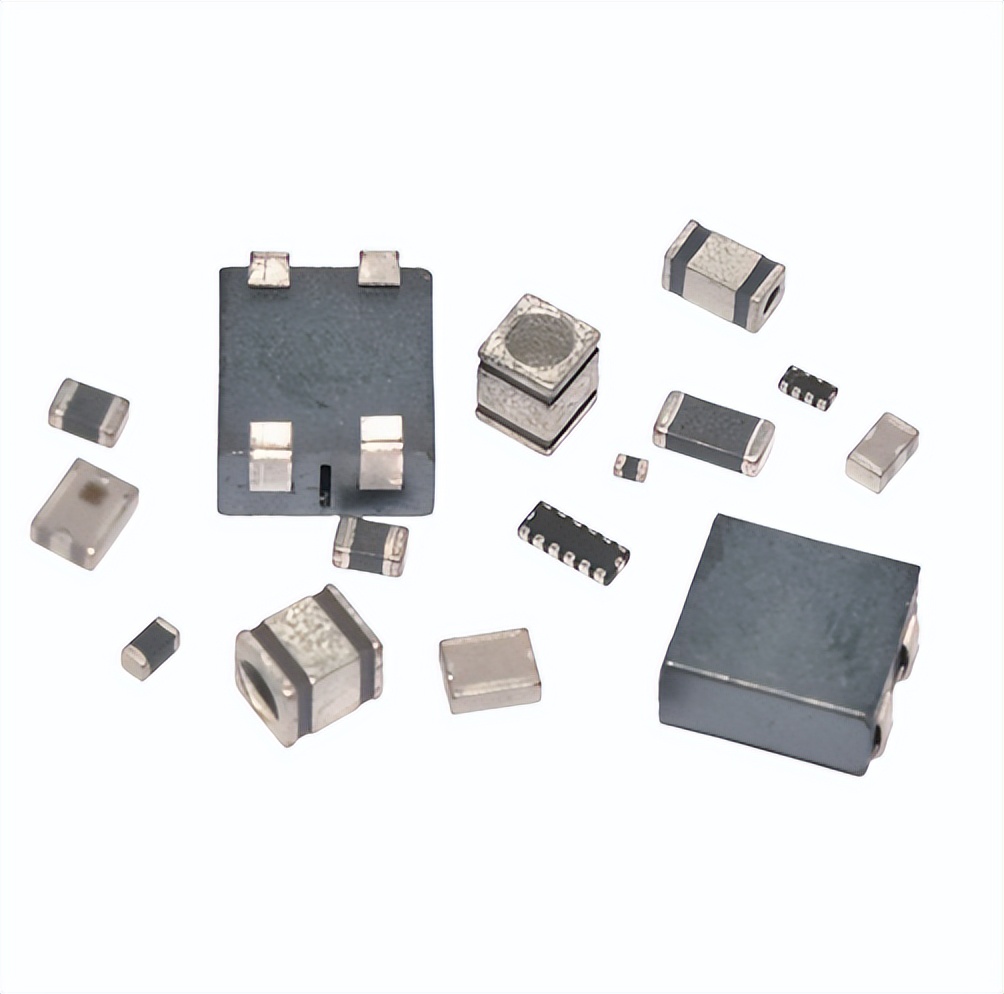

- 硬件解決方案 :盡管 ST 微控制器輸入 / 輸出電路已考慮 ESD 和閂鎖問題,但在引腳暴露于非法電壓和高電流注入的應用中,建議用戶采用低通濾波器和鉗位二極管等硬件解決方案,防止過載損壞。

- 不同輸出配置下的注意事項

- 推挽輸出 :數字 I/O 引腳電路包含標準輸入緩沖區和推挽配置的輸出緩沖區,輸出緩沖區 MOS 晶體管的二極管結構在非法電壓條件下可能影響引腳行為,同時附加的 ESD 保護電路用于保護邏輯電路,但需注意其在正常工作模式下的影響。

- 開漏輸出 :某些 I/O 引腳可設置為開漏輸出,此時需注意外部線路電壓高于 VDD 時可能通過二極管注入電流損壞器件,且在多引腳連接同一點時,應合理配置輸出以避免電流爭用。

- 模擬輸入引腳保護 :模擬輸入引腳內部電路包含數字 I/O 和模擬復用器,復用器晶體管受電源影響,需確保模擬電源和數字電源輸入電壓值正常,避免意外電流注入導致器件損毀。

發射設計策略

- 內部 PLL

- 時鐘生成與優化 :部分微控制器內置可編程 PLL 時鐘生成器,可使用標準 3 - 25MHz 晶振獲取多種內部頻率(最高幾百 MHz),使微控制器能在使用中等頻率晶振的同時,獲得高頻率內部時鐘以提升系統性能。

- 噪聲減少機制 :高頻時鐘源集成在芯片內部,減少了 PCB 走線和外部元件帶來的潛在噪聲發射,同時 PLL 網絡對 CPU 時鐘濾波,可抵御外部短時脈沖波干擾。

- 通用低功耗方法

- 低功耗振蕩器選擇

- 外部源 :使用外部時鐘源時,需用占空比約 50% 的時鐘信號(方波、正弦波或三角波)驅動 OSC1 引腳,OSC2 引腳接地。

- 晶振 / 陶瓷振蕩器 :優點是主時鐘精度高,通過選項字節選擇不同頻率范圍的振蕩器,且諧振器和負載電容應靠近振蕩器引腳以減小失真和穩定時間,在復位階段不停止,以避免啟動延遲。

- 內部 RC 振蕩器 :經濟高效但頻率精度較低,處于個位數低 MHz 范圍,兩個振蕩器引腳接地,不同批次間存在工藝變化差異,部分微控制器有工藝補償(可調內部 RC)可將精度提高到 1%。

- 內部調壓器(適用低功耗內核 MCU)

- 供電電壓調節 :從外部電源為內核供電,降低 CPU 供電電壓,減少內核帶來的 EMI。

- 電源隔離 :將 CPU 供電與 MCU 外部供電隔離開,進一步降低電磁干擾。

- 低功耗振蕩器選擇

- 輸出 I/O 電流限制和邊沿時間控制 :內置輸出緩沖區,通過控制切換速度,在噪聲和速度之間實現平衡,避免切換時產生寄生振蕩,從而減少電磁發射。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

emc

+關注

關注

170文章

3927瀏覽量

183291

發布評論請先 登錄

相關推薦

單板設計中的EMC優化策略

1板級EMC設計Openclasses成都9月20-21日隨著電子信息的發展,產品的EMC要求不斷提升。然而,70%的企業未設專職EMC人員,EMC設計多依賴研發人員經驗和“測試修補法

EMC濾波器:原理、應用及選型指南?|深圳比創達電子EMC.

EMC濾波器:原理、應用及選型指南?|深圳比創達電子EMC隨著電子設備的不斷普及和電磁環境的復雜化,電磁兼容性(EMC)問題日益凸顯。在電子設備中,

發表于 03-18 10:34

EMC濾波器:原理、應用與選型指南?|深圳比創達電子EMC a

景和選型指南等方面進行詳細介紹。接下來就跟著深圳比創達電子EMC小編一起來看下吧!一、EMC濾波器的基本原理EMC濾波器是一種用于抑制電磁干擾的器件,其工作原理主要包括:1、濾波器分類

發表于 03-04 10:49

高功率PCB中EMC的處理與優化策略

在高功率PCB設計中,電磁兼容性(EMC)是一個關鍵問題,它涉及到保證電子設備在各種環境下正常運作,不受電磁干擾(EMI)的影響,同時也不對其他設備產生干擾。本文將從一個全面的視角探討高功率PCB中EMC的處理與優化策略,提供實

ST MCU的 EMC 特性、設計策略、應用的 EMC設計指南

ST MCU的 EMC 特性、設計策略、應用的 EMC設計指南

評論