后段刻蝕工藝(Back-End of Line ETCH,簡稱BEOL ETCH)作為集成電路制造的重要環節,其復雜性與重要性毋庸置疑。

什么是BEOL ETCH

BEOL是指從金屬互連開始的晶圓制造階段,主要包括金屬布線、鈍化層沉積及相關圖形刻蝕。BEOL ETCH是針對這些材料和結構的精確圖形化過程,用以實現導線、過孔(Via)等功能結構。

可以將集成電路制造比作建造城市,BEOL ETCH就像是鋪設城市的地下管網——不僅要規劃出清晰的路徑,還要精準挖掘、避免損壞其他區域,同時確保管網的耐用性。

核心任務

1. 圖形定義:通過光刻定義出的圖案轉移到金屬或介質層上,形成互連結構和電極通道。常見刻蝕對象包括:金屬(如銅、鋁)、介質層(如SiO?、Low-k材料)等。

2. 選擇性刻蝕:在保持保護層或底層完整的情況下,移除目標材料,達到圖形分離的目的。

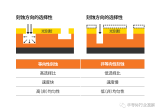

3. 尺寸與形貌控制:確保關鍵尺寸(Critical Dimension, CD)的精確度,同時保持側壁形貌(如垂直度或傾斜度)的設計要求。

4. 與前后工藝匹配:BEOL刻蝕需與前段光刻及后續金屬沉積完美銜接,避免缺陷引發的產能損失或性能退化。

工藝流程

BEOL刻蝕通常涉及多層次結構,以下為其基本步驟:

1. 圖形轉移:光刻后將掩膜圖案傳遞到底層,通過刻蝕將保護層之下的材料按設計移除。

2. 主刻(Main Etch):移除大部分目標材料,快速形成圖案的大致輪廓。這一階段要求刻蝕速率高、選擇性好。

3. 精刻(Over Etch):針對邊角或復雜結構進行修整,確保結構完整性及尺寸一致性。這一階段對控制刻蝕終點(End-Point Detection, EPD)提出更高要求。

4. 清洗(Post Etch Cleaning):刻蝕后清除殘留物(如聚合物、顆粒等),防止缺陷傳播。

關鍵技術解析

1. 材料特性與刻蝕化學

BEOL涉及多種材料,其刻蝕原理多樣:

金屬材料:如銅、鋁,需通過化學反應生成易揮發的產物。

介質材料:如SiO?,通過離子轟擊結合化學反應去除。

2. 設備與工藝控制

等離子體生成:通過RF功率激發反應氣體形成活性離子。

Recipe優化:根據不同材料和結構,調整氣體比例、功率、壓力等參數。

3. 端點檢測(EPD)

通過光學信號、放電特性監測刻蝕進展,確保終點的精準控制。EPD在多層刻蝕中尤為重要,可避免過刻蝕或不足刻蝕。

4. 良率與缺陷控制

關鍵尺寸偏差:通過在線SPC(Statistical Process Control)工具實時監測。

缺陷修復:如使用PR rework進行光刻殘膠去除優化。

常見挑戰與應對策略

1. 復雜多層結構

挑戰:深溝槽刻蝕(如DTI,深度范圍1.5μm-4μm)易導致側壁塌陷或不均勻性。

應對:調整氣體流量及功率分布,優化多次刻蝕策略。

2. 新材料引入

挑戰:低介電常數(Low-k)材料刻蝕易損壞,影響電性能。

應對:采用溫和刻蝕配方,并結合低溫工藝。

3. 高精度需求

挑戰:在40nm及以下工藝節點上,CD控制誤差可能帶來器件性能劣化。

應對:結合先進的RMS(Recipe Management System)和SPC系統進行動態調參。

優化與未來趨勢

1. 機器學習與智能控制:通過大數據分析與機器學習優化刻蝕參數,實現自適應調控,提升產線穩定性。

2. 新設備與技術引入:下一代等離子體源(如ICP)將進一步提升刻蝕均勻性和深寬比控制能力。

3. 工藝協同開發:與客戶、供應商協同優化產品設計和制造工藝,降低生產成本并加快產品導入。

BEOL ETCH是一門將物理化學與精密制造結合的藝術。它不僅需要對材料特性和設備原理的深刻理解,還要具備系統化思維和問題解決能力。

-

集成電路

+關注

關注

5388文章

11559瀏覽量

361986 -

刻蝕工藝

+關注

關注

2文章

38瀏覽量

8433

原文標題:后段刻蝕工藝(BEOL ETCH)詳解

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

芯片制造的刻蝕工藝科普

【新加坡】知名半導體晶圓代工廠招聘資深刻蝕工藝工程師和刻蝕設備主管!

干法刻蝕和清洗(Dry Etch and Cleaning)

濕法刻蝕和清洗(Wet Etch and Cleaning)

一文解讀DRAM的9大刻蝕技術

后段集成工藝(BEOL Integration Flow)- 2

一文詳解CMP設備和材料

cmp是什么意思 cmp工藝原理

等離子刻蝕工藝技術基本介紹

大馬士革銅互連工藝詳解

后段刻蝕工藝(BEOL ETCH)詳解

后段刻蝕工藝(BEOL ETCH)詳解

評論