季豐電子材料分析實(shí)驗(yàn)室配備賽默飛Talos F200i,設(shè)備選配有Epsilon應(yīng)力分析系統(tǒng),配合精準(zhǔn)的TEM樣品制備技術(shù)、納米電子衍射收集參數(shù)優(yōu)化和數(shù)據(jù)處理方法優(yōu)化,可快速實(shí)現(xiàn)納米尺度的應(yīng)變分析。

季豐電子在總部上海、北京、深圳都建有專業(yè)的材料分析實(shí)驗(yàn)室,歡迎大家咨詢、委案!

芯片器件中的應(yīng)力

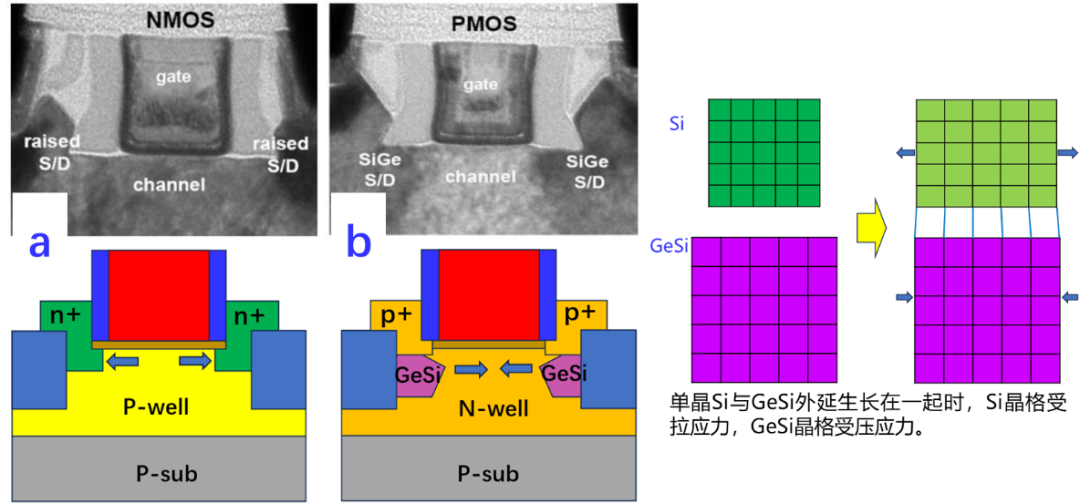

早在20世紀(jì)50年代人們就發(fā)現(xiàn)在應(yīng)變對(duì)i本征載流子遷移率影響,隨后在20世紀(jì)80年代應(yīng)變Si技術(shù)不斷被應(yīng)用于芯片性能改善。應(yīng)變 Si技術(shù)是指通過(guò)在傳統(tǒng)單晶硅襯度中加入應(yīng)變材料產(chǎn)生應(yīng)力,并把應(yīng)力引向器件的溝道,改變溝道中Si的導(dǎo)帶或者價(jià)帶的能帶結(jié)構(gòu),通過(guò)合理的器件設(shè)計(jì)來(lái)獲得合適的應(yīng)力方向從而減小能帶谷內(nèi)、谷間散射的概率以及載流子(電子和空穴)在溝道方向上的有效質(zhì)量,達(dá)到提高載流子遷移率和提高器件速度的目的。

應(yīng)變Si技術(shù)主要包括全局應(yīng)變硅(GeSi)和局部應(yīng)變硅技術(shù)(GeSi/CoSix/NiSix/TiSix/SiN等)。全局應(yīng)變硅技術(shù)利用Si與SiGex材料具有不同的晶格常數(shù),在晶格常數(shù)較大的弛豫Si如島虛擬襯底上外延生長(zhǎng)一薄層Si,得到具有平面雙軸張應(yīng)力的全局應(yīng)變Si,從而提高PMOS和NMOS載流子遷移率。局部應(yīng)變Si技術(shù)是指在器件某局部區(qū)域引入應(yīng)力,或只在對(duì)器件性能起主要作用的溝道位置引入應(yīng)變,且可調(diào)整所引入得應(yīng)變類型。

隨著制程減小帶來(lái)的器件溝道長(zhǎng)度的減小,局部硅產(chǎn)生的應(yīng)力大小逐漸增加到可與全局應(yīng)變量相比擬。2002年英特爾公司首次將局部外延嵌入SiGe技術(shù)應(yīng)用于CMOS工藝制程(90 nm)技術(shù)中,并由整個(gè)業(yè)界沿用至今。在 Si NMOSFET 器件中,SiC 是常見(jiàn)的應(yīng)變材料, SiC 的晶格常數(shù)遠(yuǎn)小于Si,作為外延的源漏區(qū)時(shí),可以對(duì)橫向的溝道產(chǎn)生單軸張應(yīng)力。

溝道制造在沿[100]晶向上的NMOSFET器件,其溝道方向的電子電導(dǎo)有效質(zhì)量和散射概率就會(huì)降低,電子遷移率增大,從而提高了N-MOSFET器件的性能。而在 Si PMOSFET器件中,通常會(huì)嵌入 GeSi 的源漏,GeSi 的晶格常數(shù)大于 Si,對(duì)橫向的溝道會(huì)產(chǎn)生壓應(yīng)力,溝道制造在沿[110]晶向上的PMOSFET器件會(huì)降低其溝道方向的空穴的電導(dǎo)有效質(zhì)量,空穴遷移率增大,從而提高了PMOSFET器件的性能。

▲圖一

(a) N-MOSFET器件的源極和漏極嵌入 SiC應(yīng)變材料和(b) P-MOSFET器件的源極和漏極嵌入GeSi應(yīng)變材料后產(chǎn)生的應(yīng)力方向。

芯片應(yīng)變表征方法

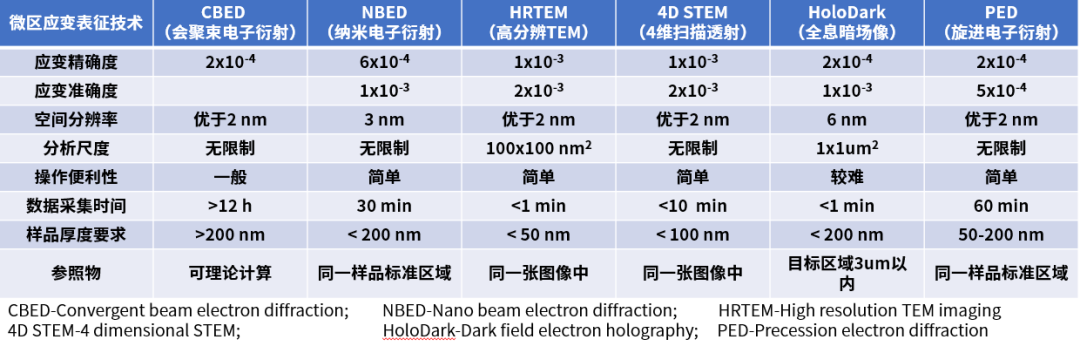

目前絕大多數(shù)芯片中的器件尺寸都小于1 um,最小可到納米級(jí)別,而透射電子顯微鏡(TEM)的空間分辨率可達(dá)0.1 nm,是芯片器件中應(yīng)變表征的首選工具,其他技術(shù)如拉曼、XRD等由于空間分辨率限制,無(wú)法用于芯片器件中的應(yīng)變表征。TEM中的應(yīng)力表征技術(shù)有CBED、NBED、HRTEM、4D STEM、Holography、PED等,這些技術(shù)在進(jìn)行微區(qū)應(yīng)變測(cè)試時(shí)的技術(shù)特點(diǎn)和優(yōu)缺點(diǎn)如下表所示[1]。

▲表一 TEM中不同應(yīng)變分析技術(shù)對(duì)比

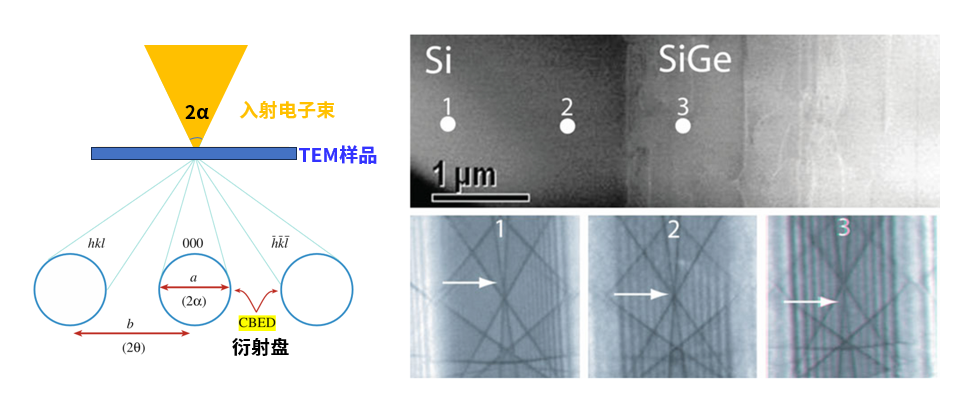

會(huì)聚束衍射(CBED)是最早用于應(yīng)力測(cè)試的技術(shù),當(dāng)入射電子束會(huì)聚角足夠大時(shí)會(huì)在衍射平面產(chǎn)生許多高階勞厄帶,這些HOLZ線的定位對(duì)材料的晶格參數(shù)非常敏感,可以用來(lái)高精度地測(cè)量應(yīng)變,正常晶格的HOLZ線非常銳利,而存在缺陷或者應(yīng)變區(qū)域的晶格的HOLZ線會(huì)變寬,對(duì)于銳利HOLZ 線,可以通過(guò)半動(dòng)力學(xué)計(jì)算直接根據(jù)Hough變換確定的HOLZ線位置來(lái)得到晶胞參數(shù),而對(duì)于寬 HOLZ 線,可通過(guò)復(fù)雜的擬合過(guò)程確定局部晶格參數(shù),某些對(duì)稱情況下,亦可通過(guò)對(duì)實(shí)驗(yàn)和動(dòng)力學(xué)模擬的 HOLZ 線圖案的兩個(gè)霍夫變換進(jìn)行擬合,也可以使用耦合動(dòng)力學(xué)模擬和有限元模擬通過(guò)試錯(cuò)來(lái)擬合產(chǎn)生應(yīng)變的界面應(yīng)力場(chǎng)。

▲圖二

左:CBED形成示意圖;右:Si-SiGe界面1-2-3三個(gè)區(qū)域的CBED衍射花樣對(duì)比,可見(jiàn)HOLZ的位置逐漸變化,且線逐漸變寬。[2]

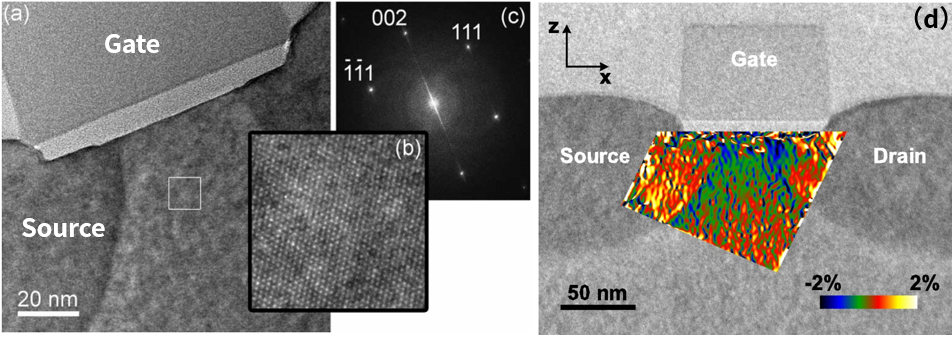

高分辨透射電子顯微像(HRTEM)是一種相位襯度像,它是利用平行電子束照射感興趣的單晶區(qū)域會(huì)在物鏡背焦面處產(chǎn)生包含原子位置信息的衍射花樣(傅里葉變換),衍射花樣中的入射束和衍射束干涉(反傅里葉變換)會(huì)在物鏡的像平面處重建晶體點(diǎn)陣的像,通過(guò)比較應(yīng)變區(qū)域和正常區(qū)域的高分辨像,即可以測(cè)量局部應(yīng)變,目前常用的方法是Hytch等人提出的幾何相位分析(GPA),這是一種實(shí)空間分析和倒易空間分析相結(jié)合的應(yīng)變分析方法,它是將高分辨像經(jīng)過(guò)Fourier變換,在倒易空間進(jìn)行應(yīng)變分析,然后再通過(guò)反Fourier變換獲得應(yīng)變?cè)趯?shí)空間的分布信息。

▲圖三

(a)-(c) GeSi源漏極的單晶硅溝道的HRTEM 圖像及相應(yīng)區(qū)域的FFT圖像;(d) 由圖(a)的HRTEM經(jīng)GPA分析后獲得的平行于柵極(εxx)的單晶硅溝道應(yīng)變分布圖 εxx ,顯示溝道處Si受到壓應(yīng)力[3]

納米電子衍射(NBED)技術(shù)是指在TEM中通過(guò)光路調(diào)整獲得直徑小至2nm的相干性好的電子束,以對(duì)尺寸很小的在幾納米至幾十納米的顆粒進(jìn)行衍射成像,從而實(shí)現(xiàn)物相分析。配合專用軟件可控制電子束逐點(diǎn)逐行掃描,獲得微小區(qū)域的納米電子衍射mapping,通過(guò)分析衍射斑點(diǎn)位置的變化趨勢(shì),可進(jìn)一步分析該區(qū)域的應(yīng)力分布情況,其原理是倒空間的衍射點(diǎn)陣參數(shù)變化與實(shí)空間的晶格參數(shù)變化成反比,即如果材料的某部分原子面間距在應(yīng)力的作用下發(fā)生膨脹(收縮)時(shí),對(duì)應(yīng)在倒空間測(cè)得的衍射點(diǎn)之間的距離會(huì)縮小(擴(kuò)大)。

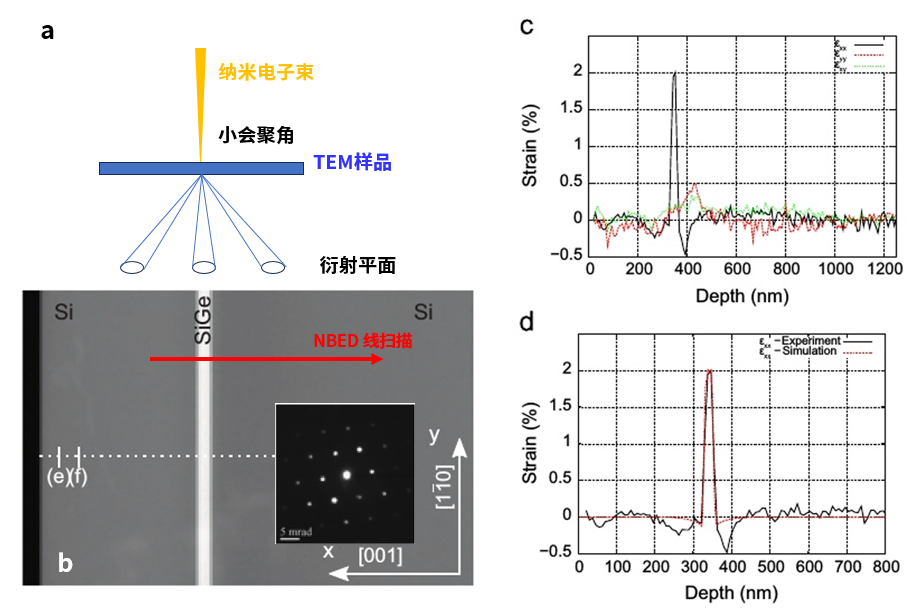

▲圖四

(a) NBED形成示意圖;

(b) 單晶硅中嵌入SiGe層的STEM圖像;

(c)在b圖進(jìn)行NBED線掃描獲得的應(yīng)變結(jié)果,顯示Si-GeSi界面附近單晶硅中存在X方向的應(yīng)變,Y方向無(wú)應(yīng)變。

(d) 實(shí)驗(yàn)測(cè)量的應(yīng)變分布可與有限元模擬的應(yīng)變分布結(jié)果相比擬,表明NBED測(cè)試應(yīng)變結(jié)果比較可靠[1]

四維掃描透射成像(4D STEM)是近年來(lái)發(fā)展起來(lái)的一種成像技術(shù),它是在掃描透射(STEM)模式下電子束會(huì)聚成一個(gè)極小的束斑照射到樣品上并在樣品表面進(jìn)行逐點(diǎn)逐行掃描,在樣品下方使用一塊具有足夠像素?cái)?shù)目、高動(dòng)態(tài)范圍以及高信噪比的電子探測(cè)器來(lái)收集所有的散射電子,即采集完整的會(huì)聚束電子衍射花樣并及時(shí)存儲(chǔ)到計(jì)算機(jī)中,即采集掃描區(qū)域的衍射mapping(四維數(shù)據(jù)集),對(duì)這個(gè)四維數(shù)據(jù)集的后處理是非常重要,目前已經(jīng)有一些開(kāi)源軟件能夠分析處理4D-STEM數(shù)據(jù),如py4DSTEM、pyxem等,或者研究人員可以根據(jù)自己的需求來(lái)編寫(xiě)程序?qū)?shù)據(jù)進(jìn)行處理分析,從而可以獲得材料的虛擬衍射成像、相位、取向和應(yīng)變分布、樣品厚度和傾斜度的測(cè)量等信息。4D STEM分析應(yīng)力的原理與NBED類似,也是利用4D-STEM技術(shù)采集一套目標(biāo)區(qū)域的NBED,利用軟件可以對(duì)材料的應(yīng)變分布進(jìn)行精準(zhǔn)分析,但是由于4D STEM的衍射圖樣噪聲和強(qiáng)度的復(fù)雜性,自動(dòng)和精確的衍射花樣分析仍然具有挑戰(zhàn)性。

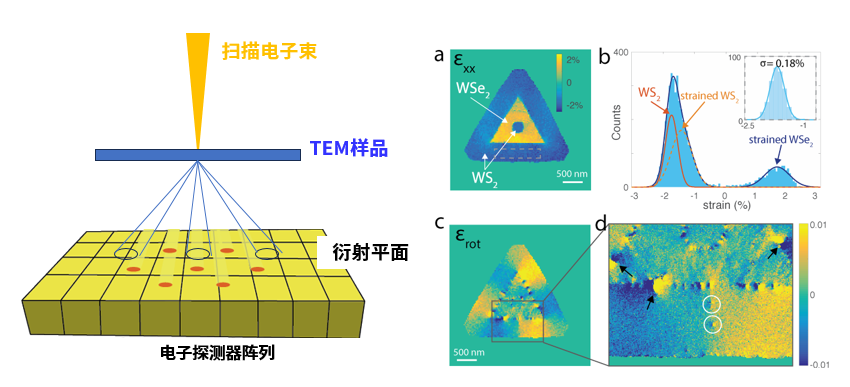

▲圖五

左 4D STEM成像示意圖;右 WS2/WSe2異質(zhì)結(jié)4D STEM應(yīng)變分析結(jié)果[4]

TEM全息暗場(chǎng)像(Holo Dark)是指在中心暗場(chǎng)衍射條件下利用無(wú)應(yīng)變的完整晶體區(qū)域的衍射束作為參考波,與應(yīng)變區(qū)域的衍射束相干涉,得到全息暗場(chǎng)干涉圖樣,再通過(guò)幾何位相分析方法計(jì)算出應(yīng)變區(qū)的應(yīng)變分布。利用這種方法可以得到尺度為200nm左右的區(qū)域的應(yīng)變分布,并具有較高的空間分辨率和應(yīng)變分析靈敏度。

旋進(jìn)電子衍射(PED)是最近20年發(fā)展起來(lái)的一種新技術(shù),它是通過(guò)圍繞電子顯微鏡的中心軸旋轉(zhuǎn)傾斜的入射電子束透過(guò)樣品產(chǎn)生衍射花樣,在一系列衍射條件下對(duì)這些衍射花樣進(jìn)行積分形成PED圖案。與普通電子衍射相比,旋進(jìn)電子衍射有以下特點(diǎn):一是旋進(jìn)電?衍射花樣斑點(diǎn)的?何位置不發(fā)?變化;二是隨著旋進(jìn)?度的增?,來(lái)?于??度晶?的更多衍射花樣變?yōu)榭梢暎直媛侍?;三是旋進(jìn)電?衍射的強(qiáng)度更接近于其運(yùn)動(dòng)學(xué)數(shù)據(jù);四是旋進(jìn)電?衍射對(duì)晶體取向缺陷不敏感,這是因?yàn)樵陔?束旋進(jìn)過(guò)程中, 其愛(ài)瓦爾德球掃掠過(guò)倒易空間, 可有效地補(bǔ)償細(xì)小的晶體取向缺陷;由于PED圖案的以上特點(diǎn),其在進(jìn)行應(yīng)變分析時(shí)應(yīng)變的準(zhǔn)確度和精確度均會(huì)比NBED要高得多。

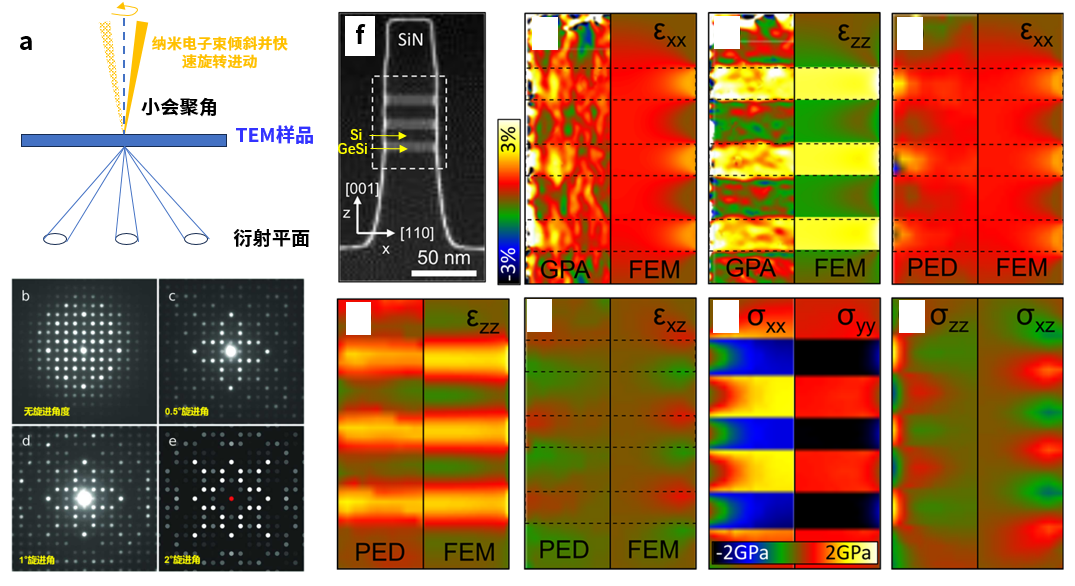

▲圖六

a PED原理示意圖;b-e 無(wú)旋進(jìn)角度和有旋進(jìn)角度衍射花樣對(duì)比;f 基于HRTEM的GPA分析和利用PED技術(shù)分析的Si-GeSi異質(zhì)結(jié)構(gòu)的應(yīng)變分布[5]

季豐電子

季豐電子成立于2008年,是一家聚焦半導(dǎo)體領(lǐng)域,深耕集成電路檢測(cè)相關(guān)的軟硬件研發(fā)及技術(shù)服務(wù)的賦能型平臺(tái)科技公司。公司業(yè)務(wù)分為四大板塊,分別為基礎(chǔ)實(shí)驗(yàn)室、軟硬件開(kāi)發(fā)、測(cè)試封裝和儀器設(shè)備,可為芯片設(shè)計(jì)、晶圓制造、封裝測(cè)試、材料裝備等半導(dǎo)體產(chǎn)業(yè)鏈和新能源領(lǐng)域公司提供一站式的檢測(cè)分析解決方案。

季豐電子通過(guò)國(guó)家級(jí)專精特新“小巨人”、國(guó)家高新技術(shù)企業(yè)、上海市“科技小巨人”、上海市企業(yè)技術(shù)中心、研發(fā)機(jī)構(gòu)、公共服務(wù)平臺(tái)等企業(yè)資質(zhì)認(rèn)定,通過(guò)了ISO9001、 ISO/IEC17025、CMA、CNAS、IATF16949、ISO/IEC27001、ISO14001、ANSI/ESD S20.20等認(rèn)證。公司員工近1000人,總部位于上海,在浙江、北京、深圳、成都等地設(shè)有子公司。

-

芯片

+關(guān)注

關(guān)注

458文章

51526瀏覽量

429491 -

SiC

+關(guān)注

關(guān)注

30文章

2975瀏覽量

63334 -

透射電子顯微鏡

+關(guān)注

關(guān)注

0文章

10瀏覽量

2217

原文標(biāo)題:透射電子顯微鏡(TEM)中的應(yīng)變分析技術(shù)

文章出處:【微信號(hào):zzz9970814,微信公眾號(hào):上海季豐電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

掃描式電子顯微鏡 (SEM)

電子顯微鏡隔振臺(tái)/減震臺(tái)/防震臺(tái)

透射電子顯微鏡透鏡穩(wěn)流電源的研究

透射電子顯微鏡的結(jié)構(gòu)與成像原理

掃描電子顯微鏡原理和應(yīng)用

透射電子顯微鏡工作原理及用途

透射電子顯微鏡成像原理資料下載

透射電子顯微鏡TEM的原理、參數(shù)及應(yīng)用

掃描電子顯微鏡(SEM )工作介紹

【應(yīng)用案例】透射電子顯微鏡TEM

透射電子顯微鏡的用途和特點(diǎn)

透射電子顯微鏡(TEM):基礎(chǔ)知識(shí)概覽

TEM樣本制備:透射電子顯微鏡技術(shù)指南

透射電子顯微鏡中的應(yīng)變分析技術(shù)

透射電子顯微鏡中的應(yīng)變分析技術(shù)

評(píng)論