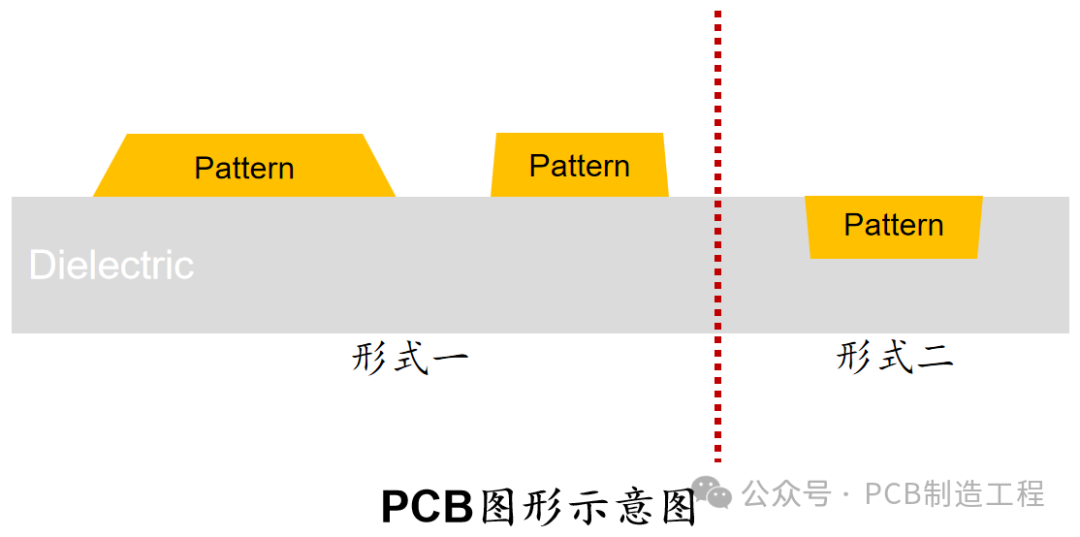

如上圖所示,PCB板上的圖形在被蝕刻出來(lái)之后,存在兩種不同的形式:

形式一:圖形位于介電層表面之上,其底部附著于介電層表面。

形式二:圖形嵌入到介電層之中,其底部與介電層表面齊平或略低于介電層表面。

“形式二”的圖形在PCB業(yè)界多稱為埋線路,而“形式一”的圖形沒(méi)有查到相關(guān)的稱呼,我們暫且稱之為傳統(tǒng)線路。

傳統(tǒng)線路

PCB制造行業(yè)的圖形制造工藝,不管是減銅法和加成法(全加成和半加成mSAP/SAP)均可以實(shí)現(xiàn)傳統(tǒng)線路的制作。

傳統(tǒng)線路PCB板的生產(chǎn)制作,PCB板廠通常基于PCB板設(shè)計(jì)工藝和制造成本的綜合考量而采取不同的圖形工藝,以實(shí)現(xiàn)品質(zhì)與成本的平衡。

埋線路

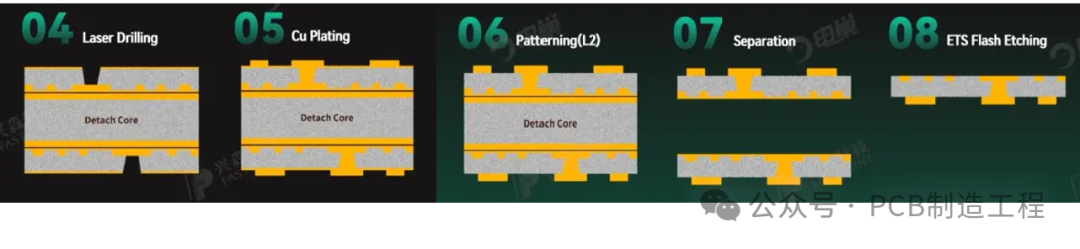

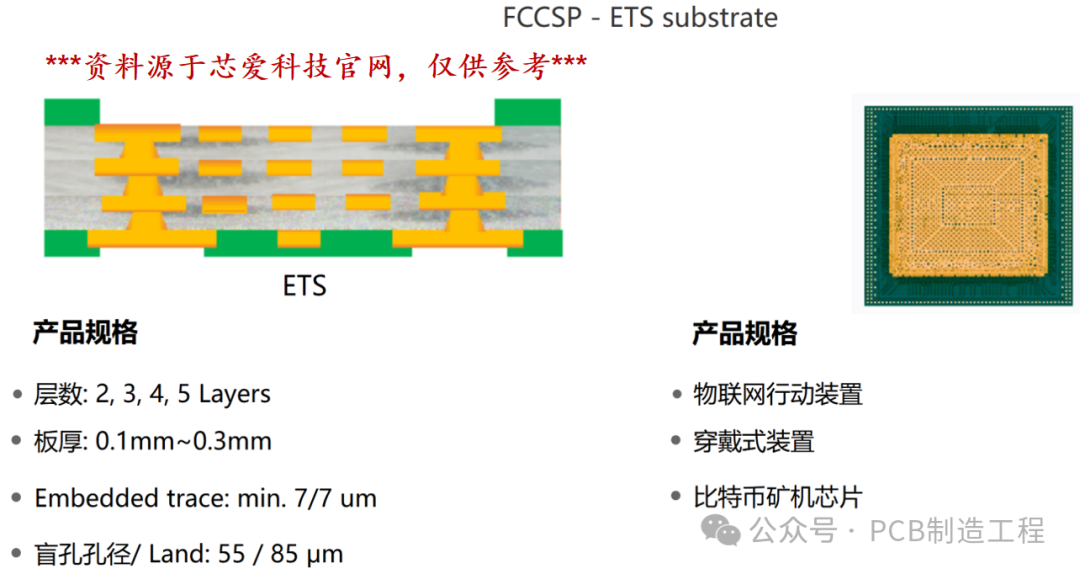

埋線路的制作涉及埋入線路技術(shù)ETS或EPP技術(shù)。

EPP:Embeded Pattern Process

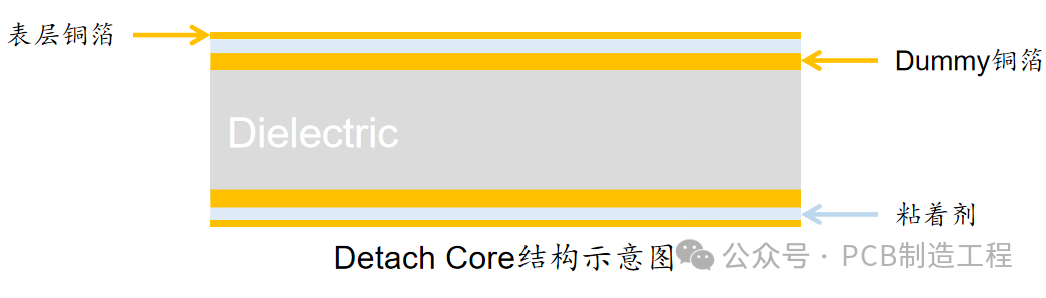

ETS/EPP技術(shù)也是一種無(wú)芯基板Coreless工藝, 其與常規(guī)Coreless工藝的區(qū)別在于:有一層表層圖形形成在Detach Core材料的表層銅箔上,并利用壓合工藝將圖形埋入介質(zhì)層中(常規(guī)Coreless工藝是直接在銅箔上增層);再在Detach Core基板分離后,通過(guò)閃蝕Flash Etching將底銅咬蝕掉形成埋入式圖形。

Detach Core結(jié)構(gòu)如下,其作為支撐輔助層材料,以實(shí)現(xiàn)超薄、細(xì)線路PCB板的制作。

ETS/EPP技術(shù)可以做到最小線寬/線距15μm/15μm以下,線路控制精度高,而且線路嵌入樹(shù)脂中。

所謂“線路嵌入樹(shù)脂中”是指線路的上面被樹(shù)脂包覆,線路結(jié)合力大;這也是埋線路的優(yōu)點(diǎn)之一。

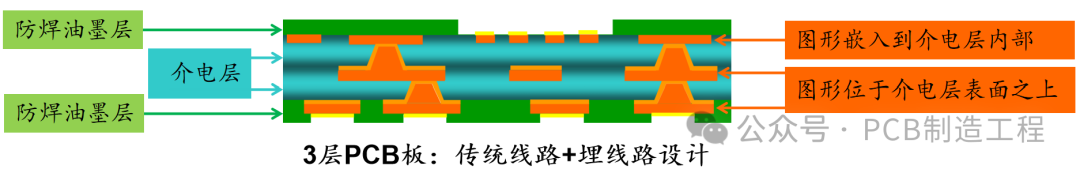

埋線路PCB板

市場(chǎng)上使用ETS/EPP技術(shù)的PCB板,通常被稱為埋線板或平齊板。

埋線路設(shè)計(jì)走mSAP或SAP工藝。

多為薄板,超薄板設(shè)計(jì),如CSP(Chip Scale Package)封裝基板。

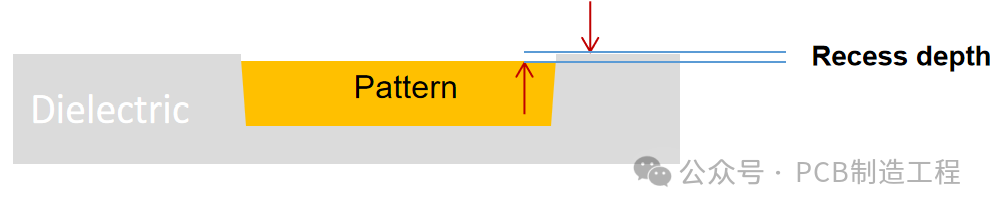

挑戰(zhàn)點(diǎn):在產(chǎn)品封裝過(guò)程中,埋線深度會(huì)影響錫球與焊盤(pán)的焊接,尤其是當(dāng)埋線深度較大時(shí),可能會(huì)導(dǎo)致焊接不良和產(chǎn)品失效等異常。

特殊管控點(diǎn):圖形表面與介電層表面的深度差Recess depth (常見(jiàn)規(guī)范<=5um)。

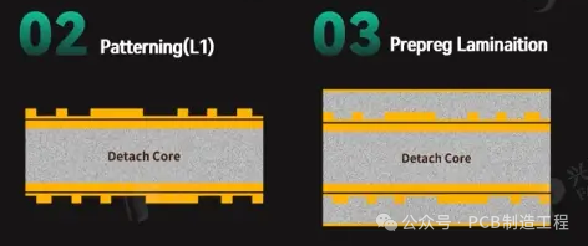

如前所述,埋線路設(shè)計(jì)之PCB板需要使用無(wú)芯基板Coreless工藝,但其流程與常規(guī)Coreless工藝PCB板的區(qū)別如下:

常規(guī)Coreless工藝PCB板:直接在Detach Core表面銅箔上增層。

埋線路Coreless工藝PCB板:Detach Core的表層銅箔是埋線路層別。

埋線路PCB板的具體制作流程相對(duì)比較復(fù)雜,本文會(huì)結(jié)合如下案例進(jìn)行簡(jiǎn)單說(shuō)明,歡迎感興趣的朋友斧正及交流。

案例(***資料源于網(wǎng)絡(luò),僅供參考***):埋線路設(shè)計(jì)之2層PCB板,Layer 1層為埋線路設(shè)計(jì)。

Pattern圖形L1層走mSAP/SAP流程(Detach Core表面銅箔形成之層別):

->化銅->壓膜->曝光->垂直顯影->圖形電鍍->去膜->烘烤->棕化->疊板->壓合->

Pattern圖形L2層走mSAP/SAP流程(壓合增層之層別):

->Laser drilling->化銅->壓膜->曝光->顯影->圖形電鍍->去膜->烘烤->Detach Core分板->Flash Etching->

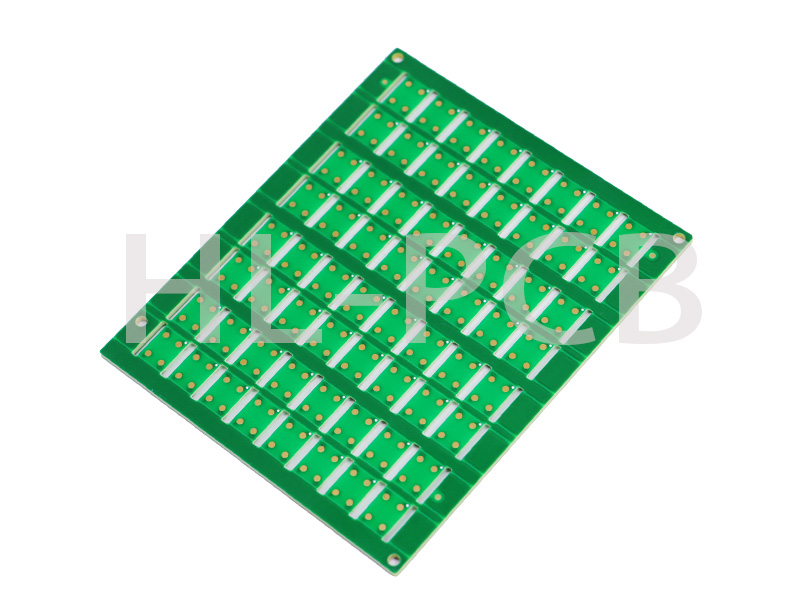

埋線板產(chǎn)品示例

-

pcb

+關(guān)注

關(guān)注

4319文章

23111瀏覽量

398316 -

線路

+關(guān)注

關(guān)注

2文章

139瀏覽量

20858 -

傳統(tǒng)線路

+關(guān)注

關(guān)注

0文章

2瀏覽量

1455

原文標(biāo)題:傳統(tǒng)線路 vs 埋線路

文章出處:【微信號(hào):深圳市賽姆烯金科技有限公司,微信公眾號(hào):深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

PCB盲埋孔,盲埋孔線路板,盲埋孔線路板工藝,盲埋孔線路板打樣

盲孔與埋盲孔電路板之前的區(qū)別

無(wú)線ap和無(wú)線路由器的區(qū)別

HDI埋盲孔線路板的生產(chǎn)工藝流程

陶瓷線路板與傳統(tǒng)FR4線路板的區(qū)別在哪里?

盲埋孔線路板的基本概念和應(yīng)用領(lǐng)域

單相交流線路與三相交流線路的區(qū)別

地埋線路的守護(hù)者:電纜行波故障預(yù)警與定位裝置

vty線路和console線路的區(qū)別

埋盲孔PCB線路板加工流程

hdi盲埋孔線路板生產(chǎn)工藝流程

傳統(tǒng)線路和埋線路區(qū)別

傳統(tǒng)線路和埋線路區(qū)別

評(píng)論