引言

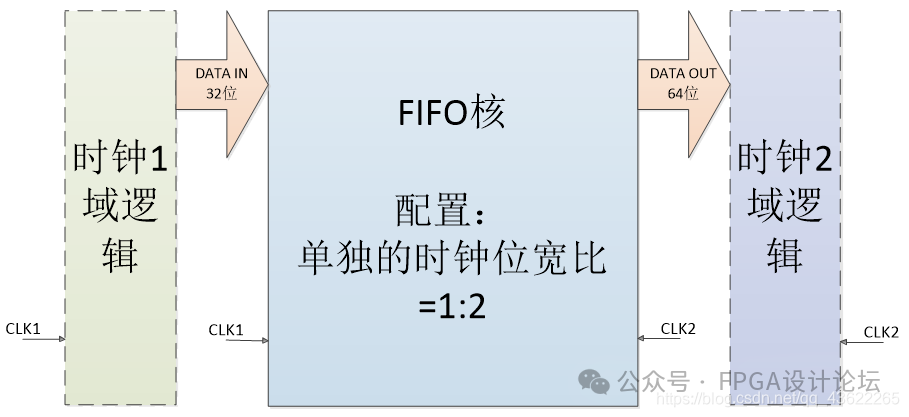

在數字設計中,利用FIFO進行數據處理是非常普遍的應用,例如,實現時鐘域交叉、低延時存儲器緩存、總線位寬調整等。下圖給出了FIFO生成器支持的一種可能配置。

設計中有兩個獨立的時鐘域并且讀數據總線的位寬是寫數據總線位寬的2倍。使用FIFO生成器可以快速實現這種配置,從而在Xilinx FPGA芯片上實現特定的設計要求。

實際應用案例:本案例背景是將信號處理系統中ADC采集到的數據寫入FPGA芯片外掛的DDR3,完成采樣數據的存儲。ADC采樣率設定為96Mhz,兩個采樣點(兩個16bit數據拼接成一個32bit)為單位,DDR讀寫時鐘速率為150Mhz,總線數據位寬64bit,二者時鐘域、位寬均不同,故需在中間加入一級FIFO,從而實現時鐘域的交叉以及總線位寬的調整。

下面將從FIFO IP核的創建,模塊程序編寫,功能仿真驗證等三個方面完成本案例的介紹:

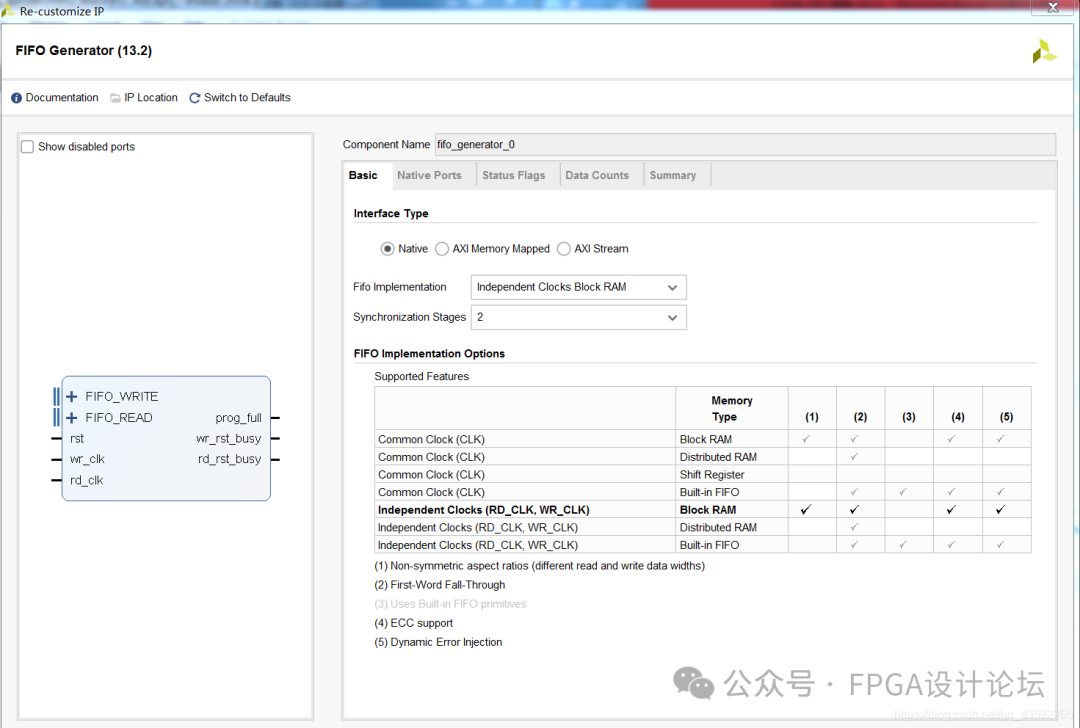

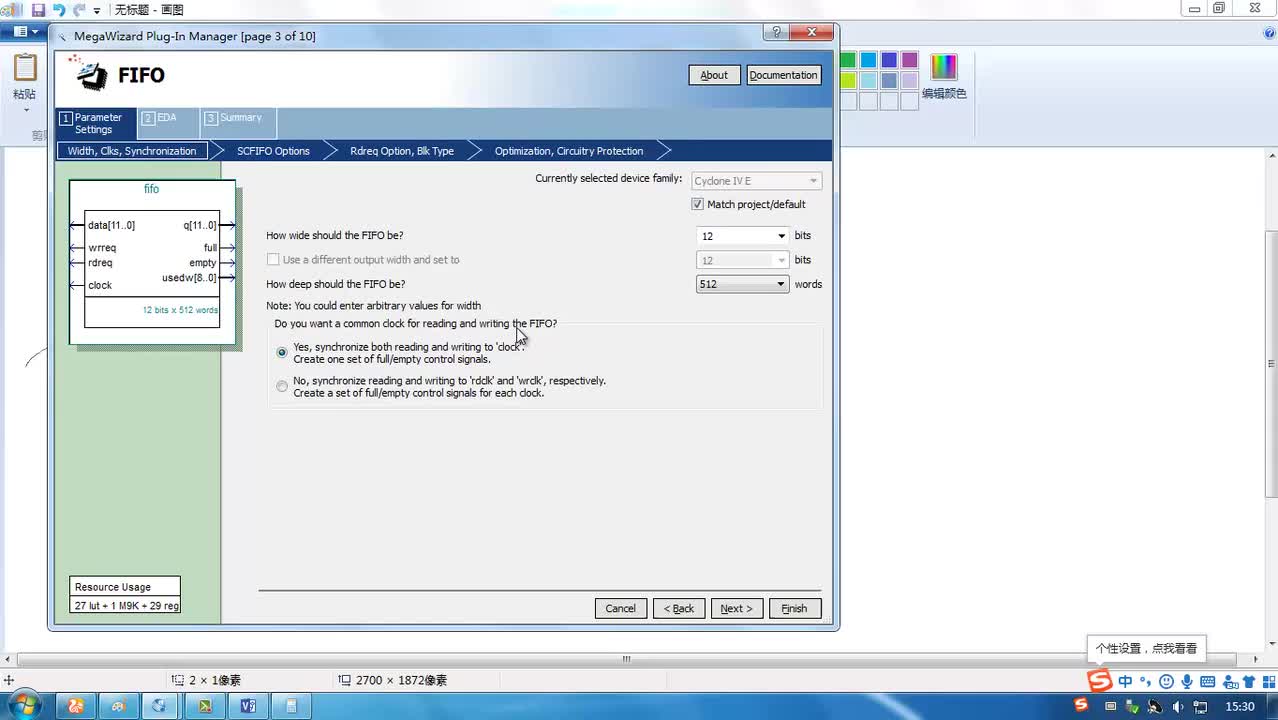

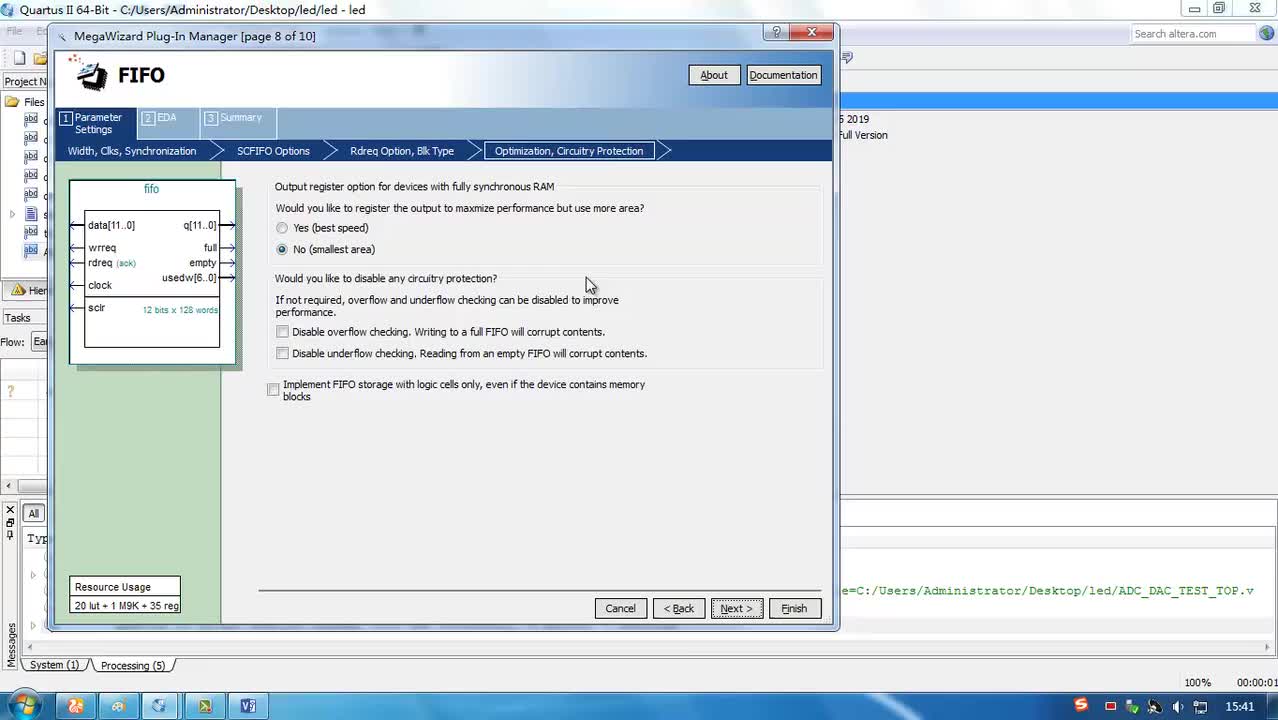

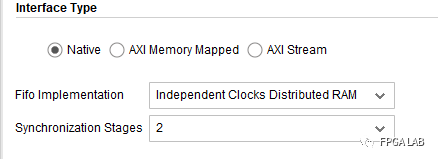

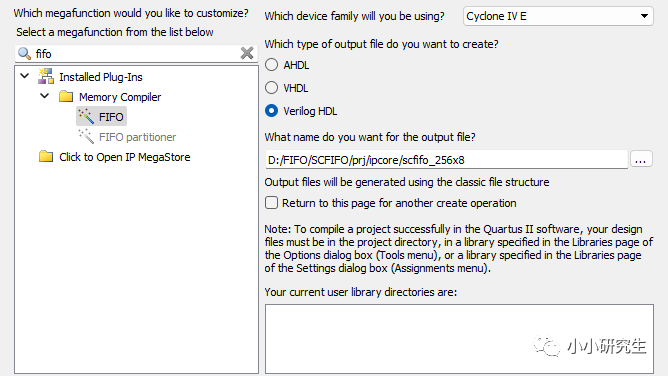

1)FIFO IP核的創建:打開Vivado軟件(本例程基于Vivado 2018.3版本)IP catalog一欄,輸入FIFO,雙擊進入如下界面,第一個Basic選項卡主要是設置FIFO接口類型,可設置為正常的Native模式或AXI總線接口,一般我們選擇Native即可。然后選擇FIFO實現的類型:讀寫使用獨立時鐘還是同一時鐘,實現時使用分布式RAM、Block RAM還是專用的FIFO等等,這里我們選擇Independent Clocks Block RAM,即獨立時鐘塊RAM的FIFO。

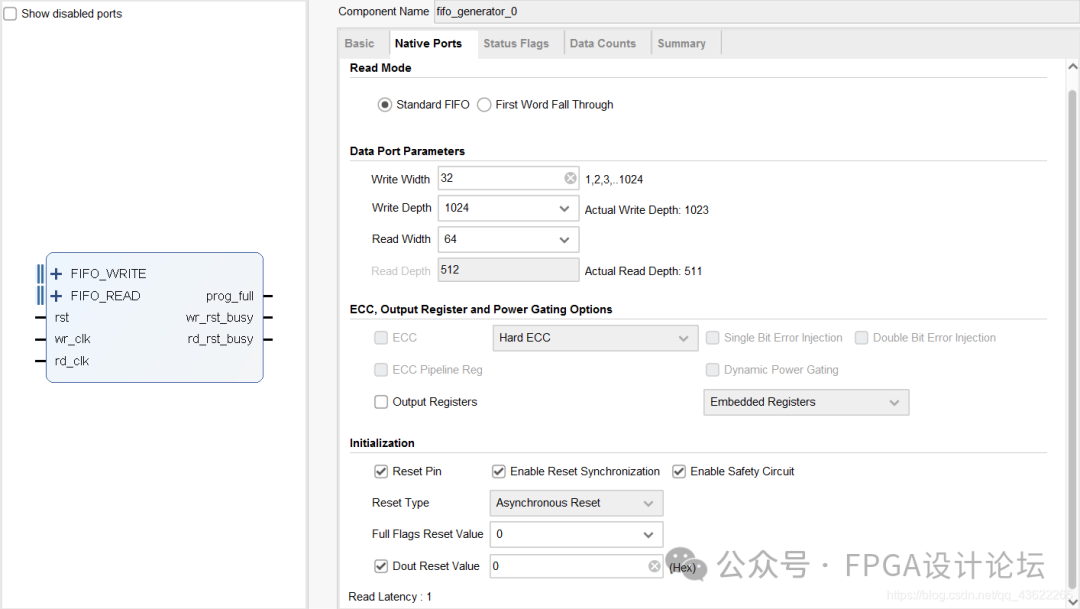

切換至第二個Native Ports選項卡,這個界面主要是設置讀寫數據位寬、深度以及一些端口的使能、端口復位值等的設置。結合本案例的應用,設置寫位寬為32bit,深度設置為1024,讀位寬設置為64bit。使能復位管腳,設置滿信號(Full Flags)的復位值為0,讀數據(Dout)復位值為0。

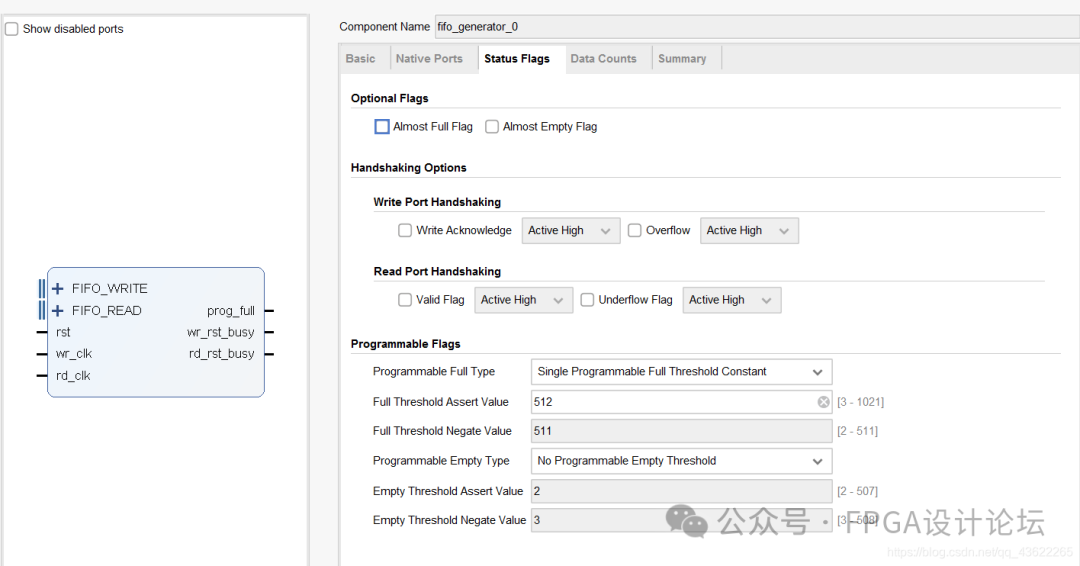

然后切換至第三個Status Flags選項卡,本選項卡是設置其余一些可選的標志信號,本案例需使用本界面下的Programmable Flags,即可編程的標志信號,設置滿標志門限置位值(Full Threshold Assert Value),可使FIFO寫入的數據總數大于等于該值后將prog_full(可編程滿標志信號)拉高,相比full信號使用起來更靈活。DDR讀寫采用Burst方式(突發傳輸),一次連續寫入256個數,這里設置Full Threshold Assert Value為512(256*2,2是FIFO讀寫位寬的比值),當FIFO寫入512個數后,prog_full拉高,進行FIFO讀操作,一次連續讀256個64bit的數(對應寫的512個32bit數)存入DDR。

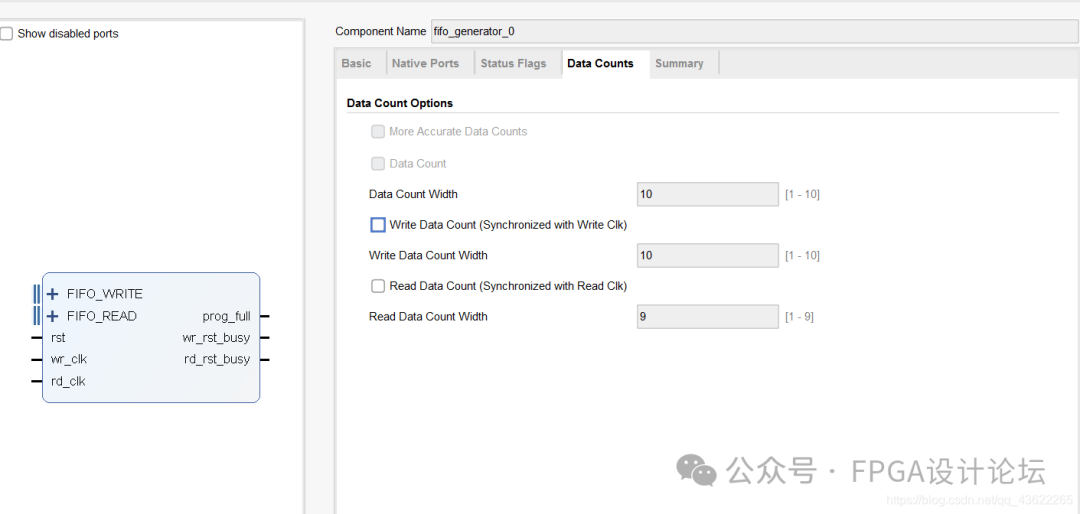

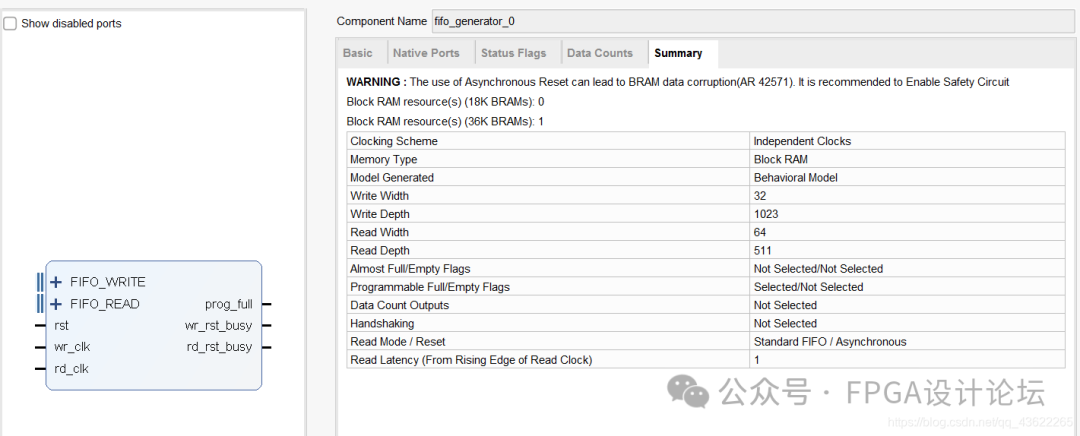

切換至第四個Data Counts選項卡,本選項卡主要是選擇是否使用讀寫數據計數,本案例不使用計數,此頁面保持默認設置。

最后Summary選項卡是FIFO設置后的各項信息,可核對FIFO設置是否正確及設計是否滿足要求。

2)模塊程序的編寫

頂層模塊:FIFO_test.v

module FIFO_test(

input rst,

input wr_clk,

input rd_clk,

input [31:0] din,

input wr_en,

input rd_en,

output [63:0] dout,

output full,

output empty,

output prog_full,

output wr_rst_busy,

output rd_rst_busy

);

fifo_generator_0 U_fifo (

.rst(rst), // input wire rst

.wr_clk(wr_clk), // input wire wr_clk

.rd_clk(rd_clk), // input wire rd_clk

.din(din), // input wire [31 : 0] din

.wr_en(wr_en), // input wire wr_en

.rd_en(rd_en), // input wire rd_en

.dout(dout), // output wire [63 : 0] dout

.full(full), // output wire full

.empty(empty), // output wire empty

.prog_full(prog_full), // output wire prog_full

.wr_rst_busy(wr_rst_busy), // output wire wr_rst_busy

.rd_rst_busy(rd_rst_busy) // output wire rd_rst_busy

);

endmodule

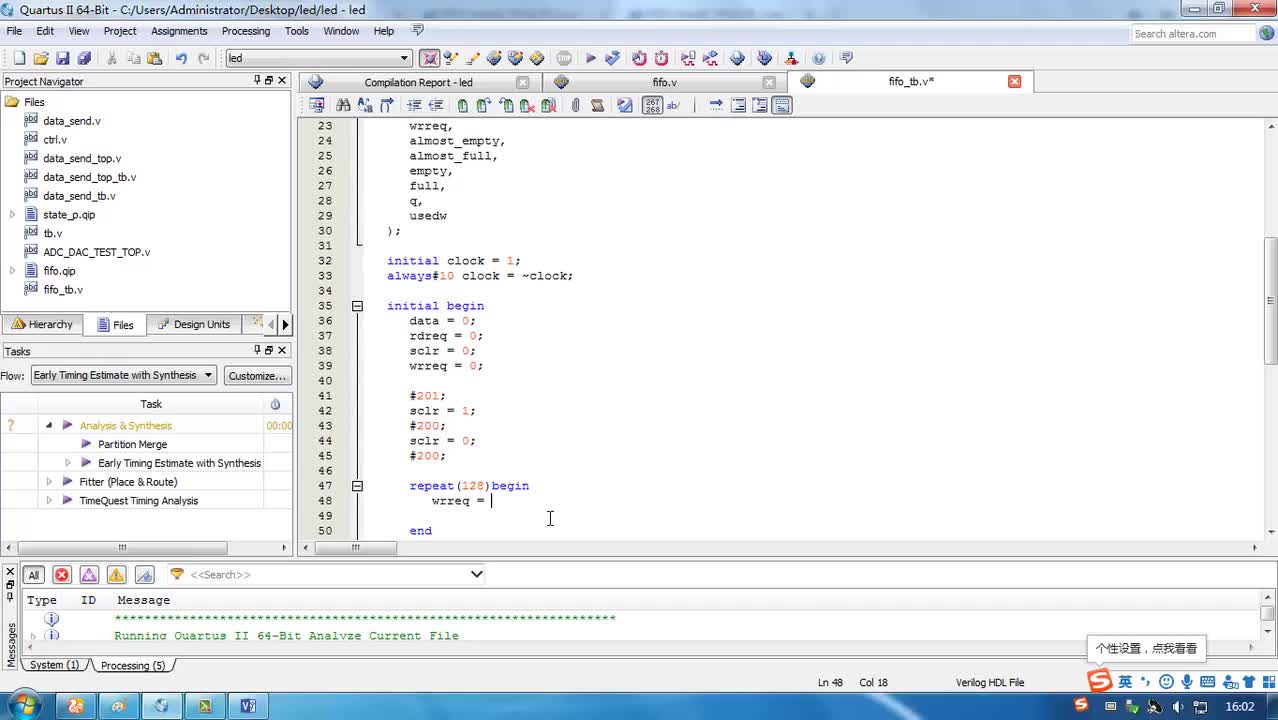

TestBench模塊:FIFO_sim

module FIFO_sim;

reg rst;

reg wr_clk;

reg rd_clk;

reg [31:0] din;

reg wr_en;

reg rd_en;

wire [63:0] dout;

wire full;

wire empty;

wire prog_full;

wire wr_rst_busy;

wire rd_rst_busy;

initial begin

rst = 1;

wr_clk = 0;

wr_en = 0;

rd_clk = 0;

rd_en = 0;

din = 0;

#1000

rst = 0;

end

always #10.4167 wr_clk = ~wr_clk;

always #3.3333 rd_clk = ~rd_clk;

always @(posedge wr_clk) begin

if(!wr_rst_busy && !rst) begin

wr_en <= 1'b1;

din <= din + 1'b1;

end

end

reg [1:0] RD_state = 2'b01;

reg [15:0] rd_count = 'd0;

always @(posedge rd_clk) begin

case(RD_state)

2'b01: begin

if(!rd_rst_busy && prog_full) RD_state <= 2'b10;

end

2'b10: begin

if(rd_count >= 'd256) begin

RD_state <= 2'b01;

rd_count <= 'd0;

rd_en <= 1'b0;

end

else begin

rd_count <= rd_count + 1'b1;

rd_en <= 1'b1;??

end

end

default: begin

RD_state <= 2'b01;

end

endcase

end

FIFO_test U_FIFO_test(

.rst(rst),

.wr_clk(wr_clk),

.rd_clk(rd_clk),

.din(din),

.wr_en(wr_en),

.rd_en(rd_en),

.dout(dout),

.full(full),

.empty(empty),

.prog_full(prog_full),

.wr_rst_busy(wr_rst_busy),

.rd_rst_busy(rd_rst_busy)

);

endmodule

編寫TestBench時,寫時鐘為48Mhz,讀時鐘為150MHz。寫是連續的,使能一直打開,表示AD是一直連續工作的,寫入夠512個數后,prog_full拉高,進行一次FIFO讀操作,連續讀出256個數,然后等待下一次prog_full為高的到來,如此周而復始。

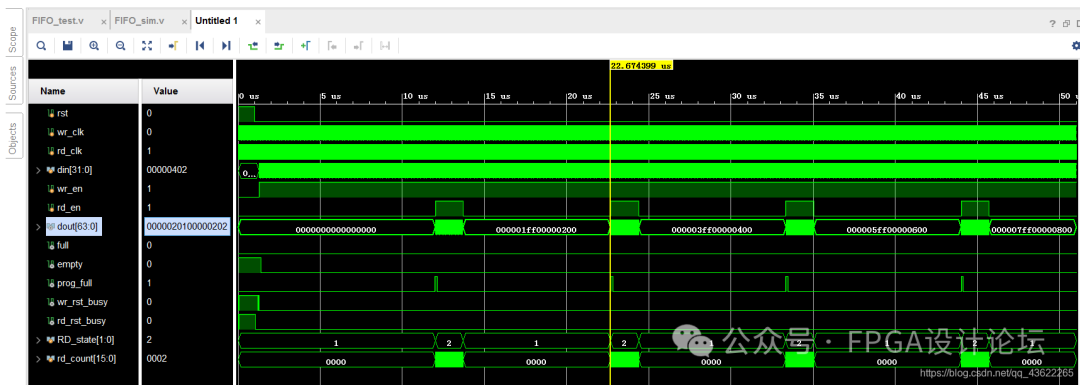

3)波形功能仿真

點擊Run simulation,啟動功能仿真,可以看到FIFO一開始復位結束后,進行寫操作,每寫夠512個數后,prog_full拉高,進行一次讀操作,連續讀出256個數后,停止讀操作,等待下一次prog_full拉高時刻的到來。將讀出的數據和寫入的數據對比,完全一致,不存在丟數的情況,因此驗證了功能的正確性。

總結:通過本案例代碼程序的編寫以及波形功能仿真,可以熟悉并掌握FIFO的基本功能和常用用法:數據跨時鐘域及總線位寬調整。本例程是我自己在一個項目中用到的,結合自己的需求進行編寫的,并不具有普適性,寫此博客的初衷也是讓一些不熟悉FIFO用法的讀者能快速入門,可能并不能直接幫助到所有的讀者。希望大家可以在此基礎上,結合自己的工程應用實例,完成自己相應的設計。

原文鏈接:https://blog.csdn.net/qq_43622265/article/details/113497121

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603971 -

fifo

+關注

關注

3文章

389瀏覽量

43709 -

IP核

+關注

關注

4文章

329瀏覽量

49520 -

生成器

+關注

關注

7文章

316瀏覽量

21042

原文標題:FIFO IP核的使用

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

求助:用fifo ip核作延時輸出數據

求助 FPGA 異步FIFO IP核

ISE中,調用FIFO IP核遇到的問題?

XILINX FIFO IP核調用問題

以MIPI項目為例講解Diamond FIFO生成和例化全過程

FIFO IP核的使用

FIFO是什么?有什么用?FIFO IP核應該如何使用?

講解幾點關于FIFO IP核使用時的注意事項

FPGA學習筆記:FIFO IP核的使用方法

FIFO IP核的使用教程

FIFO IP核的使用教程

評論