芯片是人工智能(AI)應(yīng)用的支柱,為從自動駕駛汽車到虛擬助手等各類應(yīng)用提供著核心動力。AI芯片專門設(shè)計用于處理海量數(shù)據(jù),并能實時做出決策,因此它們對于確保最終應(yīng)用的成功發(fā)揮著至關(guān)重要的作用。隨著AI引發(fā)的變革,各行業(yè)對更強大、更高效的AI芯片的需求持續(xù)攀升。AI算法的日益復(fù)雜,市場對AI運行速度需求不斷提升,測試AI芯片已成為半導(dǎo)體公司面臨的一大挑戰(zhàn)。如果沒有經(jīng)過適當(dāng)?shù)臏y試,這些芯片可能無法按預(yù)期工作,從而導(dǎo)致錯誤,甚至可能產(chǎn)生危險的后果。特別對于需要實時決策的應(yīng)用來說,這一點尤其重要,任何錯誤或故障都不能忽視。

本文將探討測試AI芯片所面臨的挑戰(zhàn),以及混合信號測試儀在實現(xiàn)AI芯片驗證所需的持續(xù)發(fā)展的功能。

復(fù)雜的AI芯片設(shè)計帶來特定測試需求

測試AI芯片的主要挑戰(zhàn)之一是它們所支持的算法的復(fù)雜性。現(xiàn)代AI芯片通常集成了多種處理要素,如CPU、GPU和專用的AI核心,并依賴于數(shù)字和模擬信號的組合。這種組合需要針對每個功能塊進行測試,同時確保無縫的互操作性。新一代混合信號測試儀通過融入這些高級功能,能有效地克服AI芯片設(shè)計日益復(fù)雜所帶來的挑戰(zhàn)。

高精度模擬和數(shù)字資源

為了適應(yīng)AI芯片不斷增加的復(fù)雜性及引腳數(shù)量,混合信號測試儀應(yīng)在測試數(shù)字和模擬電路時具備高精度。這意味著測試儀應(yīng)配備多種功能和性能,包括高速數(shù)字和模擬測試、低噪聲信號生成和分析、高速數(shù)字生成及高級數(shù)據(jù)處理能力。

大帶寬需求催生高速數(shù)字通道與深存儲

為了跟上AI芯片架構(gòu)的快速發(fā)展,混合信號測試儀需要擁有更復(fù)雜的功能。伴隨芯片設(shè)計人員利用 3D 堆疊等技術(shù)來擴大帶寬,并促進在創(chuàng)紀錄的時間內(nèi)傳輸大量數(shù)據(jù)集,新一代測試儀必須做出相應(yīng)的調(diào)整。這就需要大量的高速數(shù)字通道,能夠處理從 400MHz 到數(shù)十 GHz 的頻率。此外,大存儲深度對于容納這些復(fù)雜芯片所需的海量測試數(shù)據(jù)至關(guān)重要。

復(fù)雜的芯片架構(gòu)要求測試設(shè)備具備分布式智能

AI芯片復(fù)雜的多芯/多核架構(gòu)帶來了另一個挑戰(zhàn)。例如,神經(jīng)處理單元 (NPU) 通常包含多個核心。為了有效地測試這些芯片,混合信號測試儀需要更高的智能水平。多核架構(gòu)的分布式智能,使測試儀能夠以異步方式執(zhí)行多個計算。想象一下,測試儀的各個儀器和組件充當(dāng)獨立的智能模塊,能夠自主啟動測試模式。這種分布式處理能力能顯著提高測試效率并簡化復(fù)雜AI芯片的驗證流程,使測試人員能夠模擬復(fù)雜的現(xiàn)實操作條件。

智能混合信號測試儀助力提升效率與速度

測試AI芯片的另一個挑戰(zhàn)是對速度和效率的需求。隨著AI應(yīng)用的日益普及,對更快處理速度和更低功耗的需求也在增加。

這也給半導(dǎo)體公司帶來了壓力,要求他們開發(fā)出既能滿足這些需求又能經(jīng)過充分測試的芯片。傳統(tǒng)的測試設(shè)備和方法可能耗時且很難跟上開發(fā)速度,從而延遲產(chǎn)品上市。為了提高效率,混合信號測試儀應(yīng)具備高多站點能力,并能融入最大化測試執(zhí)行速度的特定功能:

? 分布式智能是改變游戲規(guī)則的技術(shù):測試儀及其儀器內(nèi)嵌入的多個CPU可以同時工作,允許測試儀并發(fā)運行多個測試過程,加快測試速度。

? 多時域能力是最大化測試速度的關(guān)鍵。此功能使測試儀能夠同時運行具有不同時域的數(shù)字信號。這意味著可以并發(fā)測試被測芯片內(nèi)的各個模塊,大幅縮短整體測試時間。

? 模擬和數(shù)字儀器上嵌入的數(shù)字信號處理(DSP)單元有助于優(yōu)化測試時間。這些板載DSP單元直接在儀器上執(zhí)行數(shù)據(jù)解碼和計算,消除了將數(shù)據(jù)來回傳輸?shù)街醒胩幚韱卧娜哂噙^程。

? 協(xié)議感知儀器架構(gòu)非常重要。通過理解被測設(shè)備(DUT)使用的通信協(xié)議,測試儀可以簡化模式復(fù)雜性并優(yōu)化通信效率,從而進一步加快測試速度。

監(jiān)控芯片功耗,確保管理效率

AI芯片的一個特點是注重功耗。這使得功耗管理成為新一代AI芯片混合信號測試儀必須具備的關(guān)鍵特性之一。

多域功耗管理,有利于測試復(fù)雜芯片

AI芯片通常采用高密度布局,集成了具有各自特定功耗需求的多種處理元素。這轉(zhuǎn)化為多個功耗域,每個域都需要進行細致的驗證。測試儀需要能夠精確控制和監(jiān)控這些域中的電源交付,不僅是在系統(tǒng)級別,而且是在芯片的各個部分。這種精細的功耗管理確保芯片在真實條件下運行,從而能夠準(zhǔn)確驗證功耗并檢測出可能未被發(fā)現(xiàn)的相關(guān)缺陷。

應(yīng)對AI芯片高功耗挑戰(zhàn)

AI芯片所需的大量處理能力使其本身功耗較高。這種高功耗轉(zhuǎn)化為數(shù)據(jù)中心的顯著能源成本和散熱挑戰(zhàn),令I(lǐng)T管理人員頭疼不已。為了解決這一問題,混合信號測試儀必須配備一套強大的電源,能夠準(zhǔn)確地在各種工作點對被測AI芯片進行激勵。這能夠?qū)崿F(xiàn)芯片功耗行為的全面剖析和驗證,確保其符合設(shè)計規(guī)范,并有利于實現(xiàn)更高效的系統(tǒng)。通過模擬現(xiàn)實環(huán)境的功耗條件,測試儀可以幫助緩解與AI部署相關(guān)的數(shù)據(jù)中心功耗問題。

應(yīng)對高電流、精密模擬通道的功耗波動需求

AI芯片的動態(tài)特性需要新一代測試儀具有一定數(shù)量的高電流模擬通道。與具有穩(wěn)定功耗需求的傳統(tǒng)芯片不同,AI芯片隨著工作負載的變化而呈現(xiàn)出波動的功耗。測試儀的模擬通道需要能夠提供這些高電流,同時保持精確控制。快速儀器對于有效調(diào)制所提供的電流以響應(yīng)芯片的實時要求同樣重要。這確保了芯片在任何給定時刻都能接收到所需的準(zhǔn)確電量,模擬真實的操作條件并實現(xiàn)全面的測試。

AI驅(qū)動的測試開發(fā)將簡化時間和資源

測試AI芯片最有前景的解決方案之一是利用AI自身優(yōu)勢。運用AI進行測試程序生成和缺陷分析可以顯著提高效率和有效性。想象一下,一個AI可以從過去的測試數(shù)據(jù)中學(xué)習(xí),以建議最佳的測試序列和參數(shù),并準(zhǔn)確找出故障的根本原因:這將徹底改變測試開發(fā)的流程,節(jié)省時間。

對于需要大量測試應(yīng)用的公司來說意義非凡,因為它可以節(jié)省時間和資源。通過自動化測試開發(fā)操作,測試工程師可以專注于其他重要任務(wù),如分析數(shù)據(jù)和提高性能。

AI還可以助力提高測試的速度和效率,因為它可以快速分析大量數(shù)據(jù)并識別潛在問題。這可以幫助企業(yè)跟上開發(fā)速度,并更快地將產(chǎn)品推向市場。

2024年AI行業(yè)在創(chuàng)新與挑戰(zhàn)中加速前行!從AI模型界的“神仙打架”到AI芯片巨頭持續(xù)火爆,從企業(yè)級應(yīng)用的全面煥新到學(xué)術(shù)與產(chǎn)業(yè)的深度碰撞,AI應(yīng)用已經(jīng)遍地開花,每一次突破都在改寫行業(yè)格局。SPEA積極擁抱AI浪潮下的挑戰(zhàn)與機遇,以更智能、更完善的測試設(shè)備助力AI技術(shù)的快速發(fā)展和應(yīng)用落地。

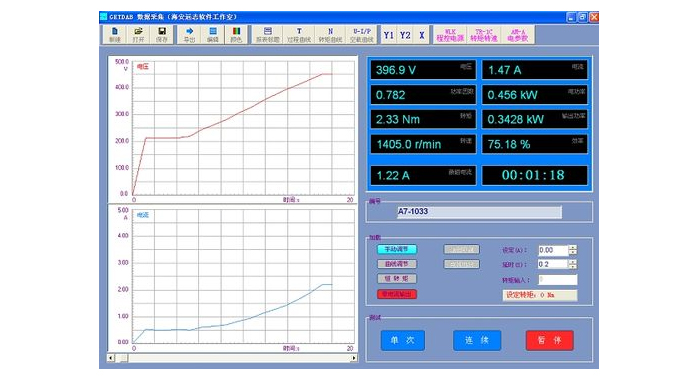

SPEA新一代混合信號測試儀 (DOT800)具有以下功能:

? 高速數(shù)字和模擬測試能力

? 大內(nèi)存深度

? 基于多核架構(gòu)的分布式智能

? 多時域操作

? 模擬和數(shù)字儀器上的DSP單元

? 協(xié)議感知儀器

? 一套強大的電源

這些創(chuàng)新升級使混合信號測試儀能夠模擬真實世界的操作條件,執(zhí)行全面的電源完整性測試,并簡化測試過程。

將AI集成到測試過程中具有巨大潛力。AI驅(qū)動的測試程序和缺陷分析可以顯著提高效率和有效性,使測試工程師能夠?qū)W⒂诟邔哟蔚娜蝿?wù)。運用這些新功能,半導(dǎo)體公司可以確保對AI芯片進行穩(wěn)健的驗證,有望為下一代開創(chuàng)性的AI應(yīng)用鋪平道路。

-

測試儀

+關(guān)注

關(guān)注

6文章

3777瀏覽量

55001 -

混合信號

+關(guān)注

關(guān)注

0文章

481瀏覽量

64983 -

AI芯片

+關(guān)注

關(guān)注

17文章

1901瀏覽量

35141

發(fā)布評論請先 登錄

相關(guān)推薦

DOT800 多核混合信號測試儀

防水測試儀:快速測試技巧分享

Rinaldi代表團到訪SPEA總部:探索全球頂尖自動化測試技術(shù)

電池測試儀的使用方法 電池測試儀適用范圍

環(huán)路測試儀的工作原理是什么

LCR測試儀怎么測試電感?

多功能網(wǎng)絡(luò)測試儀怎么用

電池內(nèi)阻測試儀

藍牙測試儀的作用

LCR測試儀的原理和使用方法

阻抗分析儀和LCR測試儀的區(qū)別

SPEA創(chuàng)新實踐:AI芯片混合信號測試儀

SPEA創(chuàng)新實踐:AI芯片混合信號測試儀

評論