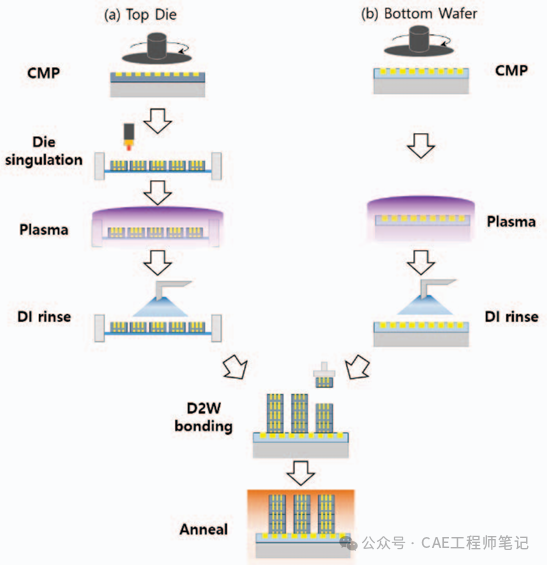

先進封裝技術(Semiconductor Advanced Packaging) - 1 混合鍵合技術(上)

先進封裝技術(Semiconductor Advanced Packaging) - 2 混合鍵合技術(下)

先進封裝技術(Semiconductor Advanced Packaging) - 3 Chiplet 異構集成(上)

先進封裝技術(Semiconductor Advanced Packaging) - 4 Chiplet 異構集成(下)

先進封裝技術(Semiconductor Advanced Packaging) - 5 TSV 異構集成與等效熱仿真

先進封裝技術(Semiconductor Advanced Packaging) - 6 扇出型晶圓級封裝(FOWLP)

先進封裝技術(Semiconductor Advanced Packaging) - 7 扇出型板級封裝(FOPLP)

先進封裝技術(Semiconductor Advanced Packaging) - 8 3D封裝與TSV技術

先進封裝技術(Semiconductor Advanced Packaging) - 9 堆疊封裝(PoP)技術

先進封裝技術(Semiconductor Advanced Packaging) - 10 2.5D封裝與異構集成技術

先進封裝技術(Semiconductor Advanced Packaging) - 11 SiP 系統級封裝

先進封裝技術(Semiconductor Advanced Packaging) - 12 表面貼裝技術 SMT

先進封裝技術(Semiconductor Advanced Packaging) - 13 倒裝封裝 Flip Chip

先進封裝技術(Semiconductor Advanced Packaging) - 14 光電共封技術(CPO) (上)

先進封裝技術(Semiconductor Advanced Packaging) - 15 光電共封技術(CPO) (下)

先進封裝技術(Semiconductor Advanced Packaging) - 16 硅橋技術(Si Bridge)(上)

先進封裝技術(Semiconductor Advanced Packaging) - 17 硅橋技術(Si Bridge)(下)

先進封裝技術(Semiconductor Advanced Packaging) - 18 TGV 玻璃通孔技術

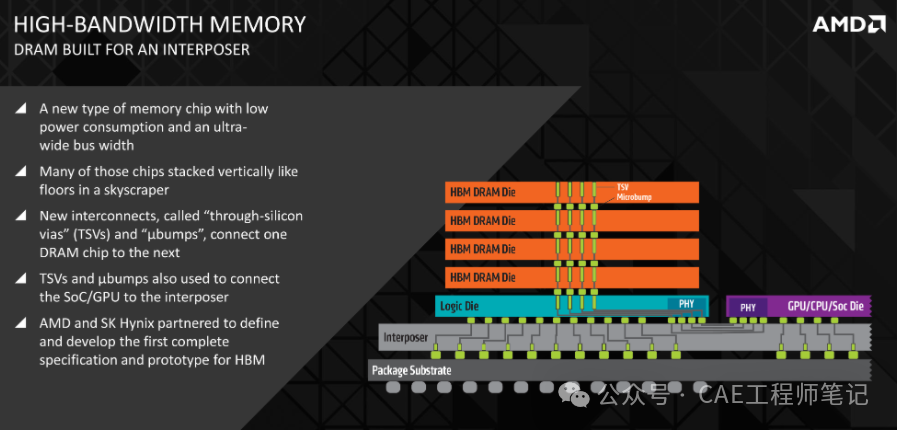

HBM的結構

當代電子計算機的性能表現依賴于 CPU 和 DRAM 的協同配合,在計算機架構中,計算處理單元根據指令從內存中讀取數據,完成計算處理后將數據存回內存。目前主流 CPU 的主頻高達 5GHz,而 DRAM內存性能取決于電容充放電速度以及 DRAM 與 CPU之間的接口帶寬。在高性能計算、數據中心、AI 應用中,頂級高算力芯片的數據吞吐量峰值在數百TB/s級別,但主流 DRAM 內存或顯存帶寬一般為幾GB/s到幾十GB/s量級,與TB/s量級還有較大差距。DRAM 內存帶寬已經成為了制約計算機性能發展的重要瓶頸,即所謂阻礙性能提升的內存墻。

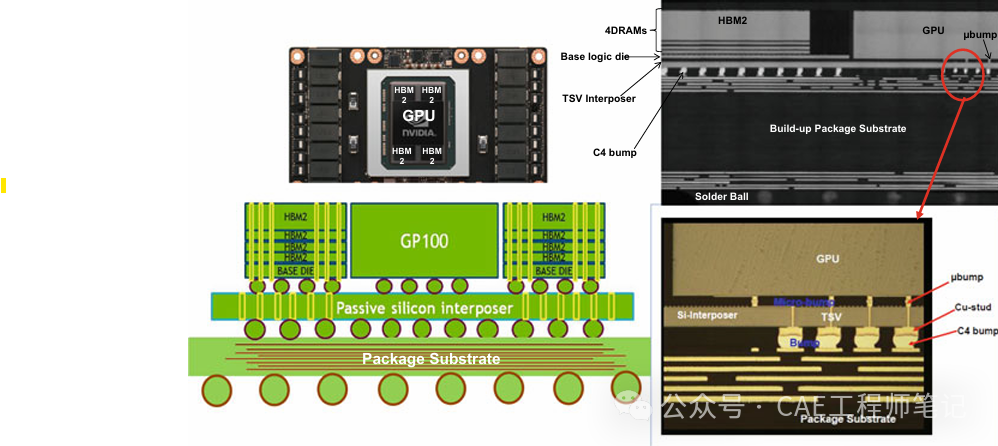

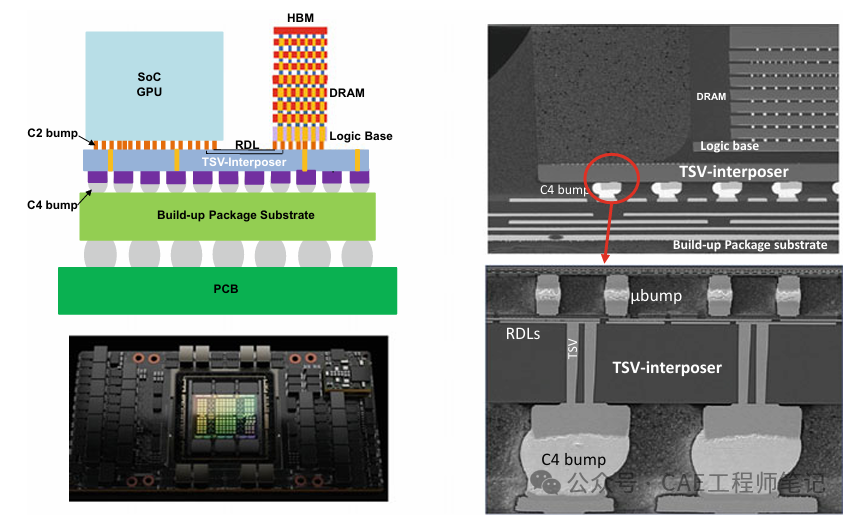

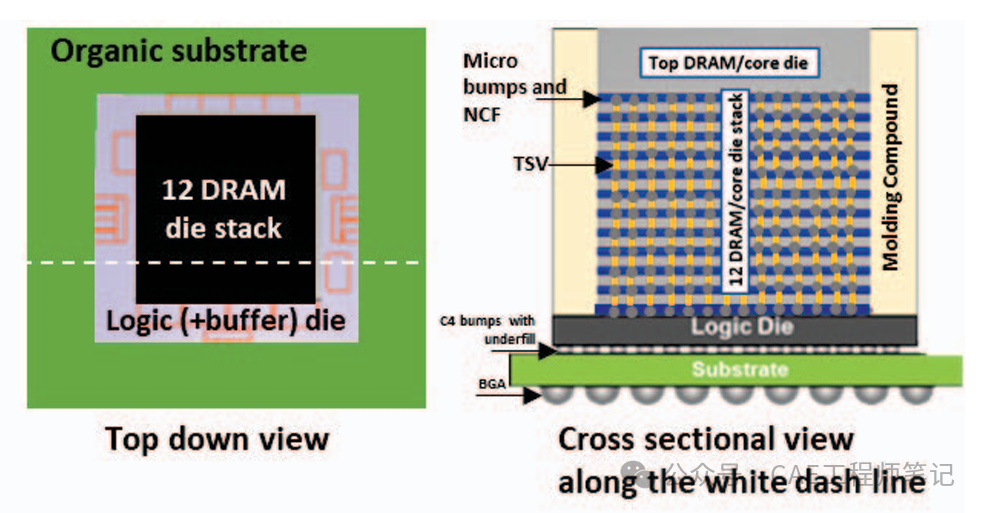

HBM 堆疊結構如上圖所示,包含多層 DRAM 芯片和一層基本邏輯芯片。4層或8層甚至更多層數的 DRAM 芯片以堆疊形式整合在一起,不同 DRAM 芯片之間以及 DRAM 芯片與邏輯芯片之間用 TSV 和微凸塊技術實現通道連接。每個 HBM DRAM 芯片可通過多達 8 條通道與外部相連,每個通道可單獨訪問1 組 DRAM 陣列,通道間訪存相互獨立。邏輯芯片可控制 DRAM 芯片,并提供與控制器芯片連接的接口,主要包括測試邏輯模塊和 PHY 模塊,其中 PHY 接口通過中間介質層與 CPU/GPU/SoC 直接高速連通,直接存取端口提供 HBM 中多層 DRAM 芯片的測試通道。中間介質層通過微凸塊連接到封裝基板,從而形成 SiP 系統。

HBM 堆棧沒有以外部互連線的方式與信號處理器芯片連接,而是通過中間介質層緊湊而快速地連接,同時 HBM 內部的不同 DRAM 采用 TSV 實現信號縱向連接,HBM 具備的特性幾乎與片內集成的RAM 存儲器一樣。

HBM 具有可擴展更大容量的特性。HBM 的單層DRAM芯片容量可擴展。HBM通過4層、8層以至12層堆疊的 DRAM 芯片,可實現更大的存儲容量。HBM可以通過 SiP 集成多個 HBM 疊層 DRAM 芯片,從而實現更大的內存容量。

HBM 由于采用了 TSV 和微凸塊技術,DRAM 裸片與處理器間實現了較短的信號傳輸路徑以及較低的單引腳I/O速度和I/O電壓,使 HBM 具備更好的內存功耗能效特性。

HBM 將原本在 PCB 板上的DDR 內存顆粒和 CPU 芯片一起全部集成到SiP 里,因此 HBM 在節省產品空間方面也更具優勢。

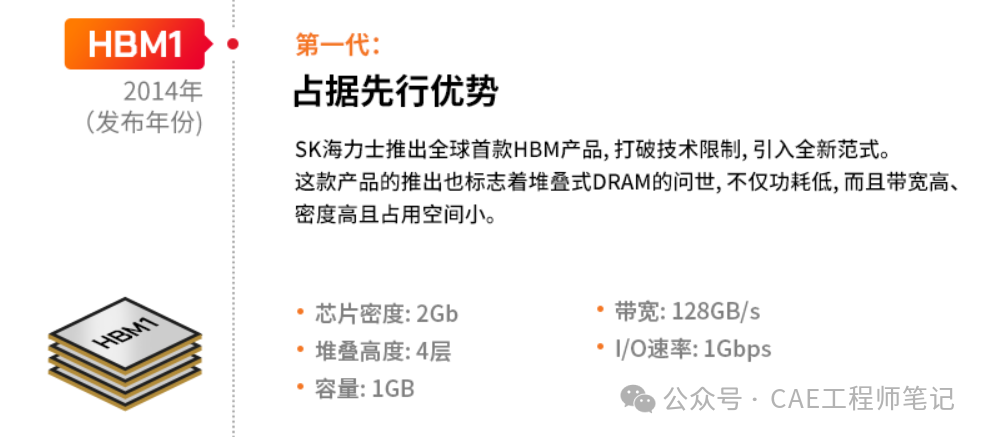

從 HBM1 到 HBM4 的技術發展

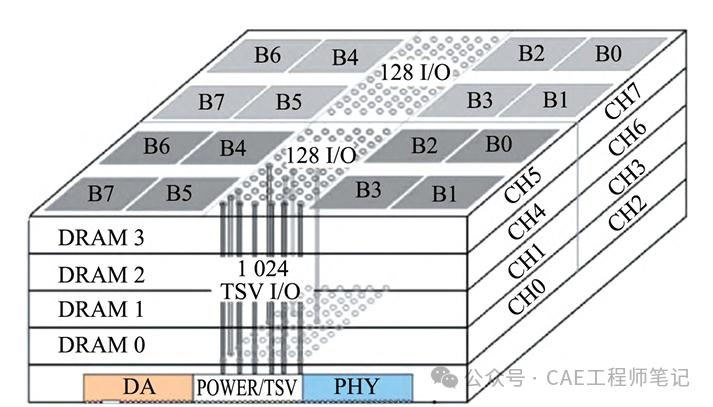

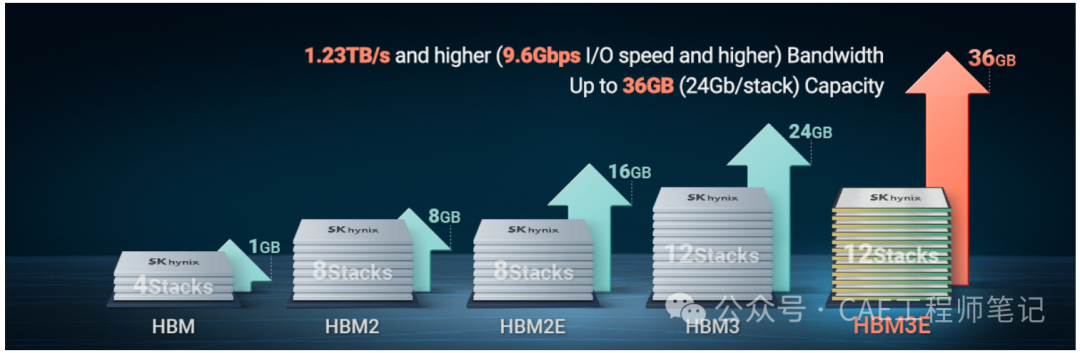

2013 年 10 月,JEDEC 發布了第一個 HBM 標準JESD235。JESD235 標準定義了具有 1024bit 接口和單引腳 1Gbit/s 數據速率的 HBM1 存儲芯片,該芯片堆疊了 2個或4個 DRAM,HBM1 堆疊 DRAM 架構如下圖所示,在基本邏輯芯片上,每個 DRAM 芯片具有 2個128bit 通道,共有8個陣列(B0~B7),最多支持 8個128bit 通道(CH0~CH7),總帶寬為128GB/s。每個通道實質上是具有 2n 預取架構的 128 bit DDR 存儲器接口,主要包括128 bit數據、8 bit 行命令地址和 6bit 列命令地址、源同步時鐘、校驗、數據屏蔽等信號,還包括復位、IEEE1500 測試端口和電源等公共信號。訪存的讀、寫操作過程基本與DDR存儲器芯片相同。HBM1 芯片具備半獨立的行、列命令接口,支持讀、寫命令與其他命令并行執行,增加了命令接口帶寬,提高了訪存性能。

2014年,SK Hynix 與 AMD 聯合開發了全球首款 HBM 產品。HBM1 的工作頻率約為 1600Mbps,漏極電源電壓為 1.2V,芯片密度為 2Gb。HBM1 的帶寬高于 DDR4和GDDR5 產品,同時以較小的外形尺寸消耗較低的功率,更能滿足 GPU 等帶寬需求較高的處理器。AMD 采用 HBM1 構建了其GPU 系統封裝和 RadeonR9Fury/R9Nano 視頻卡。

2018 年 11 月,JEDEC 在 JESD235A 的基礎上發布了 JESD235B 標準,即HBM2 技術。HBM2 充分融入了I/O高帶寬存儲技術、TSV工藝,支持最多12層的TSV堆疊,單片容量達到 16Gbit,使用 1024bit 總線,分成 8個相互獨立的 128bit 通道,單引腳數據速率提升到 2.4Gbit/s,總帶寬達到 307GB/s。HBM2 可以在全帶寬下支持 2層、4層、8層和12層的 TSV堆棧,從而使系統在容量要求方面具有靈活性,堆棧容量為1GB和24GB。

相對于 SK Hynix 主導研發的 HBM1 存儲芯片,三星、鎂光等公司也都推出HBM2產品,且三星更為領先。

2020 年 1 月,JEDEC 更新發布 HBM 技術標準JESD235C,并于 2021 年 2 月更新為 JESD235D,以支持增加的帶寬和容量,即 HBM2E。按照HBM2E 技術規范,單片最大容量為 16Gbit,支持 2層、4層、8層和12層的 TSV 堆棧,無標準高度限制,最大堆棧容量為 24GB,單引腳的數據傳輸速率提升到 3.2Gbit/s,匹配 1024bit 總線,單堆棧理論最大帶寬為410GB/s。

2020 年,三星推出 Flashbolt HBM2E 內存,堆疊 8個 16Gbit DRAM 芯片,使用 TSV 技術實現 8 芯片堆棧配置互連。

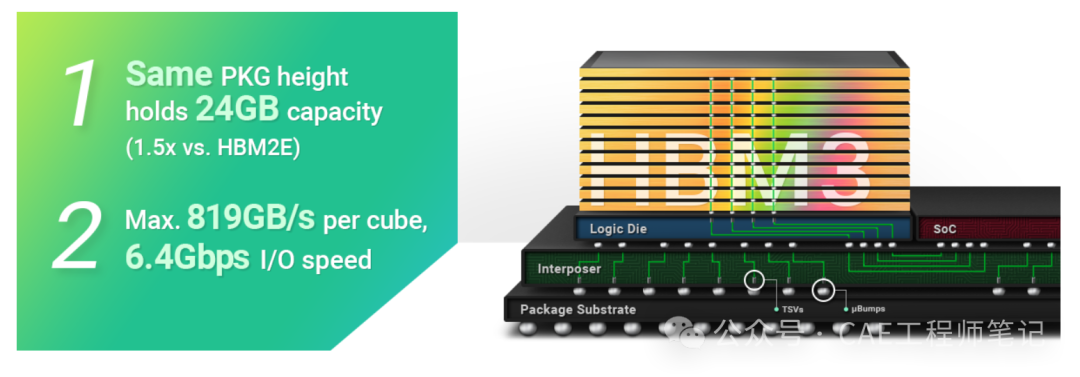

2022 年 1 月,JEDEC 發布了 HBM3 高帶寬內存標準 JESD238,即第四代 HBM 技術。HBM3在帶寬、通道、存儲密度、可靠性、能效等層面進行了擴充升級。定義了高達 6.4Gbit/s的數據傳輸速率,相當于819GB/s。將獨立通道的數量從 HBM2 的8個增加到16個。支持4層、8層和12層 TSV 堆棧,并為未來擴展至 16層TSV堆棧做好了準備,支持8~32Gbit的單層存儲容量,堆棧容量為 4~64GB。HBM3 引入了 ECC 技術,支持實時錯誤報告,滿足更高級平臺的可靠性、可用性和可維護性需求。I/O電壓降低至1.1V,能效進一步提升。

在 HBM3標準推出前,SK Hynix 就推出了 HBM3內存。SK Hynix 在 2021 年 10 月開發出全球首款 HBM3,容量是 HBM2E 的1.5倍,由 12個 DRAM 芯片堆疊成,總封裝高度相同,適用于AI、HPC等容量密集型應用。如下圖所示,Nvida H100 是世界上第一個正式使用 HBM3 技術的芯片。

目前,JEDEC 即將發布 HBM4 標準,與 HBM3 相比,HBM4 將每個堆棧的通道數增加一倍,并且物理占用空間更大。為了支持設備兼容性,該標準確保單個控制器可以在需要時同時與 HBM3 和 HBM4 配合使用。不同的配置將需要不同的中介層來適應不同的封裝。HBM4 將指定 24 Gb 和 32 Gb 層,并可選擇支持 4 層、8 層、12 層和 16 層 TSV 堆棧。

HBM 的迭代和制造已經開啟競速模式。有消息稱,為了配合英偉達的新品發布節奏,SK Hynix 原計劃 2026 年量產的 HBM4,將提前至 2025 年下半年量產,采用臺積電 3nm 制程。三星也被傳出計劃在 2025 年年底完成 HBM4 開發后立即開始大規模生產,目標客戶包括微軟和Meta。

HBM 3D 封裝仿真

下圖所示為 CASE 中模擬的單個 3D 堆疊封裝 HBM。有 12 個 DRAM 芯片堆疊在邏輯芯片的頂部。基礎邏輯芯片頂部有模塑料,圍繞著 12 個 DRAM 芯片堆棧,單個 HBM 通過 C4 凸塊或帶有底部填充的銅柱微凸塊連接到有機基板上。有機基板具有多層有機堆積膜和 Cu 層,BGA 焊球位于有機基板的底部,用于 PCB 表面貼裝。

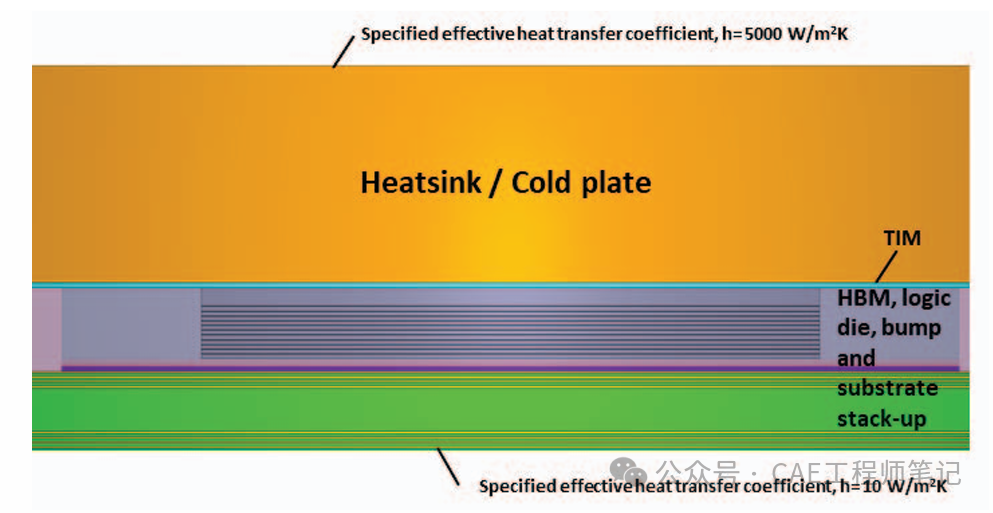

穩態熱仿真使用 Cadence 的 Celsius Electronic Cooling 工具進行設置和執行。

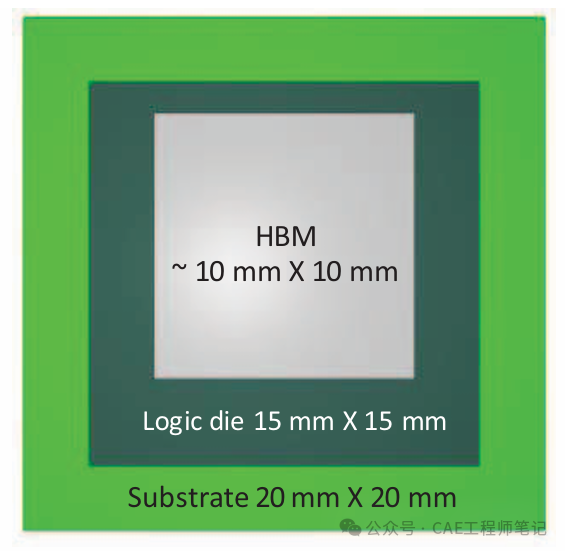

如下圖所示,邏輯芯片尺寸為 15×15 mm,在長度和寬度上比 HBM 芯片尺寸大 5 mm。HBM 芯片堆棧僅略微遠離邏輯芯片頂部的中心。TIM 材料直接連接到 HBM 芯片堆棧頂部的裸芯片上,并連接到頂部的冷板上。

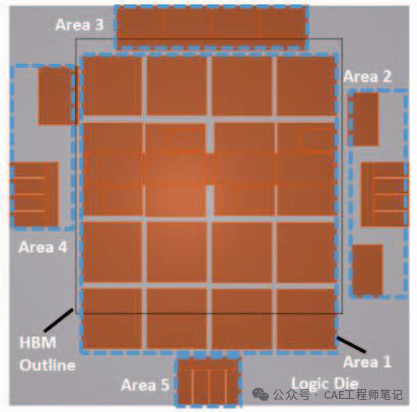

如下圖所示,邏輯芯片的總功耗為 47 W,HBM 內核芯片堆棧的總功耗為 15 W,因此封裝的總功耗為 62 W。

邊界條件根據幾何頂部和底部表面的有效傳熱系數設置,考慮到液體冷卻,冷板頂部的有效傳熱系數為 5000 W/m2K,液體入口溫度為 32度,基板底部為 10 W/m2K。

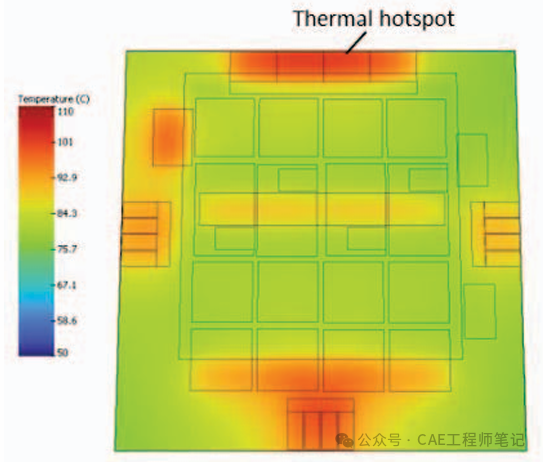

熱仿真有助于定位邏輯芯片內部的熱點。如下圖所示,熱點出現在邏輯芯片的邊緣,這主要是因為,與中心區域相比,邊緣區域在較小的區域集中了更多的功率,并且在中心區域,HBM 堆棧通過直接傳導到連接到冷板的 TIM 帶走熱量,然而,對于邊緣,傳導路徑主要通過不提供高導熱性的成型材料。

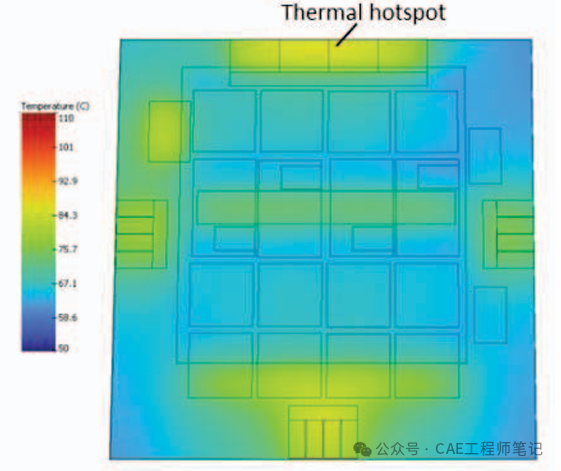

如下圖所示,將冷板頂部的傳熱系數增加到 10000 W/m2K 后,熱點溫度降低了 15.74%,熱點仍然出現在邊緣。

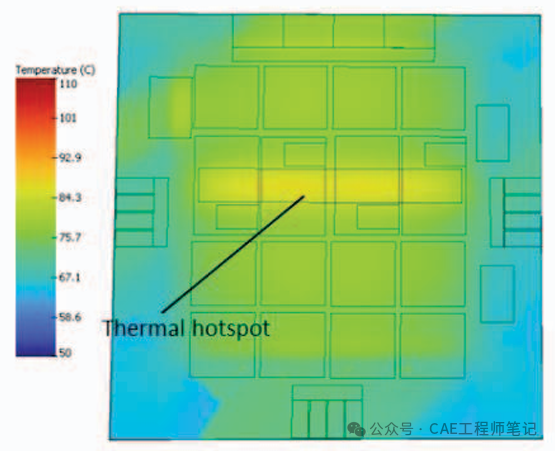

如下圖所示,在邏輯芯片頂部添加dummy die有助于將溫度降低 14.75%,并使溫度更均勻地分布在邏輯芯片上,HBM 下方的區域比其他區域略熱。

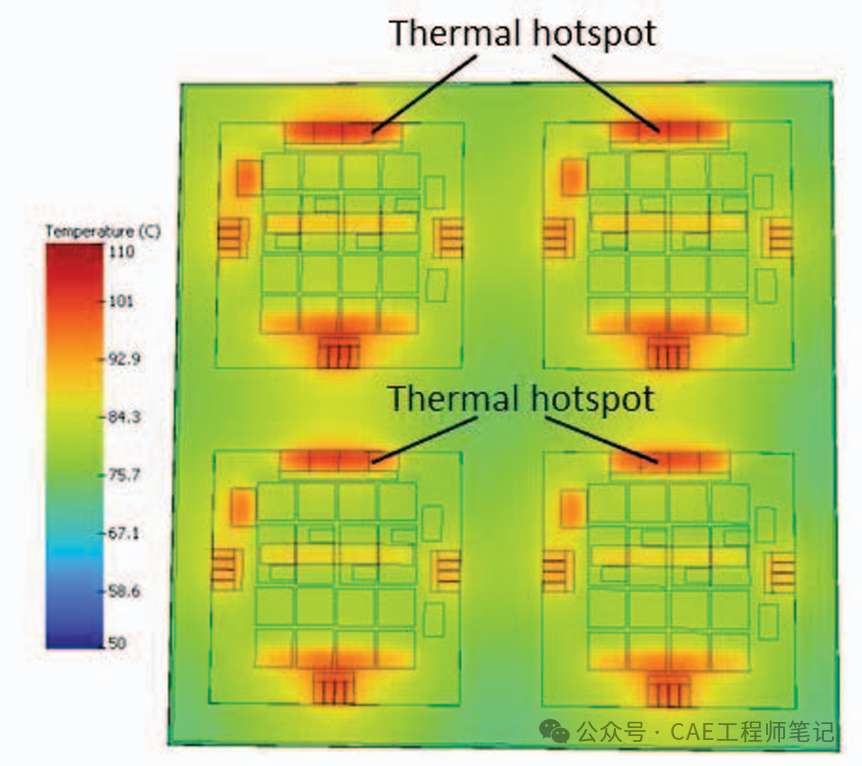

如下圖所示,在四個 HBM 的情況下,熱點仍然出現在邏輯芯片的邊緣,但與一個 HBM 的情況相比,熱點的絕對溫度實際上降低了 1%。這是因為該封裝的基板、TIM 和冷板尺寸較大,從邏輯芯片帶走了更多的熱量。

事實證明熱仿真技術在預測熱點方面是卓有成效的,因此可以通過更新冷卻解決方案或封裝結構來提出進一步的改進方案。

-

仿真

+關注

關注

52文章

4252瀏覽量

135520 -

3D封裝

+關注

關注

8文章

139瀏覽量

27702 -

HBM

+關注

關注

1文章

409瀏覽量

15168 -

先進封裝

+關注

關注

2文章

466瀏覽量

565

原文標題:先進封裝技術(Semiconductor Advanced Packaging) - 19 HBM與3D封裝仿真

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

AD16的3D封裝庫問題?

7.2小時完成868個HBM封裝端口——Cadence Clarity 3D Solver仿真案例詳解

基于HFSS的3D多芯片互連封裝MMIC仿真設計

什么是先進封裝?先進封裝技術包括哪些技術

評論