越來(lái)越多的日常設(shè)備開(kāi)始部署生成式人工智能,市場(chǎng)對(duì)大語(yǔ)言模型和出色算力的需求也隨之日益增長(zhǎng)。Yole Group在2024年OCP區(qū)域峰會(huì)的演講過(guò)程中表示:“對(duì)于訓(xùn)練參數(shù)達(dá)到1750億的GPT-3,我們估計(jì)需要6000到8000個(gè)A100 GPU歷時(shí)長(zhǎng)達(dá)一個(gè)月才能完成訓(xùn)練任務(wù)。”不斷提高的HPC和AI計(jì)算性能要求正在推動(dòng)Multi-Die設(shè)計(jì)的部署,將多個(gè)異構(gòu)或同構(gòu)裸片集成到一個(gè)標(biāo)準(zhǔn)或高級(jí)封裝中。為了快速可靠地處理AI工作負(fù)載,Multi-Die設(shè)計(jì)中的Die-to-Die接口必須兼具穩(wěn)健、低延遲和高帶寬特性,最后一點(diǎn)尤為關(guān)鍵。本文概述了利用Multi-Die設(shè)計(jì)的AI數(shù)據(jù)中心芯片對(duì)40G UCIe IP的需求。

高帶寬Die-to-Die接口用例

AI應(yīng)用正在給半導(dǎo)體行業(yè)帶來(lái)新的挑戰(zhàn)。為支持深度學(xué)習(xí)和機(jī)器學(xué)習(xí)算法的海量數(shù)據(jù)處理任務(wù),對(duì)更大帶寬的需求不斷增加,特別是對(duì)于計(jì)算和網(wǎng)絡(luò)應(yīng)用。這些AI應(yīng)用對(duì)于Die-to-Die接口提出了不同的要求。本文以100Tb網(wǎng)絡(luò)交換機(jī)和AI加速器為例。

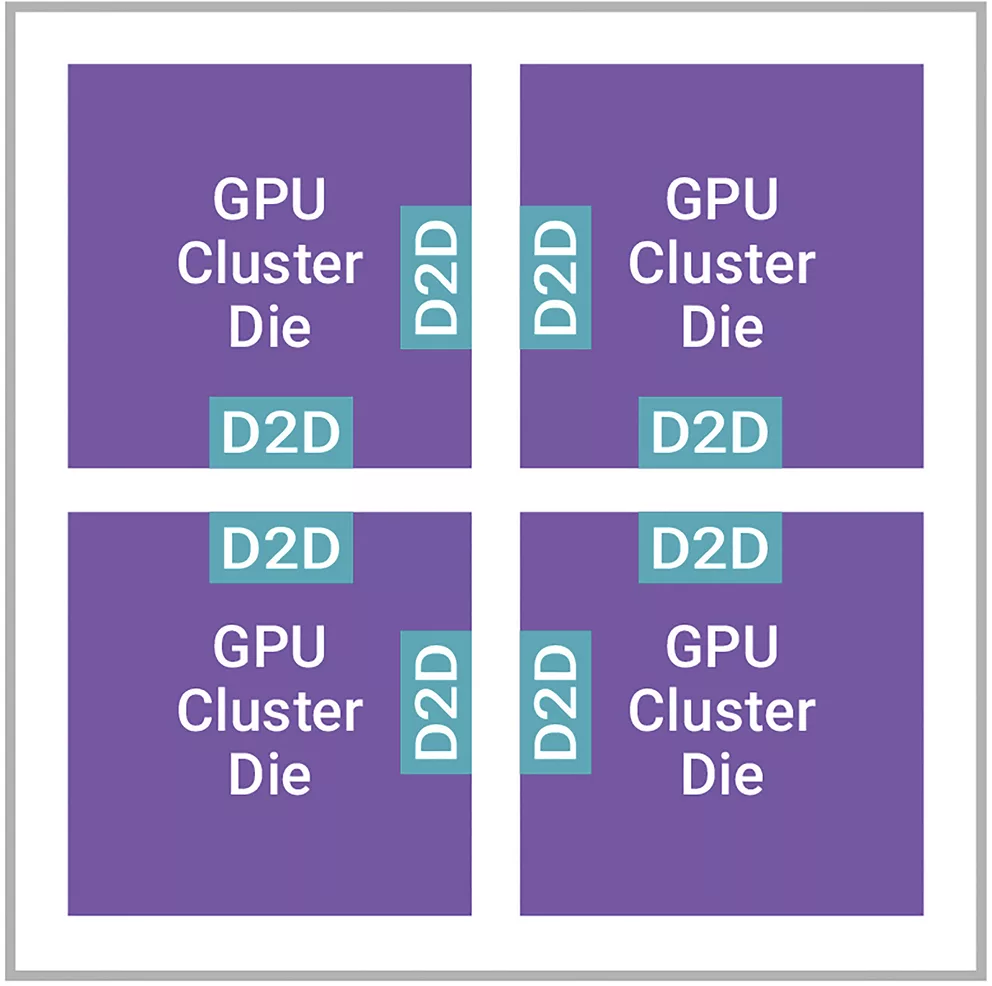

圖1為100Tb交換機(jī)示例,該交換機(jī)可用于AI數(shù)據(jù)中心,采用橫向擴(kuò)展方法來(lái)處理跨數(shù)據(jù)中心的海量數(shù)據(jù)。橫向擴(kuò)展方法在機(jī)器協(xié)同工作的網(wǎng)絡(luò)中將工作負(fù)載分配到多臺(tái)服務(wù)器上。交換機(jī)SoC不斷擴(kuò)展,正在接近尺寸極限,因此它被分割成更小的裸片,以提高邊緣使用率。在這種情況下,Die-to-Die接口通過(guò)高速以太網(wǎng)在裸片之間以及向外界傳輸大量數(shù)據(jù),反之亦然。

▲圖1 100Tb交換機(jī)的裸片分割用例片

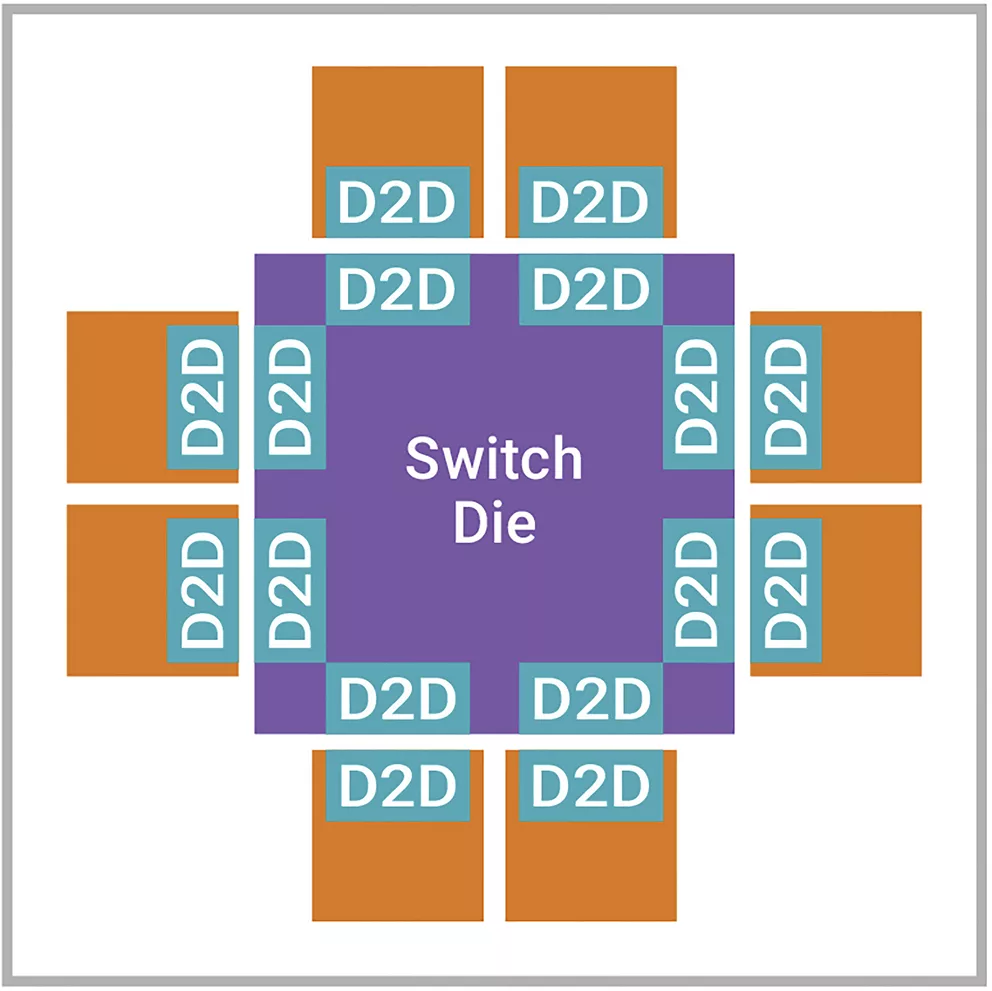

類似Google張量處理單元這樣的AI加速器采用Multi-Die設(shè)計(jì),為PCIe和以太網(wǎng)等接口配備單獨(dú)的計(jì)算裸片和IO裸片。此類AI處理器在更主流的技術(shù)工藝上使用IO裸片來(lái)節(jié)省成本,并在更先進(jìn)的技術(shù)工藝上使用計(jì)算裸片來(lái)提高性能和能效,從而充分發(fā)揮Multi-Die設(shè)計(jì)的優(yōu)勢(shì)。一些AI加速器使用圖3所示的裸片分割方法,需要高帶寬Die-to-Die接口來(lái)無(wú)縫傳輸裸片之間的數(shù)據(jù)。

▲圖2 使用AI加速器的裸片分割用例

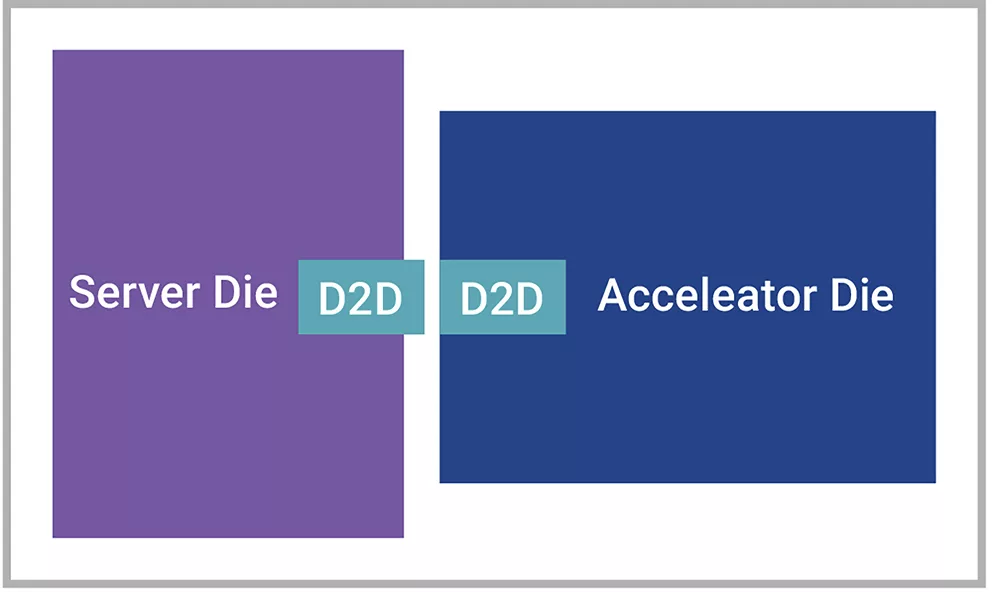

另一個(gè)示例是裸片連接用例,其中主服務(wù)器裸片或處理器連接到AI加速器裸片,以便執(zhí)行可分流到特定功能加速器的任務(wù)。在這種用例中,Die-to-Die接口用于在需要時(shí)將數(shù)據(jù)從服務(wù)器裸片發(fā)送到加速器裸片,而無(wú)需在高帶寬下運(yùn)行。此類用例使用標(biāo)準(zhǔn)封裝技術(shù)(如有機(jī)襯底),復(fù)雜性較低。許多邊緣AI和移動(dòng)應(yīng)用都使用此類用例。

▲圖3 裸片連接用例

利用40G UCIe IP為Die-to-Die連接提供最大帶寬

UCIe規(guī)范已成為Die-to-Die連接的事實(shí)標(biāo)準(zhǔn),確保裸片之間的互操作性、低延遲和實(shí)時(shí)數(shù)據(jù)傳輸。得益于UCIe,100Tb交換機(jī)和AI加速器等使用Multi-Die設(shè)計(jì)技術(shù)在標(biāo)準(zhǔn)封裝和高級(jí)封裝下實(shí)現(xiàn)了帶寬效率更高。作為通用芯粒互聯(lián)產(chǎn)業(yè)聯(lián)盟(UCIe Consortium)的成員,新思科技在其當(dāng)前經(jīng)驗(yàn)證的UCIe IP基礎(chǔ)上,推出了40G UCIe IP解決方案,可提供比UCIe規(guī)范高25%的帶寬,而不會(huì)影響能效或面積。

40G UCIe PHY符合新的UCIe規(guī)范,實(shí)現(xiàn)了各種功能,可確保Die-to-Die鏈路可靠性和質(zhì)量。PHY具有全面的可測(cè)性設(shè)計(jì)(DFT)功能,可用于已知良好裸片和生產(chǎn)測(cè)試,從而提高了可測(cè)試性。嵌入式信號(hào)完整性監(jiān)視器(SIMs)可監(jiān)測(cè)Die-to-Die鏈路的任務(wù)模式。監(jiān)視器可以持續(xù)分析Die-to-Die信號(hào)質(zhì)量,并在任務(wù)模式下執(zhí)行校正措施,以實(shí)現(xiàn)可靠的通信。

PHY在2GHz頻率下支持高達(dá)128B的接口寬度,可以利用整個(gè)PHY的帶寬。對(duì)于必須以較低時(shí)鐘頻率運(yùn)行的系統(tǒng),它還在1GHz頻率下支持更寬的256B接口。40G UCIe控制器支持不同的接口選項(xiàng),例如流式傳輸、CXS、AXI,以及PCIe、CXL、AXI和CHI C2C等協(xié)議,以在Die-to-Die鏈路上運(yùn)行標(biāo)準(zhǔn)化數(shù)據(jù)。

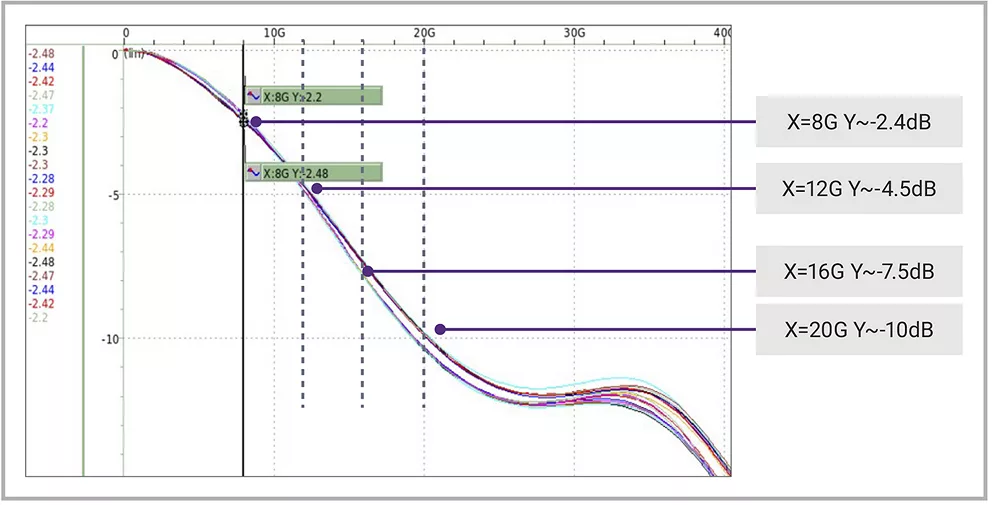

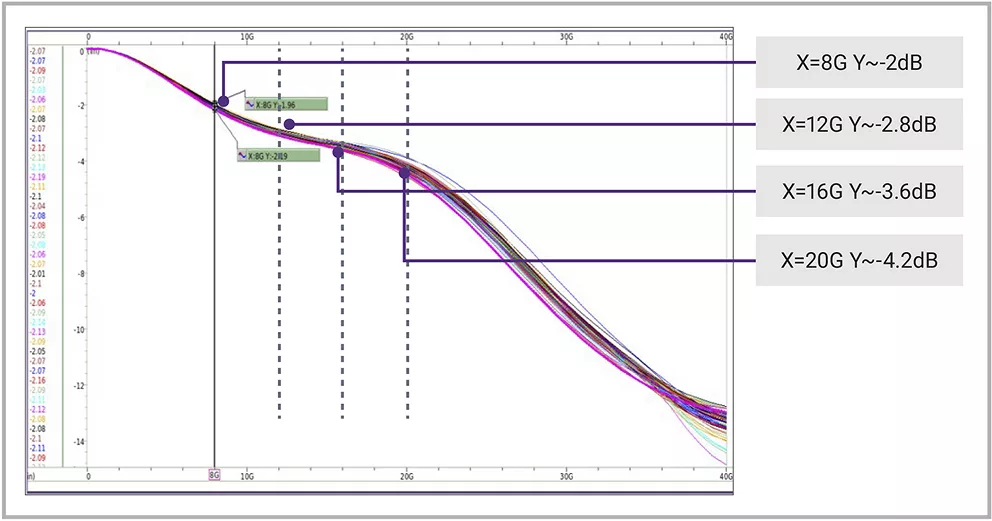

雖然更高的數(shù)據(jù)速率有助于AI應(yīng)用實(shí)現(xiàn)高帶寬效率并滿足數(shù)據(jù)處理要求,但也帶來(lái)了設(shè)計(jì)挑戰(zhàn)。開(kāi)發(fā)者必須精心設(shè)計(jì)通道規(guī)格,避免更高的插入損耗和串?dāng)_,以實(shí)現(xiàn)更優(yōu)性能。速度較低時(shí),可能不需要對(duì)發(fā)射器(TX)進(jìn)行均衡處理。但在速度較高時(shí),為了達(dá)到所需的信道性能,就需要進(jìn)行TX均衡,比如使用2抽頭前饋均衡(FFE)。此外還需要采用更強(qiáng)大的接收器(RX)均衡技術(shù),例如1抽頭決策反饋均衡(DFE)及連續(xù)時(shí)間線性均衡(CTLE)。Die-to-Die通道需經(jīng)過(guò)大量的信號(hào)完整性和電源完整性仿真,以驗(yàn)證Die-to-Die鏈路特性和性能是否符合預(yù)期。

▲圖4 16G奈奎斯特頻率下的有損信道示例

▲圖5 良好渠道設(shè)計(jì)示例

40G UCIe PHY支持新興的先進(jìn)封裝技術(shù),例如硅或RDL中介層、硅橋和RDL扇出,以及傳統(tǒng)的有機(jī)襯底封裝技術(shù)。PHY為先進(jìn)封裝技術(shù)提供高達(dá)12 Tbps/mm的總帶寬效率,為標(biāo)準(zhǔn)封裝技術(shù)提供高達(dá)1.8 Tbps/mm的總帶寬效率,同時(shí)運(yùn)行速度高達(dá)40Gbps/pin。有機(jī)襯底封裝技術(shù)雖然更為常見(jiàn)且比較實(shí)惠,但需要更多的布線層來(lái)支持IP實(shí)現(xiàn)更高速的布線。相反,先進(jìn)封裝技術(shù)可以改善布線密度,但也增加了封裝設(shè)計(jì)所面臨的挑戰(zhàn)。了解到這種復(fù)雜性,新思科技提供了用于中介層設(shè)計(jì)的3DIC Compiler平臺(tái)及UCIe-A IP參考設(shè)計(jì)。3DIC Compiler是統(tǒng)一的探索到簽核解決方案,其中包含用于自動(dòng)布線和自定義中介層設(shè)計(jì)的工具和腳本。

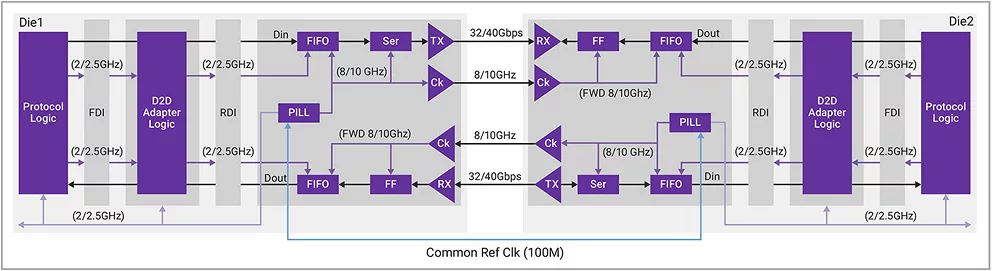

40G UCIe IP實(shí)現(xiàn)了前向時(shí)鐘架構(gòu),以簡(jiǎn)化接收器架構(gòu),從而降低功耗和延遲。其中使用了四倍速率架構(gòu),對(duì)于32 Gbps/pin速度,PHY操作頻率限制為8 GHz;對(duì)于40 Gbps/pin速度,PHY操作頻率限制為10 GHz。此外還借助嵌入式低延遲FIFO來(lái)補(bǔ)償前向時(shí)鐘和本地時(shí)鐘之間以及不同通道之間的偏差不匹配。通用的100MHz參考時(shí)鐘用作PHY鎖相環(huán)(PLL)的輸入,可生成PHY和控制器所需的所有高頻時(shí)鐘,這樣邏輯電路就無(wú)需向PHY提供高頻時(shí)鐘。圖6為40G UCIe PHY架構(gòu)。

▲圖6 UCIe PHY架構(gòu)

UCIe未來(lái)的發(fā)展道路

3D封裝具有功耗和性能優(yōu)勢(shì),正逐漸成為快速M(fèi)ulti-Die設(shè)計(jì)的優(yōu)選解決方案。

UCIe規(guī)范2.0正在促使3D封裝中的Die-to-Die連接實(shí)現(xiàn)標(biāo)準(zhǔn)化,與2D和2.5D技術(shù)相比,其帶寬更高且功耗更低。UCIe規(guī)范為3D封裝定義了以下特性:

簡(jiǎn)約的PHY架構(gòu),例如簡(jiǎn)單的逆變器/驅(qū)動(dòng)器

適合凸塊區(qū)域的電路和邏輯,這有助于實(shí)現(xiàn)較低的工作頻率和更簡(jiǎn)單的電路

較小的凸塊間距,例如幾微米

預(yù)定義的Bump-PHY的Bump圖,可簡(jiǎn)化互操作性

新思科技利用3DIO IP解決方案實(shí)現(xiàn)了3D封裝中的Die-to-Die連接。

3D封裝技術(shù)正蓬勃發(fā)展,未來(lái)幾年對(duì)更高數(shù)據(jù)速率的需求可能會(huì)越來(lái)越大。Die-to-Die接口也將持續(xù)演進(jìn),以支持更高的速度和能效。

業(yè)界首款40G UCIe IP解決方案,包括控制器、PHY和驗(yàn)證IP,提供更高算力,可滿足速度更高的基于UCIe的Multi-Die設(shè)計(jì)需求。PHY的簡(jiǎn)化架構(gòu)簡(jiǎn)化了IP集成,全面的監(jiān)控、測(cè)試和修復(fù)功能則改善了可靠性和芯片的健康狀況。新思科技走在技術(shù)發(fā)展的前沿,并將繼續(xù)部署先進(jìn)的IP來(lái)適應(yīng)千變?nèi)f化的市場(chǎng)需求。

-

數(shù)據(jù)中心

+關(guān)注

關(guān)注

16文章

4810瀏覽量

72212 -

新思科技

+關(guān)注

關(guān)注

5文章

800瀏覽量

50362 -

AI芯片

+關(guān)注

關(guān)注

17文章

1893瀏覽量

35099 -

UCIe

+關(guān)注

關(guān)注

0文章

47瀏覽量

1635

原文標(biāo)題:當(dāng) AI 芯片遇上帶寬瓶頸,看40G UCIe IP 如何打破僵局?

文章出處:【微信號(hào):Synopsys_CN,微信公眾號(hào):新思科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Maxim 40G傳輸解決方案有效降低功耗、提高數(shù)據(jù)吞吐率

請(qǐng)問(wèn)光學(xué)模塊如何進(jìn)化以滿足數(shù)據(jù)中心需求?

40G光模塊選購(gòu)指南

40G數(shù)據(jù)中心之銅纜布線

為什么25G比40G更適合數(shù)據(jù)中心市場(chǎng)?

2023是否會(huì)成為Multi-Die的騰飛之年?

芯片革命:Multi-Die系統(tǒng)引領(lǐng)電子設(shè)計(jì)進(jìn)階之路

態(tài)路小課堂丨為40G數(shù)據(jù)中心綜合布線產(chǎn)品選擇方案!

利用Multi-Die設(shè)計(jì)的AI數(shù)據(jù)中心芯片對(duì)40G UCIe IP的需求

利用Multi-Die設(shè)計(jì)的AI數(shù)據(jù)中心芯片對(duì)40G UCIe IP的需求

評(píng)論