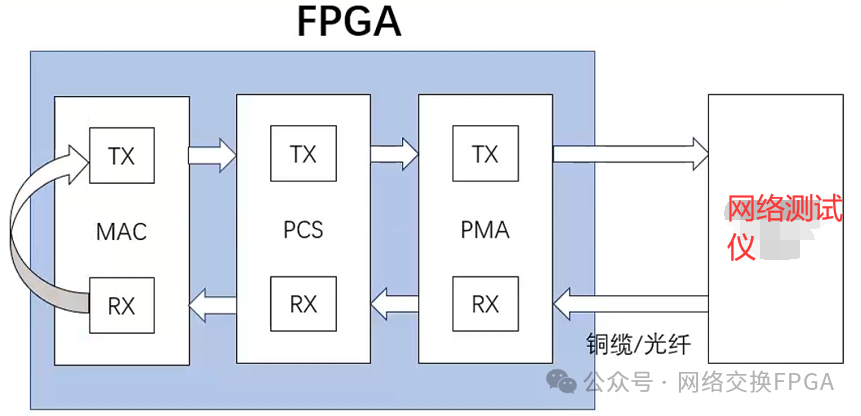

帶Serdes的高速以太網接口流片后如果功能不正常,可以采用帶有相同接口類型的FPGA進行測試定位問題。本文簡單的介紹一種通過FPGA來對基于四通道serdes的40G/10G以太網接口PMA和PCS層進行鏈路連接測試的方法,歡迎大家留言討論指導。

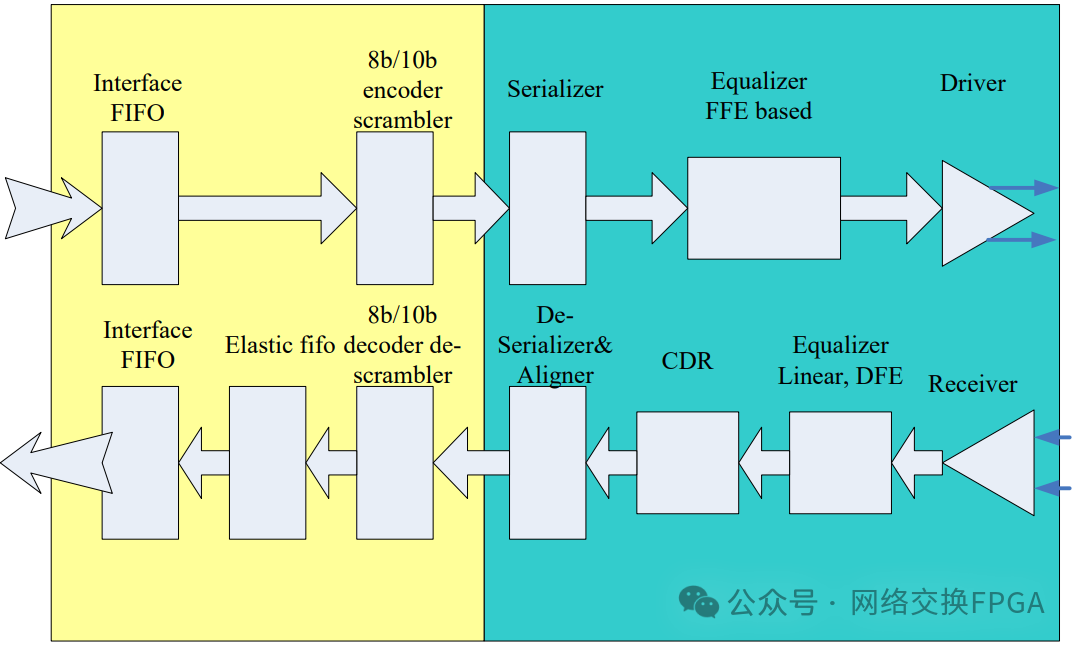

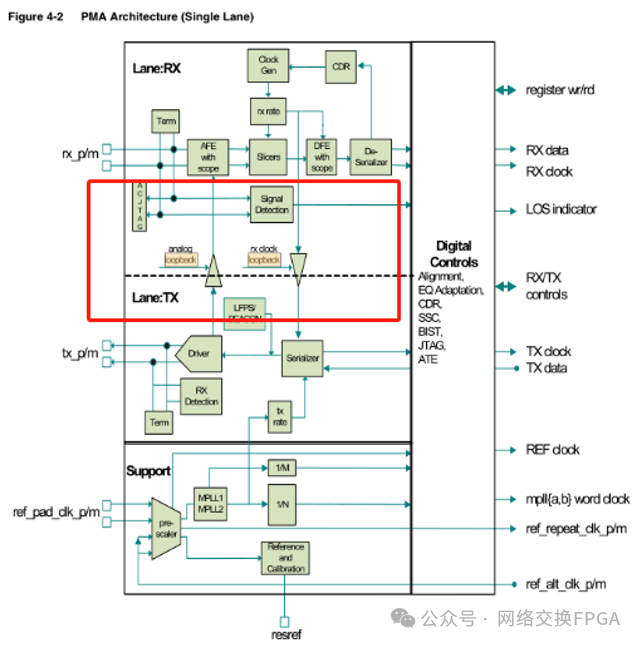

SERDES 是英文 SERializer(串行器)/DESerializer(解串器)的簡稱。它是一種時分多路復用(TDM)、點對點的通信技術,即在發送端多路低速并行信號被轉換成高速串行信號,經過傳輸媒體(光纜或銅線),最后在接收端高速串行信號重新轉換成低速并行信號。這種點對點的串行通信技術充分利用傳輸媒體的信道容量,減少所需的傳輸信道和器件引腳數目,從而減少了傳輸線之間的干擾,增大了背板傳輸距離,并且大大降低通信成本。同時帶來了諸如減少布線沖突、降低開關噪聲、更低的功耗和封裝成本等許多好處。而 SERDES 技術的主要缺點是需要非常精確、超低抖動的元件來提供用于控制高數據速率串行信號所需的參考時鐘。即使嚴格控制元件布局,使用長度短的信號并遵循信號走線限制,這些接口的抖動余地仍然是非常小。 SERDES 主要由物理介質相關( PMD)子層、物理媒介附加(PMA)子層和物理編碼子層( PCS )所組成。PMD 是負責串行信號傳輸的電氣層,PMA 負責串化/解串化,PCS 負責數據流的編碼/解碼,在 PCS 的上面是上層數字 IP 功能。一般的高速接口均是由 2 個 IP(時鐘域)組成,上層是數字 IP,一般執行接口協議相關的處理,下層為 SERDES 層,主要執行串并,并串轉換的處理。 如下圖所示,藍色背景子模塊為 PCS 層,是標準的可綜合 CMOS 數字邏輯,可以硬邏輯實現。褐色背景的子模塊是 PMA 層,是數模混合 CML/CMOS 電路,是理解 SERDES 區別于并行接口的關鍵,也是本文要討論的內容。

發送方向(Tx)信號的流向: 處理器軟邏輯(fabric)送過來的并行信號,通過接口FIFO(Interface FIFO),送給 8B/10B 編碼器(8B/10B encoder)或擾碼器(scrambler),以避免數據含有過長連零或者連一,之后送給串行器(Serializer)進行 并->串 轉換,串行數據經過均衡器(equalizer)調理,由驅動器(driver)發送出去。 接收方向(Rx)信號的流向, 外部串行信號由線性均衡器(Linear Equalizer)或判決反饋均衡器(Decision Feedback Equalizer)調理,去除一部分確定性抖動(Deterministic jitter)。CDR 從數據中恢復出采樣時鐘,經解串器變為對齊的并行信號。8B/10B 解碼器(8B/10B decoder)或解擾器(descambler)完成解碼或者解擾。如果是異步時鐘系統(plesio-synchronous system),在用戶 FIFO 之前還應該有彈性 FIFO 來補償頻差。 在測試前,可以先搭建仿真驗證環境,對FPGA和芯片版本的40G/10G接口進行仿真。

仿真目的:

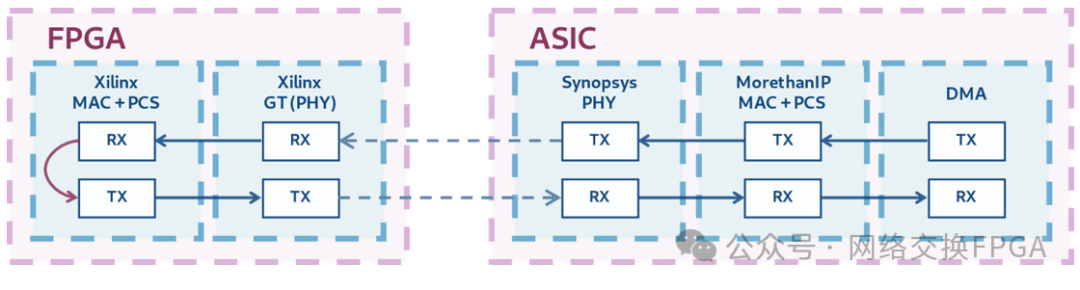

確定FPGA在10GBASE-KR與10GBASE-R模式下與ASIC連接鏈路的穩定,以及鏈路具體狀態。

連接關系與數據通路:

FPGA與ASIC兩側的PCS均顯示每個bus的四個lane進入鎖定狀態(xl_block_lock為高),但四個lane對齊的標志位xl_align_done為0。與實際測試表現一致。

通過仿真進行異常定位:通過FPGA側的PCS RTL信號追查鏈路無法對齊、aligndone標志無法產生的原因。

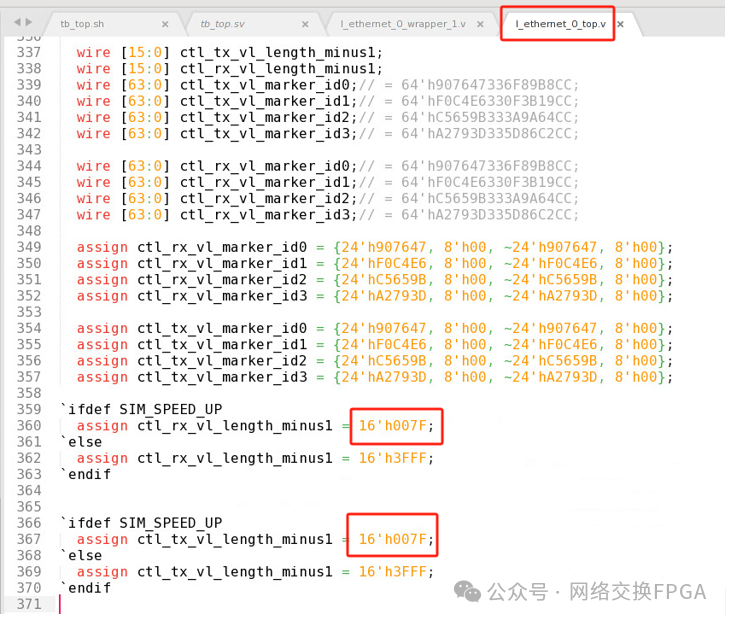

在FPGA的PCS的對齊邏輯中發現其檢查對齊標志(alignmarker)之前,需要lane保持同步鎖定一定時間,該時間由代碼如下位置指定:

(1)當仿真環境未添加SIM_SPEED_UP宏定義,仿真中PCS檢查align marker的時間間隔設置為3FFF(16383)個block,RTL仿真跑到這個時間間隔需要花費極大的時間。另外觀察到,FPGA一側添加SIM_SPEED_UP宏定義后,上述參數為3F(原代碼中),該參數與ASIC中PCS的vl_intvl寄存器配置的7F值非常像,而且結合PCS手冊描述和網表反推,vl_intvl同樣是與對齊標志間隔相關的寄存器,該寄存器在實際上板、仿真時應當設置不一樣的值:對于滿足802.3的40GBASE-R標準的情況,需要設置為16383,對于仿真,需要減小該數值以縮短仿真的鏈路對齊時間。

(2)在FPGA中打開SIM_SPEED_UP宏定義進行仿真。FPGA側對齊標志間隔參數(ctl_Xx_vl_length_minus1)設置為3F,ASIC的vl_intvl寄存器保持7F值。進行仿真,追查對齊相關信號,找到FPGA側PCS查找align marker的邏輯,PCS找到第一個marker后,在下一個應當檢測到marker的位置沒有繼續找到marker,因此PCS的連接狀態從ALIGNING(對齊中)和IDLE(失去對齊)中反復跳轉,無法進入ALIGNED(已對齊)狀態。該現象直接說明了對端(ASIC側)的PCS在鏈路中插入align marker的間隔與FPGA側的不一致,因此兩設備無法建立對齊鏈路。

(3)將仿真中的FPGA的ctl_Xx_vl_length_minus1與ASIC的vl_intvl寄存器設置為同樣的值(7F),讓兩側的PCS在相同的7F個block間隔后插入或檢測align marker。仿真觀察到FPGA的PCS對齊狀態機成功進入ALIGNED狀態,表明4個lane的對齊基本條件能夠滿足。結合以上仿真結果,可以得知之前ASIC側的vl_intvl寄存器值配置為7F為快速仿真設置,與802.3要求的3FFFF(16384)不符,實際芯片測試中需要將vl_intvl寄存器配置為3FFF進行測試。

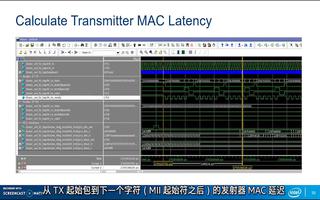

40G線速仿真:通常在ASIC IP核中,PHY和MAC接口處寄存器用來配置是否工作在40G線速狀態,如MAC沒有配置tx_ipg_comp_reg寄存器,該寄存器用于補償PCS插入對齊標志造成的40G滿速時的線速損耗,那么MAC就無法運行在40G線速模式。此時,對齊標志占比1/16384,導致損失速率的實際速率為0.999938*40Gbps,實際芯片測試中,最高速率能夠達到0.999928*40Gbps不丟幀,該比例與對齊標志損耗接近。若配置相關寄存器后,則鏈路中對齊標志就會刪除,此時芯片實際測試可以跑滿40G線速。如下視頻是A芯片實際測試40G打流99%不丟幀的視頻:

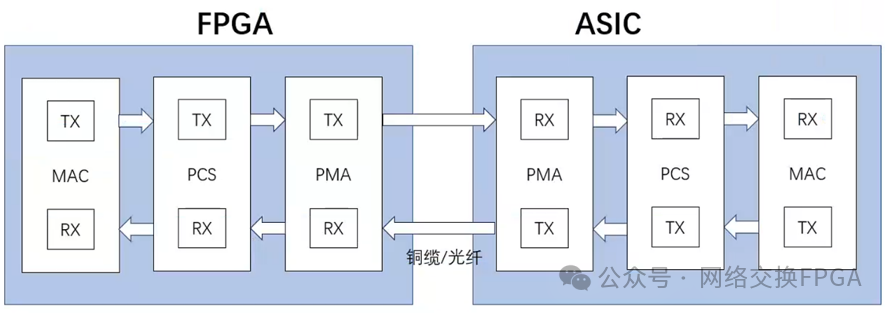

由于仿真無法百分百跟真實場景對應,尤其是PMAC側數模混合部分,在仿真環境中往往被簡化模型替代,仿真通過,但實際上板或流片則可能會有問題。以下介紹FPGA與ASIC實際上板測試情況。

1、硬件連接方式

使用銅纜或者光纖將FPGA和ASIC側的光口進行連接。ASIC側的IP需要根據需求或者手冊配置成正常工作模式。FPGA側只用例化相關IP,并進行管腳約束。FPGA側可使用IP參考第二部分。

使用上述方式進行監測時首先要保證FPGA側正常工作。可以通過連接網絡測試儀進行打流回環來驗證。如下圖所示。本文針對40G/10G高速以太網接口利用FPGA對同樣接口速率的40G/10G以太網接口serdes和PCS層進行互連互通,進而對流片后的serdes芯片進行調試(也可能是芯片的serdes或PCS工作模式配置不正確)或故障定位。FPGA側40G/10G可以參考xilinx官方的兩個文檔pg211和ug578,其中pg211介紹40g/50g的MAC+PCS等相關的知識點,ug578介紹GTY的知識,具體可以到官網下載,學習查看。FPGA側40G/10G接口工作是否正常可以參考文章:UltraScale+FPGA中Serdes的多lane對齊異常解決方案。

同時由于PCS的工作機制,其必須在鏈路正常穩定的情況下才能對數據進行正常傳輸。所以如果鏈路有問題,PCS部分會有相關寄存器反映當前狀態。具體寄存器或者內部信號參考第三部分。

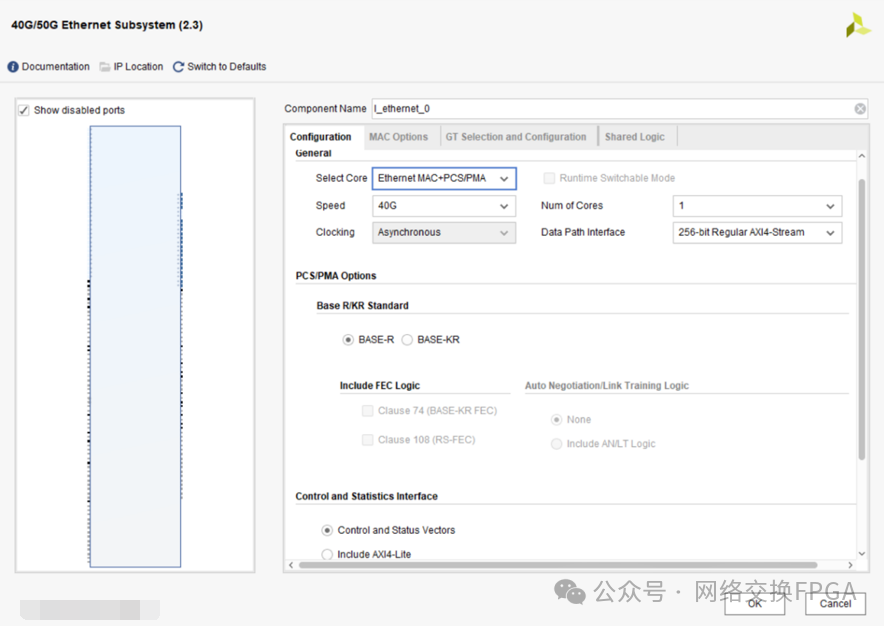

2、FPGA使用IP

1)對端是40G以太網接口(4lane 40)

示例工程如下:(略)

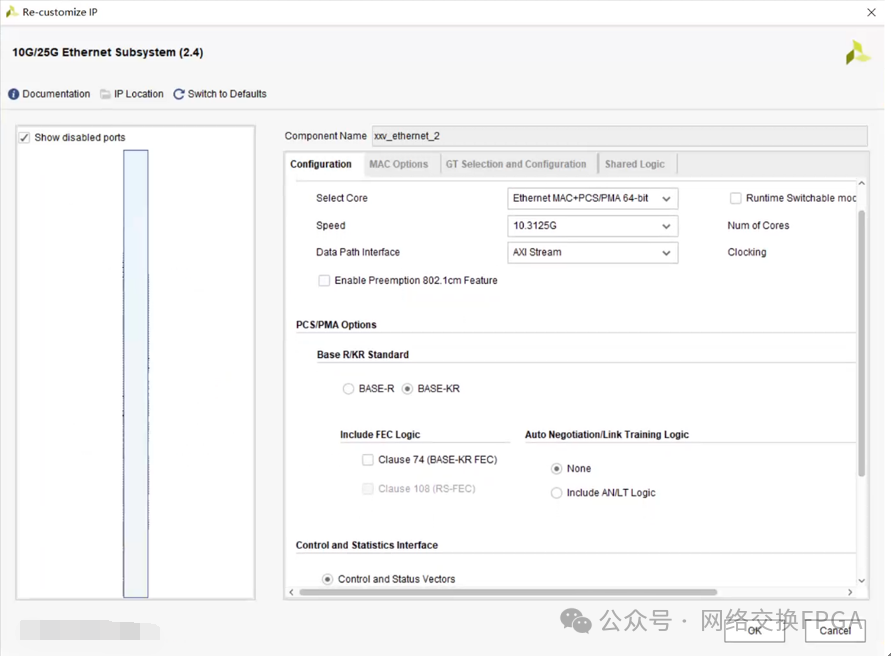

2)對端是10G以太網接口(單lane 10)

3)對端是10G以太網接口(4lane 10)

3、信號抓取說明

1)如果使用40G/50G Ethernet Subsystem或者10G/25G Ethernet Subsystem,直接監測相關狀態寄存器。

| RX PCS通道對齊狀態 | ||

| 寄存器 | 含義 | 備注 |

| stat_rx_synced[3:0] | 字邊界已同步。這些信號用于指示 PCS 通道是否已完成字邊界同步。值為 1 表示對應 PCS 通道已實現字邊界同步,并且已接收到 PCS 通道標記。對應于第 82.3 條中所定義的管理數據輸入/輸出 (MDIO) 寄存器位 3.52.7:0 和 3.53.11:0。此輸出對電平敏感。 | |

| stat_rx_synced_err[3:0] | 字邊界同步錯誤。這些信號用于指示在相應的 PCS 通道內進行字邊界同步期間,是否發生錯誤。值為 1 表示由于同步報頭成幀位錯誤或者從未收到 PCS 通道標記,對應 PCS 通道已丟失字邊界同步。此輸出對電平敏感。 | |

| stat_rx_mf_len_err[3:0] | PCS 通道標記長度錯誤。這些信號用于指示相應通道內是否發生了 PCS 通道標記不匹配(即,接收到的 PCS 通道標記間隔字數并非 ctl_rx_vl_length_minus1)。值為 1 表示對應通道接收 PCS 通道標記的間隔錯誤。它將保持高電平,直至消除錯誤狀況為止。 | |

| stat_rx_mf_repeat_err[3:0] | PCS 通道標記字錯誤。這些信號用于表示在相應通道內檢測到構成的 PCS 通道標記字錯誤。值為 1 表示發生了錯誤。此輸出將脈沖 1 個時鐘周期,以指示錯誤狀況。脈沖可在不間斷的連續周期內發生。 | |

| stat_rx_mf_err[3:0] | 當 stat_rx_aligned 值為 1 時,表示全部通道都已對齊/去歪斜,并且接收器已準備好接收包數據。 | |

| stat_rx_aligned_err |

當 stat_rx_aligned_err 值為 1 時,將發生以下 2 種情況之一: ? 通道對齊經多次嘗試后失敗。 ? 通道對齊已丟失(stat_rx_aligned 斷言有效,隨后被取反) |

|

| stat_rx_misaligned | 對齊錯誤。此信號表示通道對齊器并未在所有通道上都接收到期望的 PCS 通道標記。在所有通道上都至少接收到 1 個 PCS 通道標記并且至少接收到 1 個錯誤的通道標記后,此信號才會斷言有效。此狀況的發生比錯誤晚 1 個元幀。如果從未正確接收到任何通道標記,則此信號不會斷言有效。通道標記錯誤通過對應的 stat_rx_mf_err 信號來指示。此輸出將脈沖 1 個時鐘周期,以指示錯誤狀況。脈沖可在不間斷的連續周期內發生。 | |

|

stat_rx_framing_err_[3:0][3:0] stat_rx_framing_err_valid_[3:0] |

這組總線旨在用于保留同步報頭錯誤記錄。每個 PCS 通道都有一對輸出。 stat_rx_framing_err_[PCSL_LANES-3:0] 輸出總線用于指示已接收到的同步報頭錯誤數量,當對應 stat_rx_framing_err_valid_[PCSL_LANES-3:0] 采樣為 1 時,此輸出總線合格(即,僅限在此情況下其值才有效)。 | |

| stat_rx_vl_number[3:0][1:0] | 每個總線所指示的特定 PCS 通道的狀態反映在特定狀態管腳上。例如,stat_rx_vlane_number_0 所指示的 PCS 通道的狀態反映在其它狀態信號的管腳 0 上。這些總線可用于檢測是否尚未找到 PCS 通道或者是否某一 PCS 通道已映射到多個狀態管腳。 | |

| stat_rx_vl_demuxed[3:0] | 在每個通道上都達成字邊界同步后,如果該總線的位為 1,則表示已正確查找到對應 PCS 通道,并且已對其正確完成逆多路復用。 | |

| stat_rx_block_lock[3:0] | 每個 PCS 通道的塊鎖定狀態。值為 1 表示對應通道已達到第 82 條中定義的塊鎖定狀態。對應于第 82.3 條中所定義的 MDIO 寄存器位 3.50.7:0 和 3.51.11:0。此輸出對電平敏感。 | |

| stat_rx_aligned | 所有 PCS 通道均已對齊/去歪斜。此信號表示是否所有 PCS 通道均已對齊并去歪斜。值為 1 表示所有 PCS 通道均已對齊并去歪斜。當此信號為 1 時,表示 RX 路徑已對齊并且可接收包數據。當此信號為 0 時,表示存在本地故障狀況。這也對應于第 82.3 條中所定義的 MDIO 寄存器位3.50.12。此輸出對電平敏感 | |

| stat_rx_hi_ber | 誤碼率 (BER) 過高指示符。設置為 1 時,BER 過高(根據 IEEE 802.3-2015 標準的定義)。對應于第 82.3 條中所定義的 MDIO 寄存器位 3.32.1。此輸出對電平敏感。 | |

| stat_rx_status | PCS 狀態。值為 1 表示 PCS 已對齊且未處于 hi_ber 狀態。對應于第 82.3 條中所定義的 MDIO 寄存器位 3.32.12。此輸出對電平敏感。當 stat_rx_aligned 為 1 且 stat_rx_hi_ber 為 0 時,此輸出設置為 1。此設置由 IEEE 802.3-2015 標準定義。 | |

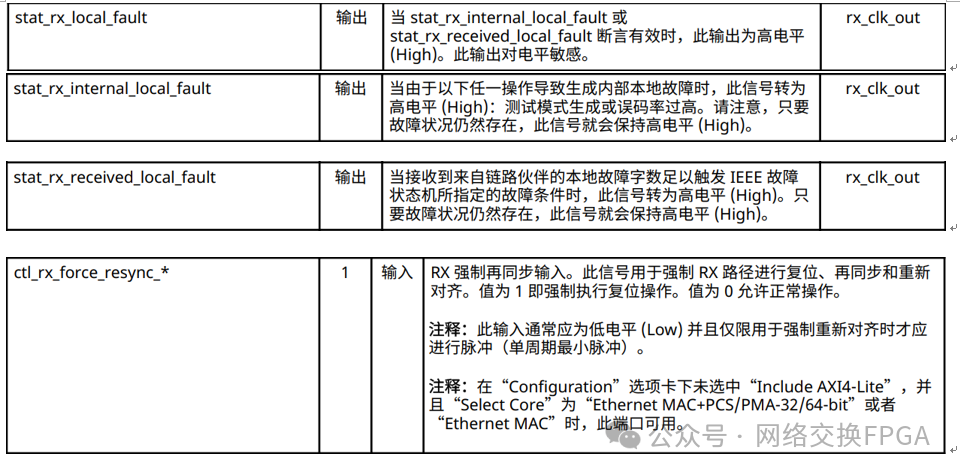

| stat_rx_local_fault | 當stat_rx_received_local_fault 或stat_rx_internal_local_fault 斷言有效時,此輸出設置為 1。此輸出對電平敏感。 | |

| RX錯誤狀態 | ||

| stat_rx_bad_fcs | 當此信號值為 1 時,表示錯誤檢測邏輯已在接收到的包中發現接收的 CRC32 值與期望的值不匹配。當檢測到 CRC32 錯誤時,接收到的包將被標記為包含錯誤,并隨在上一次傳輸(即 rx_eopout 斷言有效的周期)期間斷言有效的 rx_errout 一起發送,但 ctl_rx_ignore_fcs 斷言有效的情況下除外。每次檢測到 CRC32 錯誤時,都將斷言此信號有效并保持 1 個時鐘周期。 | |

| stat_rx_bad_code[1:0] | 此信號用于指示RX PCS 接收狀態機處于IEEE 802.3-2015 標準所定義的 RX_E 狀態的周期數。 | |

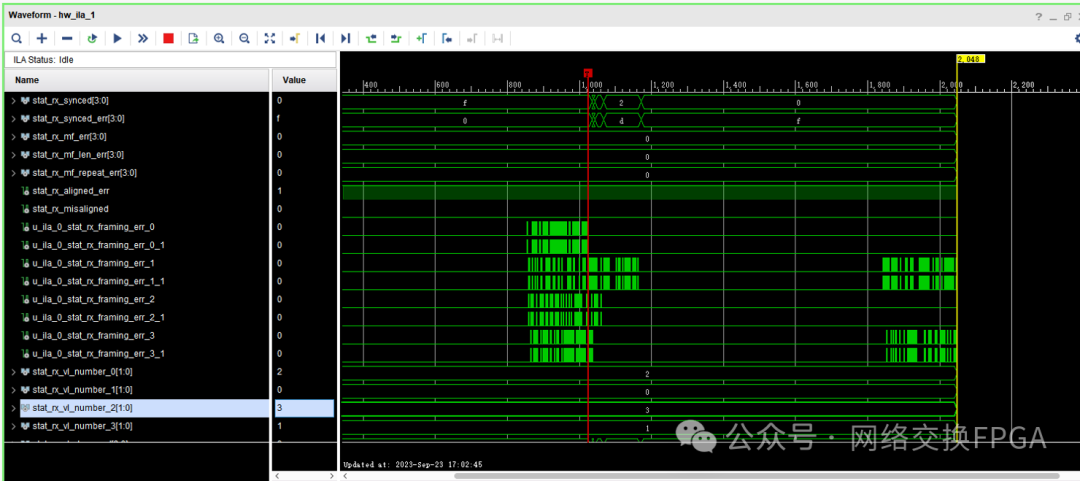

下圖為A芯片 40G接口的實測截圖。stat_rx_synced應始終保持4’hF,不穩定說明信號質量太差。一定程度上反映ASIC側的時鐘質量問題。

2)如果40G PCS部分使用相關代碼,可以基于以下信號展開監測:

40G PCS和對端鏈路建立過程主要有ABC三個階段:

A、同步頭鎖定:

監測信號:

/i_RX_CORE/i_RX_LANE0/i_RX_WD_SYNC_0/align_status[1:0]

/i_RX_CORE/i_RX_LANE0/i_RX_WD_SYNC_1/align_status[1:0]

/i_RX_CORE/i_RX_LANE1/i_RX_WD_SYNC_0/align_status[1:0]

/i_RX_CORE/i_RX_LANE1/i_RX_WD_SYNC_1/align_status[1:0]

正常情況下恒為1。

0表示復位,2表示鎖定失敗

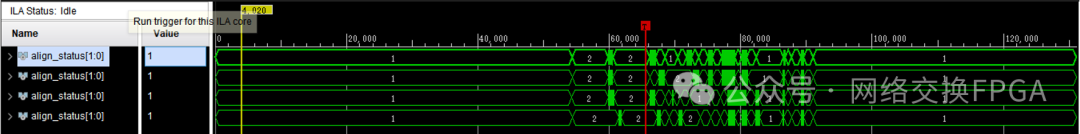

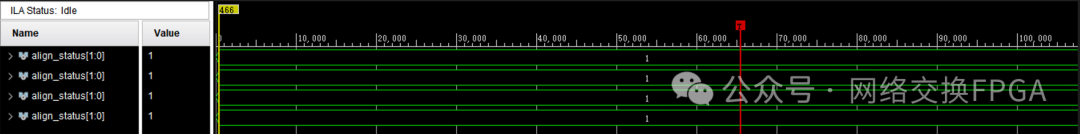

下圖為A芯片40G接口的實測截圖。alian_status應始終保持2’b1,不穩定說明信號質量太差。

FPGA連接網絡測試儀,正常鏈路情況下的截圖。

B、四通道各自鎖定

監測信號

/i_RX_TOP/i_RX_CORE/i_RX_LANE0/i_AFINDER_0/word_synced

/i_RX_TOP/i_RX_CORE/i_RX_LANE0/i_AFINDER_1/word_synced

/i_RX_TOP/i_RX_CORE/i_RX_LANE1/i_AFINDER_0/word_synced

/i_RX_TOP/i_RX_CORE/i_RX_LANE1/i_AFINDER_1/word_synced

正常情況下恒為1

0表示復位或鎖定失敗

C、四通道實現對齊

監測信號

/i_RX_CORE/i_RX_DESTRIPER/i_RX_LANE_ALIGNER/aligned

正常情況下恒為1

0表示復位或對齊失敗

B芯片40G接口芯片測試時,四通道的align_status和word_synced信號一直保持為1,說明同步頭鎖定和四通道各自鎖定沒有問題,但是aligned信號沒有拉高過,說明四個通道沒有實現過對齊。

繼續抓取四通道對齊的前一級模塊(四個緩存模塊)的相關信號,發現四個通道彼此間的數據延時差異過大,通常一個通道的數據緩存FIFO溢出時,其余通道仍然沒有數據進入緩存模塊,導致下一步通道間對齊無法進行。

后續發現PCS的模式配置寄存器有誤,默認情況下為10GBASE-CX4,將PCS正確配置為40GBASE-CR4后對齊標志可以成功拉高且保持穩定。

前面的四通道數據延時差異過大也是因為這種配置模式下對端單lane 3.125Gbps的數據在FPGA側單lane 10.3125Gbps的數據通道上傳輸導致的。

另外,如果FPGA自身四通道就沒有對齊,那大概率也是由于復位沒有做好,或者是復位的順序和復位時間,以及代碼中看門狗方式復位代碼有問題。

擴展:FPGA版本10Gbps以上速率以太網光口熱插拔問題。

在較復雜的測試環境下,即交換機光口始終有分組進入時,對交換機進行上下電或進行光口拔插,會導致交換機的40G MAC IP核會出現卡死和輸出錯幀的現象,若沒有錯幀過濾模塊,錯幀可能會導致交換機可編程解析器模塊不能正常工作,也可能會導致地址學習表短時間內學習到大量的錯誤的MAC地址和端口號,因此,需要“看門狗系統”主動復位交換機出錯的40G IP的MAC和GT,以及過濾MAC給出的錯幀(利用rx_user信號)。

a、rx側的時鐘需要恢復訓練,在連接上光纖后,tx數據中帶有時鐘信息,rx接收到tx的時鐘信息后,需要從高速串行流中恢復時鐘(鎖相環穩定時鐘),待時鐘穩定后才能正常傳輸數據。

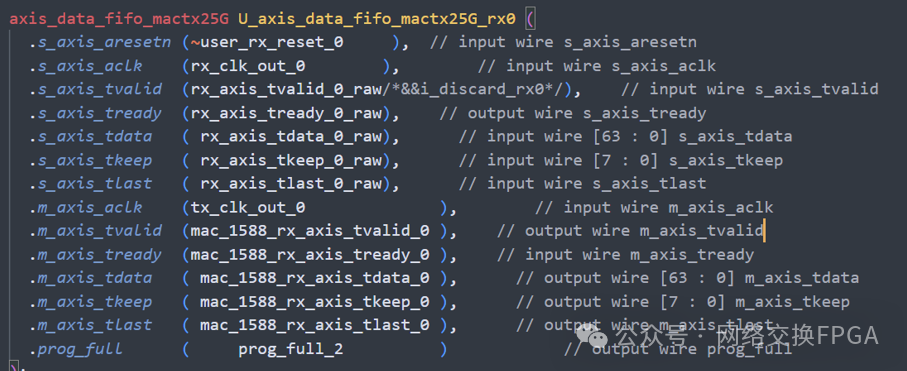

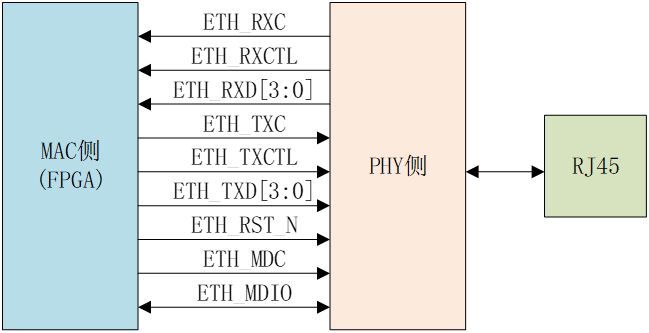

基于10G源碼作者Alex(著名開源項目Corundum網卡的作者)的代碼,我們在rx側出來的axi data接異步時鐘fifo,輸入用rx時鐘,輸出用tx時鐘。因為tx時鐘由本地晶振給出,保持穩定,不需要訓練,如下圖。

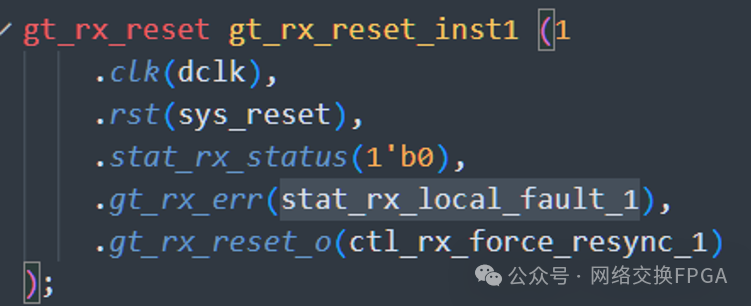

b、環境比較差的時候,做光口拔插實驗,會有link狀態的問題,link是單方向的rx link,查看手冊找到復位邏輯,做檢錯復位,以及link狀態丟失的主動復位,主動復位時間比較長持續100ms,1s內不會重復觸發。

復位模塊如下:

在拔插的時候對于電路來說不是單純的拔插,不論是拔動作還是插動作link狀態都會有0-1 1-0的變化,而link狀態時斷時續,在拉高時會有錯幀進入,需要加入錯幀過濾邏輯(判斷rx_user信號)。

c、打流過程中復位會產生進入錯幀的問題,也就是gt側在link狀態拉高的時候,同步并不是直接正常的,剛開始的時候會有一些內容和長度有問題的幀,大概10幀,對于2層交換機來說會地址自學習產生錯誤的mac地址,需要在link狀態穩定時讓幀進入邏輯,加入端口使能。加入端口使能,不往該端口發幀和不讓該端口的幀進交換,同時交換機有狀態信息統計也同步停止更新或者打開,這樣可以保護交換機內部邏輯不會受到影響。

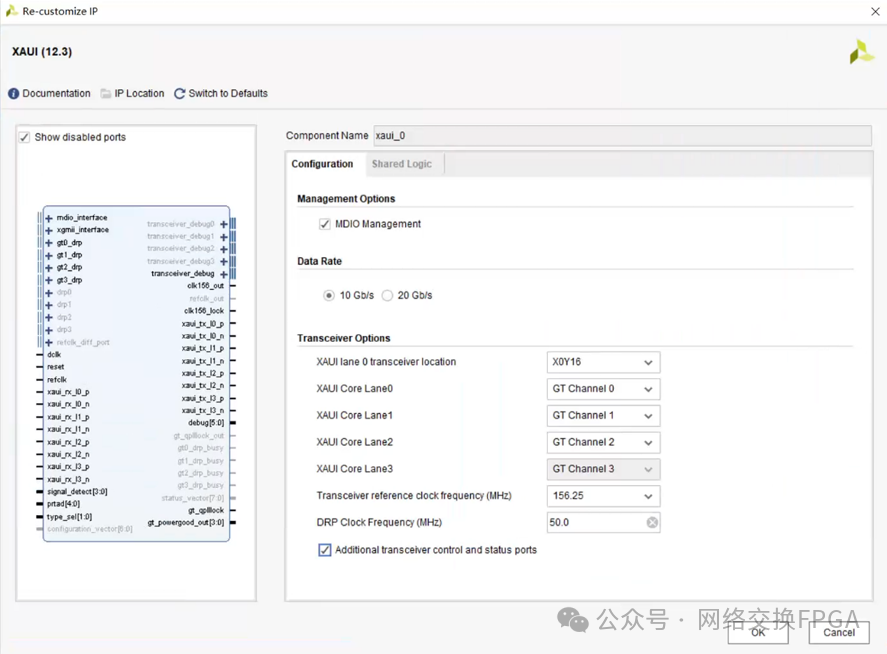

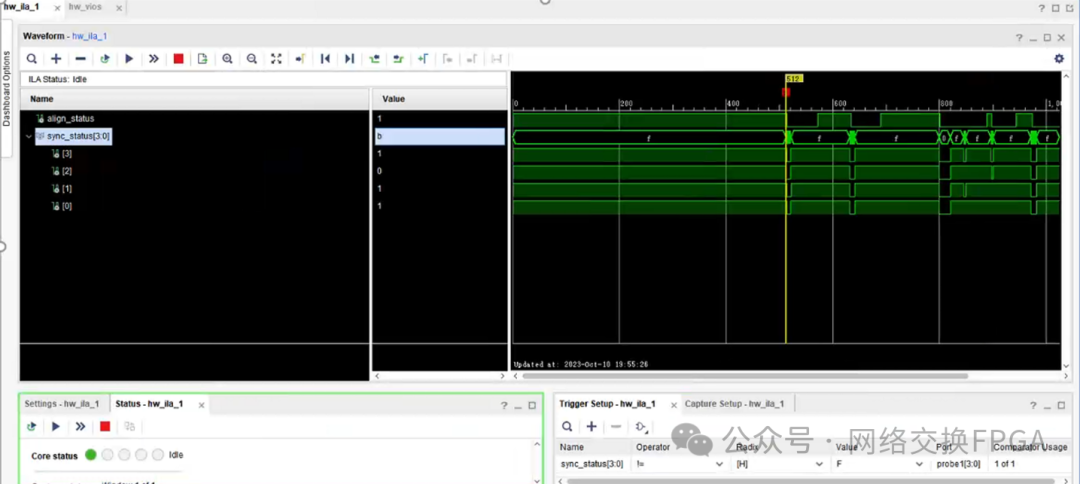

3)如果使用XAUI

主要監測align_status和sync_status[3:0]。

下圖為A芯片10G以太網接口實測截圖。

ILA顯示align_status不恒為1,sync_status不恒為F,說明10G的鏈路也不穩定。

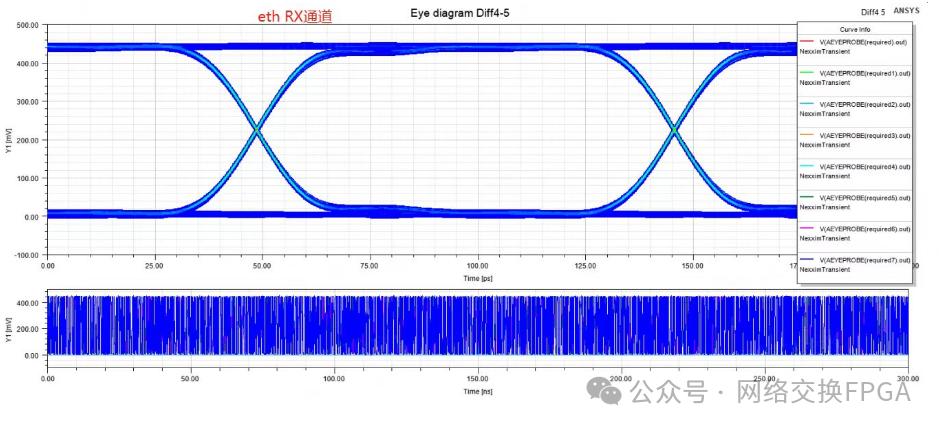

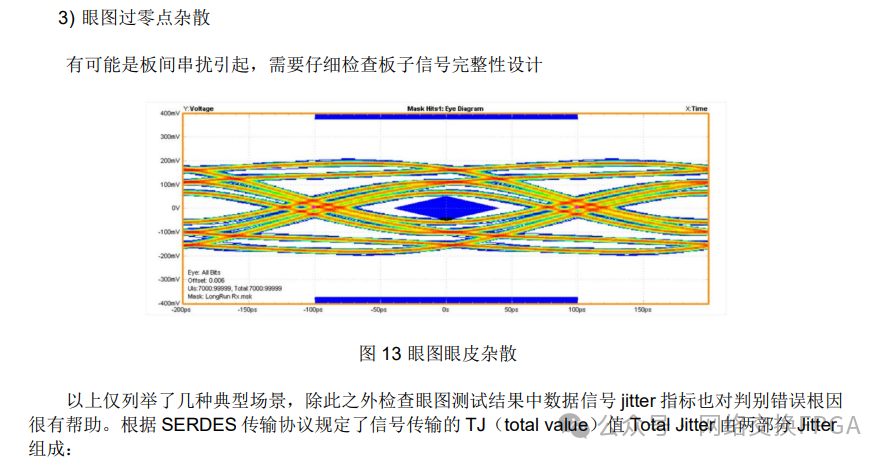

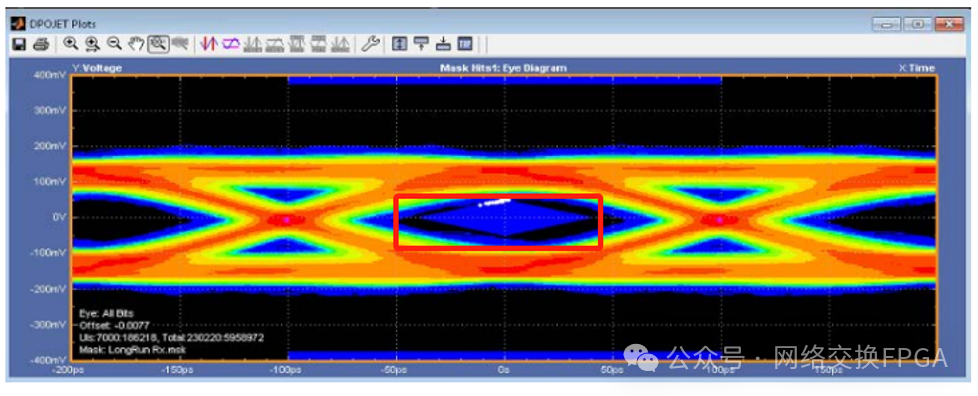

若ASIC側Serdes測試有問題,則也可能是封裝和基板帶來的問題。封裝時要考慮多lane之間共地,die外圍共享電阻的連接方式。同時,還要注意serdes時鐘是片內還是片外,在使用片內時鐘(on-chip clock)時,需要將片外時鐘接地或者懸空。在使用片外時鐘時,也需要將片內時鐘接地或者懸空。另外,基板也需要進行SI、PI等仿真,如果眼圖仿真結果不好,則有可能阻抗不連續,過孔要考慮;還有等長走線,雖然走了等長,有可能兩條線沒有一起繞蛇形等多種可能。以下是仿真較好的情況:

通過眼圖判斷serdes的情況也很重要,如下圖:

正常情況下,圖中眼睛區域可被包住即可。除了用專用設備看眼圖外,一般IP供應商會提供MATLAB或者Python的程序,可以通過讀取實際Serdes測試時對應相關寄存器的狀態,繪制出對應的眼圖。

4、ASIC版serdes故障定位

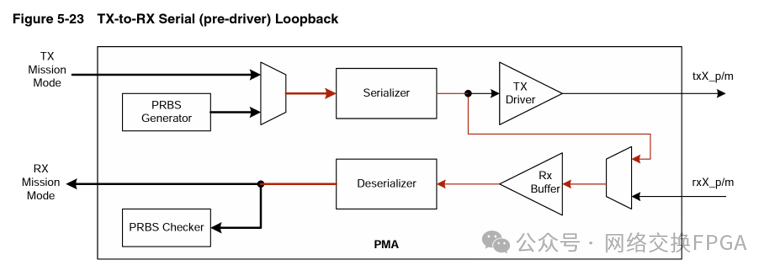

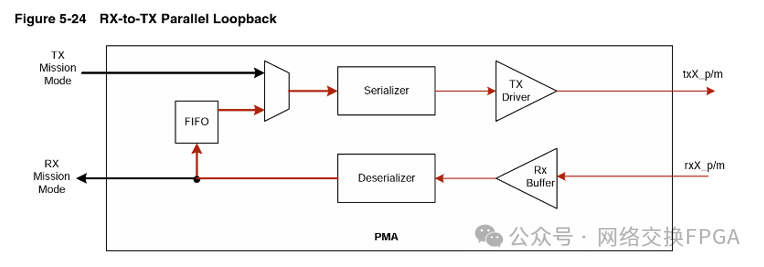

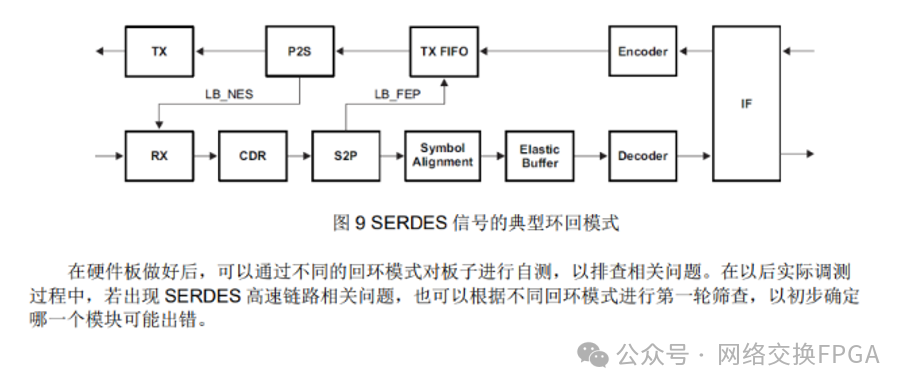

若SERDES高速鏈路存在問題,可通過多種回環模式進行第一輪篩查,以初步排查問題。

主要使用兩種模式:

(1) 近端回環LB_NES模式,即測試芯片PHY的tx2rx loopback,PRBS;

(2)遠端回環LB_FEP模式,即測試芯片PHY的rx2tx loopback;

若在近端回環模式下,BER值(誤碼率)較高,主要可以檢測SERDES 輸入時鐘相關設置,如果遠端回環模式下 BER 值較高,則主要檢測發送端幅值,衰減設置,發送側濾波器參數設置,接收端DFE 設置,CDR 設置以及和時鐘相位偏移相關的設置。

PRBS:串行總線的物理層測試通常分為發射機測試和接收機測試,又稱為 TX 測試和 RX 測試。發射機測試通常包括眼圖、抖動、信號波形、幅度、上升下降時間等測試項目,接收機測試通常包括誤碼率、抖動容限、接收機靈敏度等測試項目。對于眼圖測試、誤碼率和抖動容限測試,最常用的測試碼是 PRBS,主要有 PRBS7、PRBS15、PRBS23 和 PRBS31。

PRBS7 是目前 10Gbps 以下的串行總線中最常用的測試碼型,在 ITU-TV.29 規范中規定。PRBS7 屬于短偽隨機碼型,與 8b10b NRZ 編碼的數據流很相似,所以,在 PCIe、SATA、XAUI、1000BASE-LX、FC、SAS 等采用 8b10b 編碼的串行總線中,PRBS7 是最常用的測試碼型,支持這些總線的芯片通常都可以輸出 PRBS7 測試碼型,用于眼圖、抖動或誤碼率測量。PRBS31是一種較長的偽隨機碼型,其多項式為X31+X28+1,碼長為2^31-1個比特。PRBS31的碼流中最長的連1為31個,最長的連0為30個,包含了相當多的低頻成分,因此適用于像SONET/SDH信號那樣包含了很多低頻成分的物理層測量。PRBS31也是10 Gigabit Ethernet推薦的測試碼型之一。

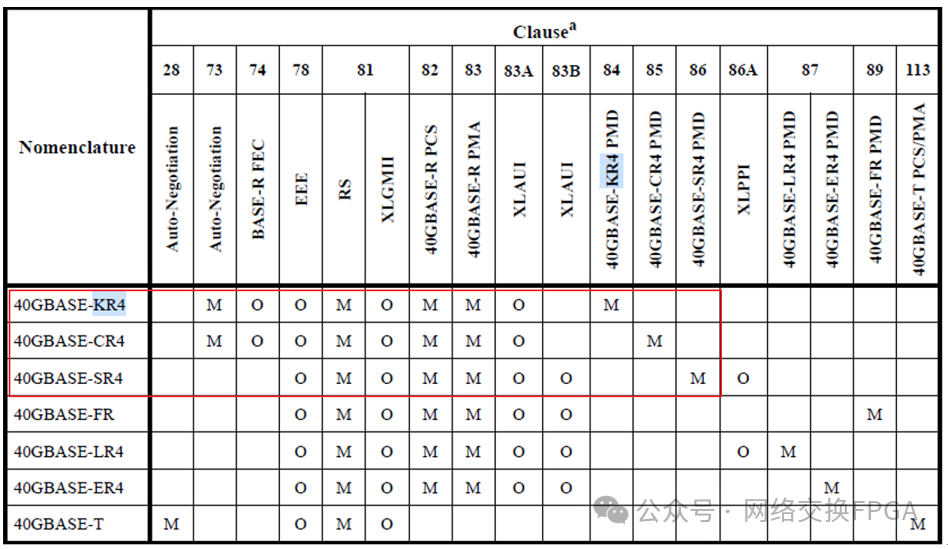

KR:背板傳輸;CR:銅線互聯;SR:短距光纖傳輸。

-

FPGA

+關注

關注

1630文章

21759瀏覽量

604297 -

SerDes

+關注

關注

6文章

200瀏覽量

34961 -

以太網接口芯片

+關注

關注

0文章

38瀏覽量

6593

原文標題:使用FPGA對40G以太網接口芯片Serdes進行測試的方法

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于FPGA的萬兆以太網接口的設計與實現

40G QSFP+光模塊的完美鏈接-Cisco Nexus 6004交換機

解密易飛揚40G QSFP+ PSM4光模塊

基于FPGA的10G以太網光接口設計

超遠程40G以太網子系統的遠端回路問題如何解決

Serdes到Serdes 10G以太網連接是T2080上的一個功能選項,通過光纖或跨背板時會失敗的原因?

基于FPGA的萬兆以太網接口設計

分析25G以太網架構能否取代40G

部署40G以太網時要考慮哪些因素?

詳解FPGA的10G以太網接口調試

40G以太網光模塊解決方案

使用FPGA對40G以太網接口芯片Serdes進行測試的方法

使用FPGA對40G以太網接口芯片Serdes進行測試的方法

評論