前面兩期的芝識(shí)課堂,我們介紹了大量關(guān)于CMOS邏輯IC應(yīng)用的一些細(xì)節(jié)事項(xiàng),本期課堂讓我們進(jìn)入實(shí)際的應(yīng)用案例,解決電路設(shè)計(jì)中的噪聲問題。

開關(guān)噪聲類型

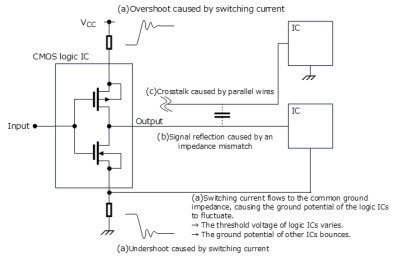

使用CMOS邏輯IC時(shí),應(yīng)注意開關(guān)噪聲。主要噪聲類型包括:開關(guān)噪聲(過沖、欠沖、接地反彈)、信號(hào)反射串?dāng)_噪聲。這些噪聲是由輸出轉(zhuǎn)換速率(di/dt或dv/dt)和輸出走線引起的。除此之外,還應(yīng)注意在多種組合條件下產(chǎn)生的電磁干擾(EMI)噪聲和附近電子設(shè)備發(fā)出的電磁敏感性(EMS)噪聲。

降低開關(guān)噪聲的問題

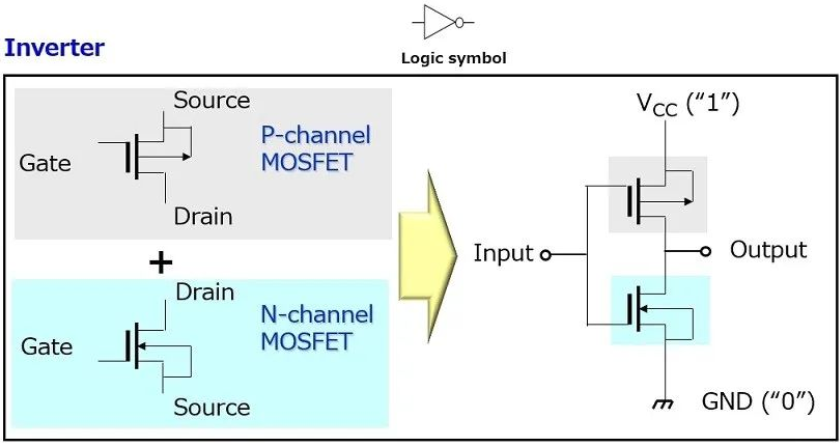

CMOS邏輯IC中的MOSFET在對(duì)內(nèi)部和外部負(fù)載電容進(jìn)行充放電的同時(shí)進(jìn)行開關(guān)轉(zhuǎn)換。開關(guān)過程中的走線阻抗可以看作是一個(gè)LCR電路。由于開關(guān)電流(i)流過電感(L),所以在CMOS邏輯IC的VCC和GND線上出現(xiàn)峰值電壓(=L(di/dt))。這種噪聲便稱為開關(guān)噪聲。多個(gè)同步開關(guān)輸出會(huì)消耗較大的充電/放電電流,因此會(huì)產(chǎn)生較大的開關(guān)噪聲(稱為同步開關(guān)噪聲)。

降低開關(guān)噪聲的對(duì)策

(1)分別增加和減小VCC和GND線的寬度和長(zhǎng)度,以減小它們的電感。

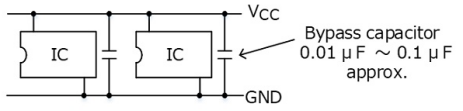

(2)將旁路電容器放置在CMOS邏輯IC的VCC和GND引腳之間并盡可能使其靠近。

(3)注意時(shí)鐘和重置信號(hào)。未使用的門輸入端(如驅(qū)動(dòng)器)應(yīng)連接到VCC或GND。將一個(gè)低通濾波器連接到使用的門輸出端,以消除噪聲。

(4)選擇低噪聲IC。

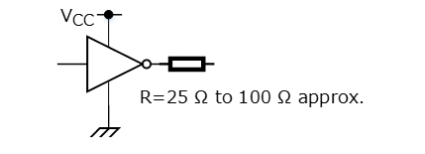

(5)在使用的門輸出端添加一個(gè)阻尼電阻器。但必須檢查輸出波形以調(diào)整阻尼電阻器的值。

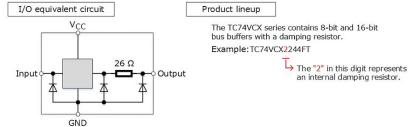

東芝為CMOS IC提供內(nèi)部阻尼電阻器,這不僅有助于降低開關(guān)噪聲,而且有助于減少零件數(shù)量。

信號(hào)反射的問題

對(duì)于高速CMOS邏輯IC,反射會(huì)導(dǎo)致信號(hào)延遲、振鈴、過沖和欠沖增加。

傳輸線路反射:典型走線的特性阻抗(*1)為50至150 Ω。但是高速CMOS邏輯IC的I/O阻抗與典型走線的特性阻抗不同。這種阻抗的不匹配將導(dǎo)致一部分發(fā)射信號(hào)被反射到傳輸線路的發(fā)送端和接收端。

信號(hào)反射不影響緩慢上升的輸出,因其上升周期與反射信號(hào)的上升周期重疊。當(dāng)反射信號(hào)上升后返回到輸出時(shí),即當(dāng)下列等式成立時(shí),信號(hào)反射才會(huì)導(dǎo)致問題:

tr<2T

tr:輸出信號(hào)上升時(shí)間

T:從傳輸線路的發(fā)送端到接收端的傳輸延遲時(shí)間

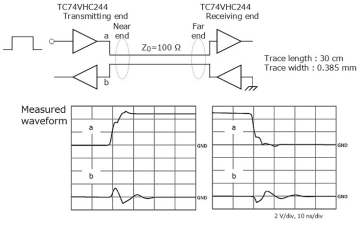

假設(shè)輸出上升時(shí)間為3 ns,沿傳輸線路的傳輸延遲時(shí)間為5 ns/m。當(dāng)傳輸線路為30 cm或更長(zhǎng)時(shí),信號(hào)反射會(huì)產(chǎn)生顯著影響。

*1特性阻抗

特性阻抗是傳輸線路(如電路板跡線、同軸電纜)的特性之一。

傳輸線路特性阻抗的一般表達(dá)式是Z_0=√(L/C),其中L是單位長(zhǎng)度的電感,C是單位長(zhǎng)度的電容。特性阻抗的單位為歐姆(Ω)。當(dāng)50 Ω的終端電阻器連接到特性阻抗為50Ω的傳輸線路末端時(shí),連接點(diǎn)處不會(huì)發(fā)生信號(hào)反射。

如果特性阻抗與電阻值不匹配,則在連接點(diǎn)處會(huì)發(fā)生信號(hào)反射。

減少信號(hào)反射的對(duì)策

(1)提高電路板組裝密度,減少電路板走線的長(zhǎng)度,以減小其電感和電容。但是在這種情況下,需要注意相鄰軌跡之間的串?dāng)_。

(2)不要使用輸出電流高于必要值的IC。

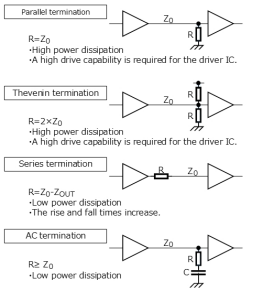

(3)提供電氣終端,以便CMOS邏輯IC的I/O阻抗與傳輸線路的特性阻抗匹配。

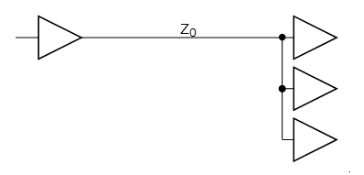

(4)當(dāng)一個(gè)CMOS邏輯IC的輸出驅(qū)動(dòng)多個(gè)CMOS邏輯IC時(shí),輸出走線應(yīng)在靠近被驅(qū)動(dòng)IC的位置呈扇形展開。

串?dāng)_的問題

串?dāng)_噪聲是由并行延伸的兩條相鄰傳輸線路(分別稱為干擾線路和受干擾線路)之間的電容或電感耦合引起的。關(guān)于串?dāng)_,應(yīng)注意快速上升或下降的信號(hào)。當(dāng)此類信號(hào)通過傳輸線路時(shí),串?dāng)_噪聲將在相鄰的線路(受干擾線路)中產(chǎn)生并且在與干擾信號(hào)相同的方向和與干擾信號(hào)相反的方向上同時(shí)傳播。由于串?dāng)_傳播的速度與干擾信號(hào)的速度相等,因此在與干擾信號(hào)相同方向上傳播的串?dāng)_噪聲(稱為遠(yuǎn)端串?dāng)_)將顯示為脈沖狀噪聲。

另一方面,當(dāng)干擾信號(hào)沿線路傳播時(shí),沿相反方向傳播的串?dāng)_噪聲(稱為近端串?dāng)_)保持恒定水平。串?dāng)_噪聲也沿著干擾線路傳播,然后返回到受干擾線路。

串?dāng)_應(yīng)對(duì)措施

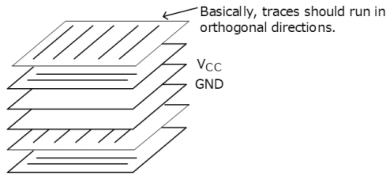

(1)在并行走線之間添加接地走線。(或者使用多層電路板,其中低阻抗層(如VCC或GND層)位于信號(hào)層之間。)

(2)減少并行運(yùn)行的走線長(zhǎng)度。

(3)如果是多層電路板,在相互正交的交替層上走線。

(4)增加走線之間的間距。

下圖展示了沿30 cm走線傳播的典型串?dāng)_噪聲水平。這個(gè)例子顯示的是近端串?dāng)_。如果受干擾走線的近端是接收端,則很容易受到串?dāng)_影響。

本篇文章,我們針對(duì)CMOS邏輯IC應(yīng)用中的噪聲問題做了講解,并分享了不同噪聲的應(yīng)對(duì)之策。在下期文章中,我們還將繼續(xù)介紹電路設(shè)計(jì)中可能出現(xiàn)的其他困擾及相關(guān)對(duì)策,大家不要錯(cuò)過哦!

關(guān)于東芝電子元件及存儲(chǔ)裝置株式會(huì)社

東芝電子元件及存儲(chǔ)裝置株式會(huì)社是先進(jìn)的半導(dǎo)體和存儲(chǔ)解決方案的領(lǐng)先供應(yīng)商,公司累積了半個(gè)多世紀(jì)的經(jīng)驗(yàn)和創(chuàng)新,為客戶和合作伙伴提供分立半導(dǎo)體、系統(tǒng)LSI和HDD領(lǐng)域的杰出解決方案。

東芝電子元件及存儲(chǔ)裝置株式會(huì)社十分注重與客戶的密切協(xié)作,旨在促進(jìn)價(jià)值共創(chuàng),共同開拓新市場(chǎng),期待為世界各地的人們建設(shè)更美好的未來(lái)并做出貢獻(xiàn)。

-

CMOS

+關(guān)注

關(guān)注

58文章

5726瀏覽量

235739 -

開關(guān)噪聲

+關(guān)注

關(guān)注

0文章

19瀏覽量

11272 -

邏輯IC

+關(guān)注

關(guān)注

0文章

26瀏覽量

6483

原文標(biāo)題:芝識(shí)課堂【CMOS邏輯IC的使用注意事項(xiàng)】—深入電子設(shè)計(jì),需要這份指南(三)

文章出處:【微信號(hào):toshiba_semicon,微信公眾號(hào):東芝半導(dǎo)體】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

CMOS邏輯IC的使用注意事項(xiàng)

如何優(yōu)化CMOS邏輯IC的性能

開關(guān)電源噪聲對(duì)策的步驟

開關(guān)電源噪聲對(duì)策的詳細(xì)解說(shuō)

開關(guān)電源噪聲對(duì)策的步驟

開關(guān)電源噪聲對(duì)策的幾個(gè)步驟

電路設(shè)計(jì)EMI對(duì)策及輸出噪聲對(duì)策

CMOS邏輯IC基礎(chǔ)知識(shí):系統(tǒng)認(rèn)識(shí)CMOS邏輯IC

開關(guān)電源噪聲對(duì)策的步驟

噪聲對(duì)策-開關(guān)電源噪聲對(duì)策的基礎(chǔ)知識(shí)

一起了解CMOS邏輯IC的基本操作

CMOS邏輯IC的基本操作流程

【CMOS邏輯IC基礎(chǔ)知識(shí)】——受歡迎的CMOS邏輯IC

CMOS邏輯IC基礎(chǔ)知識(shí):解密組合邏輯背后的強(qiáng)大用途(上)

【CMOS邏輯IC基礎(chǔ)知識(shí)】—解密組合邏輯背后的強(qiáng)大用途!(上)

CMOS邏輯IC應(yīng)用中的噪聲問題和解決對(duì)策

CMOS邏輯IC應(yīng)用中的噪聲問題和解決對(duì)策

評(píng)論