文章來(lái)源:學(xué)習(xí)那些事

原文作者:趙先生

本文主要介紹MOS管及本征增益

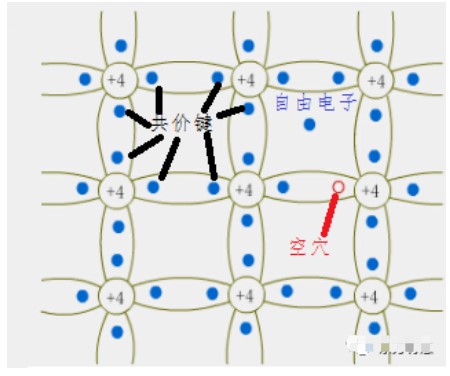

MOS,是金屬-氧化物-半導(dǎo)體場(chǎng)效應(yīng)晶體管英文名稱(chēng)的縮寫(xiě),是一種獨(dú)特的半導(dǎo)體器件,它通過(guò)電場(chǎng)效應(yīng)來(lái)控制輸出回路的電流,這一特性使其得名。該器件主要依賴(lài)半導(dǎo)體中的多數(shù)載流子進(jìn)行導(dǎo)電,因此也被歸類(lèi)為單極型晶體管。在場(chǎng)效應(yīng)晶體管(FET)的廣泛分類(lèi)中,除了MOS管,還有諸如結(jié)型場(chǎng)效應(yīng)晶體管(JFET)、金屬-半導(dǎo)體場(chǎng)效應(yīng)晶體管(MESFET)、無(wú)結(jié)場(chǎng)效應(yīng)晶體管(JLFET)以及量子阱場(chǎng)效應(yīng)晶體管(QWFET)等多種類(lèi)型。在這些類(lèi)型中,MOS管因其諸多優(yōu)點(diǎn),如高輸入電阻、低功耗、低噪聲以及易于集成等,成為了最為常用的選擇,廣泛應(yīng)用于模擬電路與數(shù)字電路中,并在市場(chǎng)上占據(jù)了絕對(duì)的主導(dǎo)地位,遠(yuǎn)超雙極型晶體管(BJT)。

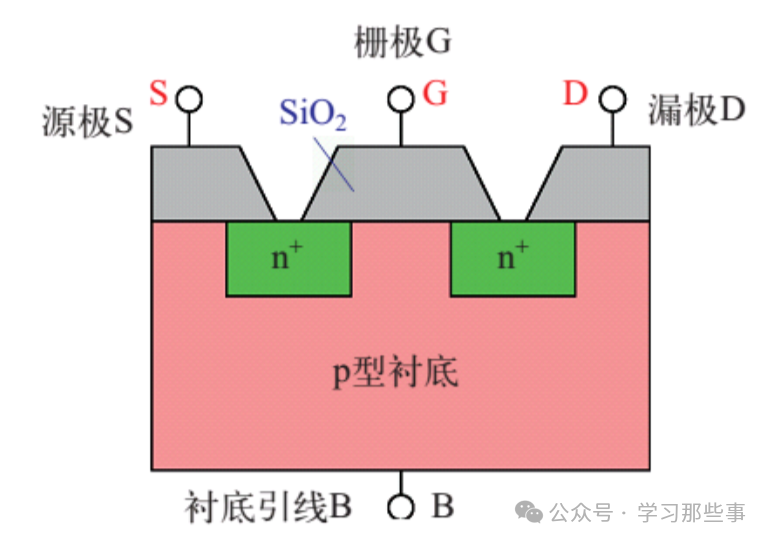

MOS管進(jìn)一步細(xì)分為NMOS(N溝道型)和PMOS(P溝道型)兩種,它們都屬于絕緣柵場(chǎng)效應(yīng)管。當(dāng)NMOS和PMOS被巧妙地組合在一起時(shí),就構(gòu)成了我們常說(shuō)的CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)器件。NMOS的結(jié)構(gòu)設(shè)計(jì)精巧,包含了三個(gè)關(guān)鍵的電極:源極(Source, S)、柵極(Gate, G)和漏極(Drain, D),如下圖所示,這三個(gè)電極的功能可以分別與雙極型晶體管的發(fā)射極、基極和集電極相對(duì)應(yīng)。

NMOS結(jié)構(gòu)示意圖

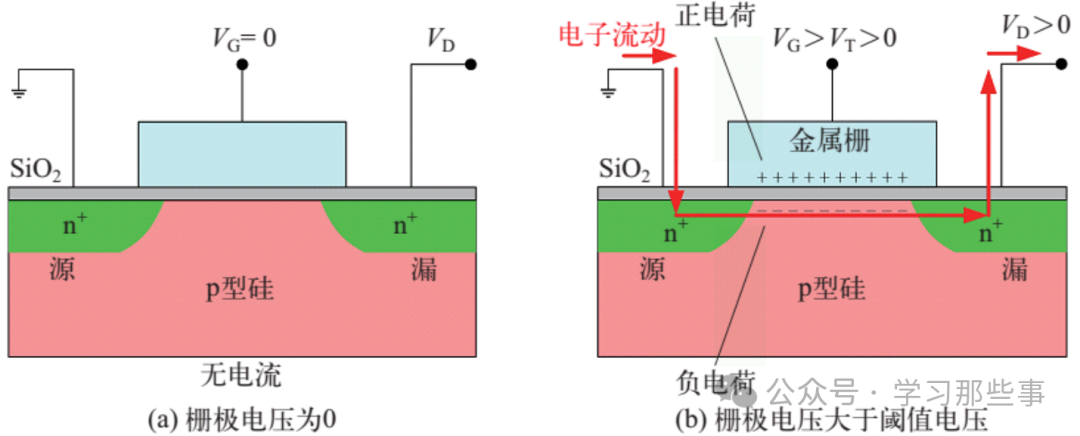

如下圖所示,在NMOS的工作過(guò)程中,如果柵極沒(méi)有施加電壓,那么源區(qū)和漏區(qū)之間就會(huì)因?yàn)槿狈?dǎo)電溝道而無(wú)法形成電流。然而,當(dāng)柵極被施加一個(gè)足夠大的正電壓時(shí),這個(gè)電壓就會(huì)像磁石一樣吸引P型襯底中的少數(shù)載流子——電子,使它們聚集在柵極和襯底的交界處。隨著電子的聚集,襯底表面就會(huì)形成一個(gè)布滿(mǎn)電子的反型層,這個(gè)反型層實(shí)際上是將原來(lái)的P型區(qū)域反轉(zhuǎn)成了N型區(qū)域,從而為電流提供了一個(gè)暢通的通道,使得源區(qū)的電子能夠順利地流向漏區(qū),形成電流。這個(gè)過(guò)程展示了MOS管作為電壓控制器件的本質(zhì),即通過(guò)柵電壓來(lái)精確地調(diào)控源極和漏極之間的電流。這個(gè)反型層構(gòu)建了一個(gè)高效的電子傳輸路徑,使得源區(qū)的電子能夠持續(xù)不斷地流向漏區(qū),進(jìn)而形成電流。因此,MOS管實(shí)質(zhì)上是一種電壓控制器件,其核心在于通過(guò)柵電壓來(lái)精確調(diào)控源極與漏極之間的電流大小。我們將開(kāi)啟場(chǎng)效應(yīng)管所必需的最小柵極電壓定義為閾值電壓。柵極在此扮演了一個(gè)開(kāi)關(guān)的角色:當(dāng)柵極電壓低于閾值電壓或柵極電壓被移除時(shí),它處于關(guān)閉狀態(tài),阻止了源漏間電流的通過(guò);而當(dāng)柵極電壓高于閾值電壓時(shí),它則打開(kāi)通道,允許源漏間的電流自由流通。

NMOS的電學(xué)性能

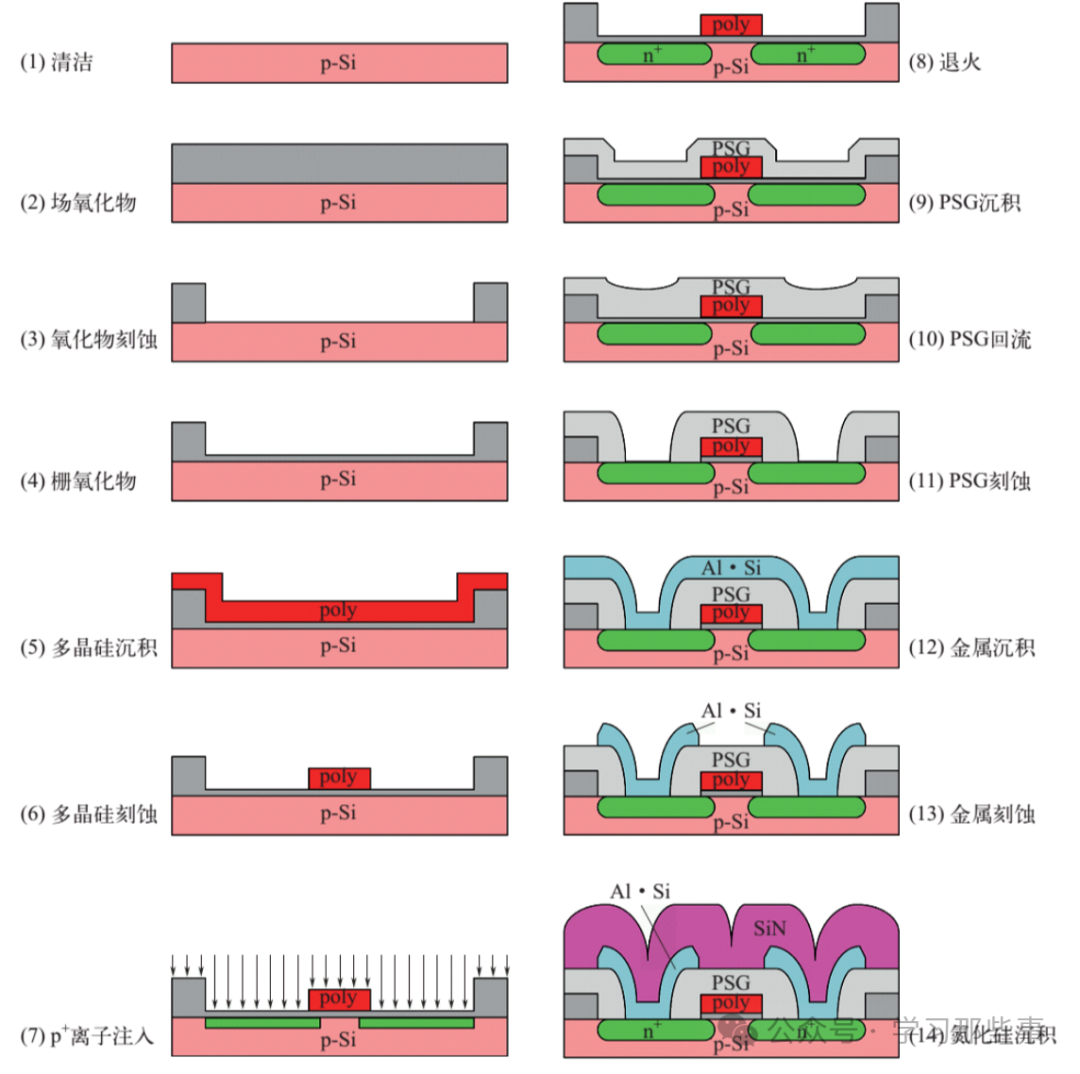

接下來(lái),我們概述一套典型的NMOS管制備工藝流程。首先,通過(guò)外延生長(zhǎng)在硅襯底上形成一層外延層,這一步驟旨在獲取低氧含量的硅單晶,它構(gòu)成了MOS管中的半導(dǎo)體部分(S)然后利用氧化、光刻及刻蝕技術(shù)制備場(chǎng)氧化物,其作用是隔離不同的MOS管,防止它們之間的電氣干擾。接下來(lái)通過(guò)氧化工藝生成柵氧化物層,這是MOS管中的氧化物部分(O)。下一步是沉積多晶硅材料,并通過(guò)光刻和刻蝕工藝形成多晶硅柵極,盡管多晶硅并非傳統(tǒng)意義上的金屬,但經(jīng)過(guò)摻雜后其導(dǎo)電性能良好,且適合集成電路工藝,因此取代了早期的金屬鋁材料。隨后進(jìn)入源區(qū)和漏區(qū)的制作階段,先通過(guò)光刻工藝開(kāi)窗,再進(jìn)行磷離子的注入,并進(jìn)行退火處理以鞏固結(jié)構(gòu)。緊接著沉積一層磷硅酸鹽玻璃(PSG)作為介質(zhì)層,通過(guò)沉積和回流工藝使其表面平整,為后續(xù)的光刻步驟打下良好基礎(chǔ)。而后,對(duì)PSG進(jìn)行光刻和刻蝕處理,以形成所需的圖案。接著,沉積鋁硅合金作為金屬連線(xiàn)材料,并通過(guò)光刻和刻蝕工藝制備出金屬連線(xiàn)。最后,沉積一層氮化硅作為鈍化保護(hù)層,為整個(gè)器件提供額外的保護(hù)和穩(wěn)定性。

MOS管的本征增益

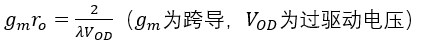

在共源極放大器配置下,晶體管所能展現(xiàn)的最大低頻小信號(hào)增益,被定義為MOS管的本征增益,本征增益可表示為

詳細(xì)推導(dǎo)過(guò)程此處略去不述。根據(jù)該式,MOS管的本征增益與過(guò)驅(qū)動(dòng)電壓及溝長(zhǎng)調(diào)制系數(shù)λ成反比關(guān)系。由于λ與MOS管的溝道長(zhǎng)度L成反比,因此,本征增益會(huì)隨著L的增大而提升。理論上,減小過(guò)驅(qū)動(dòng)電壓和增大L均可提升MOS管的本征增益。然而,這兩個(gè)操作都會(huì)減緩MOS管的工作速度。因此,在實(shí)際電路設(shè)計(jì)中,我們需要在增益與速度之間做出權(quán)衡。這種增益與速度的平衡考量,始終是模擬集成電路設(shè)計(jì)領(lǐng)域的核心議題。值得注意的是,由下面的式子可知

MOS管的本征增益在設(shè)計(jì)跨導(dǎo)效率時(shí),對(duì)過(guò)驅(qū)動(dòng)電壓的選擇原則與本征增益相似,但本征增益還額外受到溝道長(zhǎng)度的影響。隨著MOS器件特征尺寸的持續(xù)縮減,其本征增益呈現(xiàn)下降趨勢(shì),這對(duì)我們的設(shè)計(jì)構(gòu)成了日益嚴(yán)峻的挑戰(zhàn)。

此外,我們還需警惕,過(guò)低的過(guò)驅(qū)動(dòng)電壓可能使MOS管進(jìn)入亞閾值區(qū)域,該區(qū)域內(nèi)MOS管的工作特性與飽和區(qū)大相徑庭,很多相關(guān)公式和理論將不再適用。

-

放大器

+關(guān)注

關(guān)注

145文章

14119瀏覽量

216539 -

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28702瀏覽量

234183 -

MOS管

+關(guān)注

關(guān)注

109文章

2543瀏覽量

70139 -

晶體管

+關(guān)注

關(guān)注

77文章

9995瀏覽量

140952

原文標(biāo)題:MOS管及本征增益簡(jiǎn)介

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

#硬聲創(chuàng)作季 集成電路設(shè)計(jì)基礎(chǔ):2-6MOS管的本征增益視頻

本征測(cè)量標(biāo)準(zhǔn)

本征半導(dǎo)體、雜質(zhì)半導(dǎo)體ppT

一維諧振子的本征值問(wèn)題

半導(dǎo)體二極管及其應(yīng)用

本征激勵(lì)法用于天線(xiàn)陣方向圖綜合

高階矢量基函數(shù)在腔體本征值問(wèn)題中的應(yīng)用

基于F_P原理的非本征型光纖爆炸動(dòng)壓傳感器設(shè)計(jì)_陳顯

新型鋰電池本征化學(xué)石墨烯介紹

一文帶你搞懂本征半導(dǎo)體與PN結(jié)

分析一下本征半導(dǎo)體

評(píng)論