一、Chiplet技術的定義與背景

Chiplet技術,也被稱為小芯片或芯粒技術,是一種創新的芯片設計理念。它將傳統的大型系統級芯片(SoC)分解成多個小型、功能化的芯片模塊(Chiplet),然后通過先進的封裝技術將這些模塊連接在一起,形成一個完整的系統。這一技術的出現,源于對摩爾定律放緩的應對以及對芯片設計復雜性和成本控制的追求。

隨著半導體技術的不斷發展,芯片集成度不斷提高,單片SoC的設計難度和成本也隨之增加。同時,不同功能模塊對工藝制程的需求差異,使得單片SoC難以滿足所有性能要求。Chiplet技術通過模塊化設計,允許設計師根據實際需求選擇不同工藝制程的芯粒進行組合,從而有效解決了這些問題。

二、Chiplet技術的優勢

(一)提高設計靈活性和可擴展性

模塊化設計

Chiplet技術采用模塊化設計思想,將芯片功能分解成多個獨立的芯粒。這種設計方式使得設計師可以根據實際需求,靈活選擇和組合不同的芯粒,從而快速實現不同功能的產品。例如,對于需要高性能計算的應用,可以選擇高性能的CPU芯粒和GPU芯粒進行組合;對于需要低功耗的應用,則可以選擇低功耗的芯粒進行組合。

可擴展性

Chiplet技術的可擴展性體現在多個方面。首先,它允許設計師通過增加或減少芯粒的數量,輕松調整芯片的性能和功耗。其次,隨著新技術的不斷出現,設計師可以很方便地將新的芯粒集成到現有系統中,實現產品的快速升級和迭代。這種可擴展性使得Chiplet技術在應對快速變化的市場需求時具有顯著優勢。

(二)降低設計成本和制造成本

設計成本

Chiplet技術通過模塊化設計,降低了芯片設計的復雜度。設計師可以將復雜的SoC設計分解成多個相對簡單的芯粒設計,從而降低設計難度和成本。此外,由于芯粒可以獨立設計和驗證,因此可以并行開展多個芯粒的設計工作,進一步縮短設計周期。

制造成本

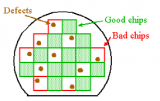

Chiplet技術通過優化工藝流程和減少浪費,降低了芯片的制造成本。首先,由于芯粒尺寸較小,因此可以在同一晶圓上制造更多的芯粒,提高晶圓利用率。其次,由于芯粒可以獨立制造和測試,因此可以在制造過程中及時發現和修復缺陷,減少廢品率。最后,由于Chiplet技術允許使用不同工藝制程的芯粒進行組合,因此可以選擇成本更低的工藝制程來制造非關鍵性能的芯粒,從而降低整體制造成本。

(三)提高芯片良率和可靠性

提高良率

Chiplet技術通過將大型SoC分解成多個小型芯粒,降低了每個芯粒的制造難度和缺陷率。由于芯粒尺寸較小,因此更容易實現高質量的制造過程。此外,由于芯粒可以獨立測試和篩選,因此可以在制造過程中及時發現和剔除缺陷芯粒,提高整體良率。

提高可靠性

Chiplet技術通過優化封裝設計和散熱設計,提高了芯片的可靠性。首先,先進的封裝技術可以實現芯粒之間的高密度、低延遲互連,減少信號傳輸過程中的損耗和干擾。其次,通過合理的散熱設計,可以有效降低芯片的工作溫度,提高芯片的長期可靠性。

(四)加速產品上市時間和創新速度

加速上市時間

Chiplet技術通過模塊化設計和并行開發,顯著縮短了產品的上市時間。設計師可以獨立設計和驗證每個芯粒,然后將其組合成完整的芯片系統。這種并行開發方式使得設計師可以更快地響應市場需求和變化,推出更具競爭力的產品。

加速創新速度

Chiplet技術為芯片創新提供了新的思路和方向。設計師可以根據實際需求,靈活選擇和組合不同的芯粒,實現新的功能和應用。此外,由于Chiplet技術允許使用不同工藝制程的芯粒進行組合,因此可以更容易地實現跨代工藝的創新和融合。

三、Chiplet技術的挑戰

(一)互連技術的挑戰

高速互連需求

Chiplet技術需要實現芯粒之間的高速互連,以滿足高性能計算和低延遲通信的需求。然而,隨著芯粒數量的增加和互連距離的延長,互連帶寬和延遲成為制約Chiplet技術發展的關鍵因素。因此,如何開發高效、可靠的互連技術成為Chiplet技術面臨的重要挑戰。

信號完整性問題

在Chiplet系統中,由于芯粒之間互連密度高、距離短,信號完整性問題變得尤為突出。信號反射、串擾和抖動等問題可能導致信號失真和傳輸錯誤,影響芯片的性能和可靠性。因此,如何確保信號在互連過程中的完整性和穩定性成為Chiplet技術需要解決的關鍵問題。

(二)封裝技術的挑戰

先進封裝技術需求

Chiplet技術需要采用先進的封裝技術來實現芯粒之間的高密度、低延遲互連。然而,先進封裝技術的研發和制造成本較高,且技術難度較大。因此,如何降低先進封裝技術的成本和提高其可靠性成為Chiplet技術面臨的重要挑戰。

封裝熱管理問題

在Chiplet系統中,由于芯粒數量多、功耗大,封裝熱管理問題變得尤為突出。高溫可能導致芯片性能下降和可靠性降低,甚至引發封裝失效。因此,如何有效散熱和降低封裝溫度成為Chiplet技術需要解決的關鍵問題。

(三)測試與驗證的挑戰

測試復雜度增加

Chiplet技術將傳統的大型SoC分解成多個小型芯粒,增加了測試的復雜度。每個芯粒都需要進行獨立測試和驗證,以確保其功能和性能符合要求。此外,在將芯粒組合成完整的芯片系統后,還需要進行整體測試和驗證,以確保系統的穩定性和可靠性。因此,如何降低測試復雜度和提高測試效率成為Chiplet技術面臨的重要挑戰。

測試標準缺失

目前,Chiplet技術缺乏統一的測試標準和規范。不同制造商和設計師采用不同的測試方法和工具進行測試和驗證,導致測試結果的可比性和可信度降低。因此,如何制定統一的測試標準和規范成為Chiplet技術需要解決的關鍵問題。

(四)生態系統建設的挑戰

生態系統不完善

Chiplet技術需要一個完整的生態系統來支持其發展和應用。然而,目前Chiplet技術的生態系統還不完善,缺乏統一的設計工具、制造工藝和測試平臺等。這導致Chiplet技術的研發和應用受到一定限制。因此,如何完善Chiplet技術的生態系統成為其面臨的重要挑戰。

產業鏈協同問題

Chiplet技術涉及多個產業鏈環節,包括設計、制造、封裝和測試等。這些環節之間需要緊密協同和合作,才能實現Chiplet技術的有效應用和發展。然而,目前產業鏈各環節之間的協同和合作還存在一定問題,導致Chiplet技術的推廣和應用受到一定阻礙。因此,如何加強產業鏈協同和合作成為Chiplet技術需要解決的關鍵問題。

四、Chiplet技術的發展趨勢與展望

(一)技術發展趨勢

互連技術不斷創新

隨著Chiplet技術的不斷發展,互連技術將不斷創新和完善。未來,將出現更多高效、可靠的互連技術,以滿足Chiplet系統對高速互連和低延遲通信的需求。

封裝技術持續進步

封裝技術作為Chiplet技術的關鍵支撐之一,將持續進步和發展。未來,將出現更多先進、可靠的封裝技術,以實現Chiplet系統的高密度、低延遲互連和有效散熱。

測試與驗證技術不斷完善

隨著Chiplet技術的不斷發展和應用,測試與驗證技術將不斷完善和提高。未來,將出現更多高效、準確的測試方法和工具,以降低測試復雜度和提高測試效率。

(二)市場前景展望

市場需求不斷增長

隨著人工智能、物聯網、5G通信等新興技術的快速發展,對高性能、低功耗芯片的需求不斷增長。Chiplet技術憑借其獨特優勢,將在這些領域發揮重要作用,并迎來廣闊的市場前景。

產業鏈協同發展

未來,隨著Chiplet技術的不斷發展和應用,產業鏈各環節之間的協同和合作將不斷加強。這將有助于推動Chiplet技術的創新和發展,并促進整個半導體產業的進步和升級。

國際合作與競爭并存

在全球化背景下,Chiplet技術的國際合作與競爭將并存。一方面,各國將加強在Chiplet技術研發、制造和應用等方面的合作與交流;另一方面,各國也將在Chiplet技術市場上展開激烈競爭。這種國際合作與競爭并存的局面將有助于推動Chiplet技術的快速發展和應用。

五、結語

Chiplet技術作為一種創新的芯片設計理念,憑借其提高設計靈活性和可擴展性、降低設計成本和制造成本、提高芯片良率和可靠性以及加速產品上市時間和創新速度等優勢,在半導體領域展現出巨大的潛力和廣闊的前景。然而,Chiplet技術也面臨著互連技術、封裝技術、測試與驗證以及生態系統建設等方面的挑戰。未來,隨著技術的不斷創新和完善以及市場需求的不斷增長,Chiplet技術有望克服這些挑戰并實現快速發展。同時,國際合作與競爭也將推動Chiplet技術的不斷進步和應用拓展。

-

芯片

+關注

關注

459文章

51600瀏覽量

429879 -

soc

+關注

關注

38文章

4247瀏覽量

219935 -

chiplet

+關注

關注

6文章

438瀏覽量

12687

發布評論請先 登錄

相關推薦

KLA發布全新汽車產品組合以提高芯片良率及可靠性

評論