文章來源:學習那些事

原文作者:趙先生

在之前的文章中我們已經對集成電路工藝的可靠性進行了簡單的概述,本文將進一步探討集成電路前段工藝可靠性。

柵介質的經時擊穿(TDDB)

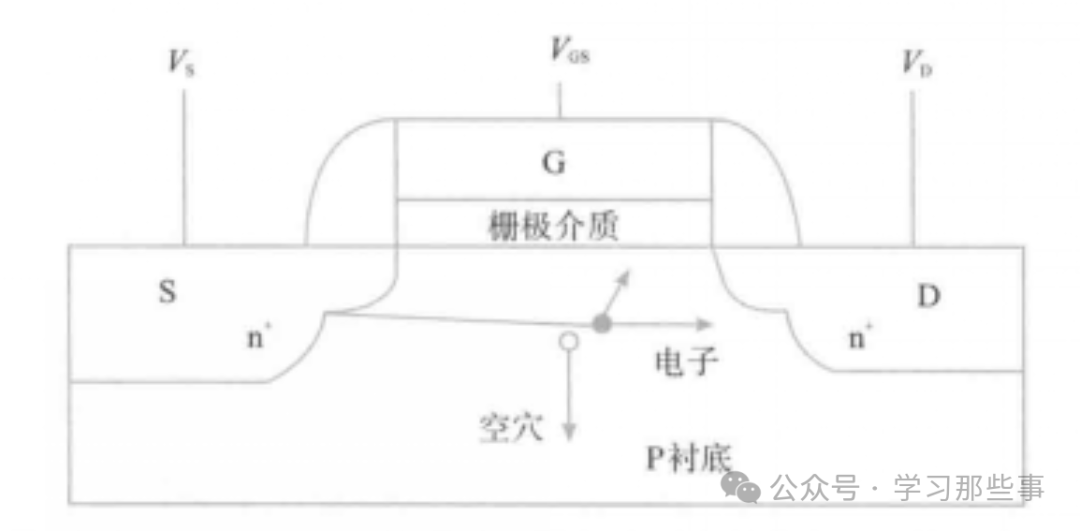

在MOSFET器件里,柵極介質處于極高的工作電場環境中,這使得柵介質經時擊穿(TDDB)成為集成電路里一種常見且極為關鍵的失效現象。具體來說,在強電場作用下,MOS器件的柵介質層會由于各種不同的原因,出現漏電或者被擊穿的情況,進而致使整個器件無法正常工作。

通常,其失效機制如下:參照圖1(a),在一段較長的時間里,缺陷不斷累積,伴隨著化學鍵的斷裂以及空位的產生。嚴重的電流問題最終引發災難性的熱失控,使得電介質層被擊穿。而局部出現的高密度電流以及由此產生的大量焦耳熱,會在電介質內部形成絲狀的導電通路。這會讓MOSFET器件中原本相互隔離的多晶硅柵極與襯底短路,進一步導致陽極和陰極短路,如圖1(b)所示。

圖1:失效機制

在過去,有兩種TDDB模型被廣泛用于解釋氧化物介質中電介質隨時間推移發生擊穿的失效機制。一個是電場驅動模型(E-Model或E-模型),另一個則是電流驅動模型(1/E- Model或1/E-模型)。

1.E模型

E模型也被叫做熱化學擊穿模型,它是基于共價鍵斷裂建立起來的分子模型。SiO?中的Si-O鍵有著很強的極性,大部分電子電荷會從Si原子轉移吸附到O原子附近,于是在帶正電的Si離子和帶負電的O離子之間,就會產生電偶極子運動。當在柵氧化層上施加外加電場E時,電偶極子運動就會在電場方向產生極化電場P。此時,電子在穿越氧化層時所受到的電場力,是外加電場和極化電場的總和,差不多是外加電場的兩倍。在這種局部強電場的持續作用下,分子的共價鍵會逐漸退化,直至最終斷裂。由此可見,即便沒有電流通過,只要有外加電場存在,柵氧化層最終也會出現退化并被擊穿的情況。

2. 1/E模型

1/E模型也被稱為空穴擊穿模型,其建立的基礎是福勒-諾德海姆(Fowler-Nordheim,F -N)隧穿電流。在早期,柵氧化層相對較厚,工作電壓也比較大。按照1/E模型的物理解釋,陰極端的電子會借助F-N隧穿效應進入到柵氧化層的導帶中,隨后在外加電場的作用下被加速。當電子獲得足夠的能量后,就會與SiO?晶格發生碰撞電離,進而導致Si-O鍵受到損傷,產生電子陷阱和空穴陷阱。這些空穴陷阱的存在,會使得局部缺陷處的電場強度和隧穿電流不斷增加,形成一個正反饋過程,促使缺陷持續增多,最終形成導電通道,將柵氧化層擊穿。

而在實際的柵介質擊穿過程中,這兩種機制是同時存在的。所以,在當下先進的集成電路工藝里,為了評估柵介質的可靠性,一般會采用將兩者相結合的電場-電流互補擊穿模型 。

3. Vg模型

Vg模型也被稱作陷阱產生模型。該模型指出,缺陷的產生與穿過柵氧化層的電子作用成正比,因此,所測量到的缺陷產生速率是施加在柵氧化層上電壓的指數函數。對于超薄氧化層而言,其經時擊穿模型遵循冪指數模型。具體過程為,隧穿電子在陽極端SiO?和Si的交界面釋放出H離子,這些H離子在外加電壓的驅使下穿過氧化層,并與氧化層內的缺陷相互作用,對氧化層造成損傷,最終形成歐姆導電通道,致使氧化層被擊穿。

4. 電場 - 電流互補擊穿模型

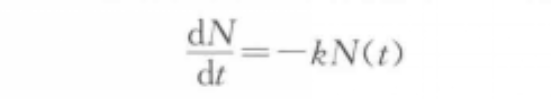

考慮到在柵介質擊穿過程中,電場誘導和電流誘導的電介質層退化機制會同時發揮作用,于是將場致退化和電流引發的退化整合到一個單一的TDDB模型中,“電場-電流互補擊穿模型”由此形成,且該模型與測試結果契合度很高。一般認為,這一失效模型中TDDB的根本原因在于價鍵斷裂、氧空位以及陷阱的形成。單位時間內價鍵斷裂概率方程如下:

式1

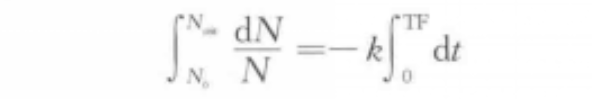

其中,N代表溝道與柵介質界面區域中Si-O鍵的數量;k是鍵斷裂率常數。對上述方程中的變量進行分離并積分,可得到:

式2

其中,TF表示失效時間,fcrit=(N/N0)crit是價鍵被破壞并最終導致器件失效的臨界比例。通常認為,只需相對少量的鍵被打破,就會引發介質擊穿,所以fcrit預計僅略小于1。

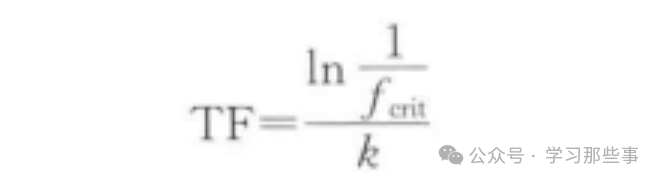

由上述積分后的方程可得出:

式3

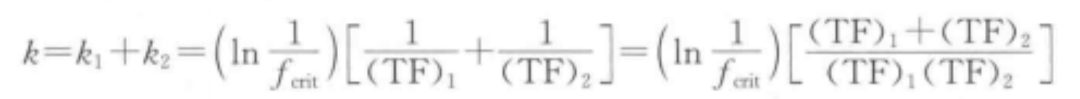

倘若存在兩個相互獨立的鍵斷裂機制k1和k2,那么假設總反應速率常數k是它們的總和,即k = k1 + k2,此時總反應速率變為:

其中,(TF)?和(TF)?分別是對應于鍵斷裂機制k?和k?的失效時間。結合式3和上述總反應速率方程式4,能夠得到:

式5

上述失效時間(TF)方程適用于相互獨立卻同時作用的退化機制。由此可知,如果(TF)?大于(TF)?,那么失效時間TF完全由(TF)?主導,反之亦然。對于TDDB來說,當電場E高于10MV/cm時,基于電流的1/E模型可能在TDDB過程中占據主導;而當電場E在10MV/cm以下時,陽極空穴注入相對較少,電場主導的E模型可能在TDDB中占據主導地位。因此,結合E模型和1/E模型的物理特性,柵介質擊穿時間可由式6描述:

式6

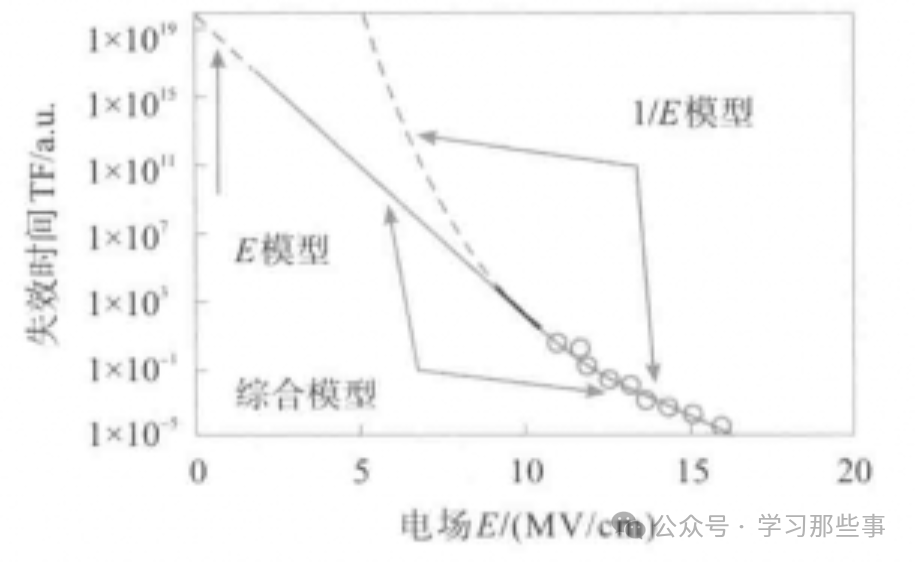

如圖2所示為單一失效時間TF模型,它將基于場的E模型和基于電流的1/E模型合并成一個模型。在很高的電場(E>10MV/cm)下,電流誘導的退化起主導作用;而在較低的電場(E<10MV/cm)下,電場誘導的退化占主導地位。

圖2:E模型和 I/E 模型合并后得到的單一失效時間模型

盡管E模型已被廣泛應用,并且在描述厚度大于4.0nm厚膜的低場TDDB數據方面頗為成功。然而,對于非常薄的氧化物(<4.0nm)而言,這些薄膜中的直接隧道電流可能會顯著高于傳統氧化物介質。這或許意味著,超薄氧化物薄膜中的失效更多是由電流注入而非電場作用所導致的。此外,不能僅僅將TDDB看作是MOSFET柵極氧化物或電容器氧化物特有的問題。實際上,在后段工藝中,隨著低介電常數電介質的引入,互連的TDDB問題同樣值得關注。

在介質內部,柵電流主導的空穴捕獲現象對化學鍵斷裂過程具有催化作用,進而在缺陷形成以及介質擊穿的過程中扮演著關鍵角色。空穴一旦被捕獲,會致使Si-O 鍵的結合能大幅下降。而鍵能的降低使得化學鍵在電場與熱的共同作用下,更容易發生斷裂。鑒于E模型在幾乎所有情形下都能適用,因而普遍將其視作最為保守的TDDB模型。相對來說,互補模型則成為人們評估TDDB的最優選擇。

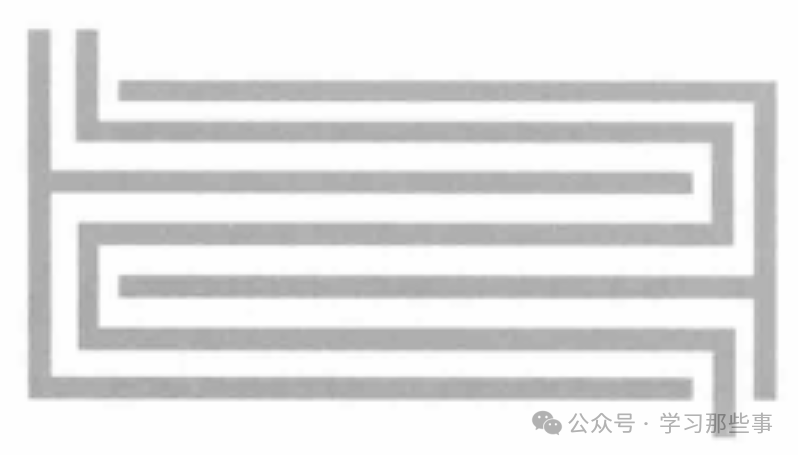

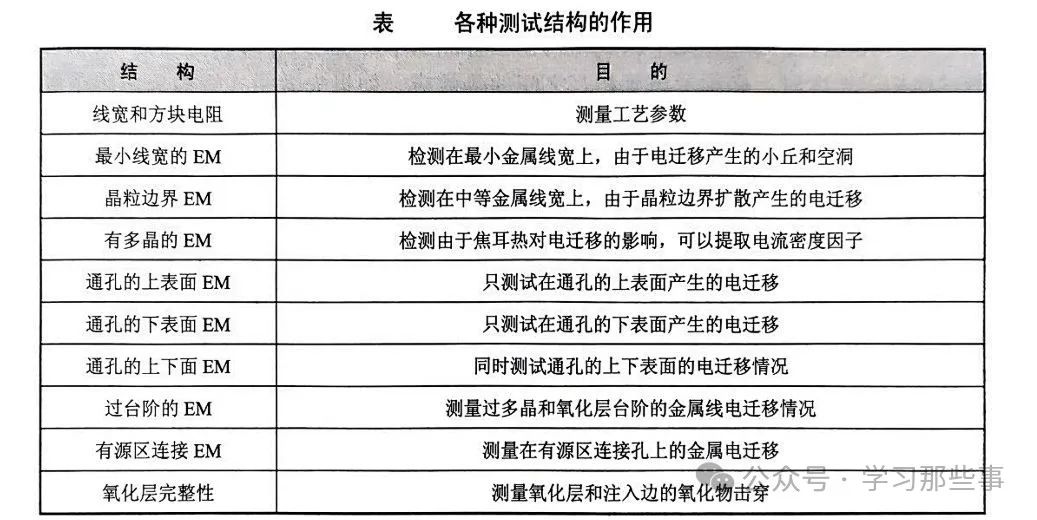

互連電介質的TDDB數據,一般借助梳狀 - 梳狀或者梳狀 - 蛇形測試結構來采集,如圖3所示。此結構屬于具有最小間距(即最小線寬與最小間距之和)的梳狀蛇形測試結構。針對該結構所開展的擊穿強度測量,或者獲取的TDDB數據,能夠作為評判該互連 - 介電結構性能優劣的關鍵指標。雖說低介電常數介電材料能夠有效減少電路延遲,顯著提升互連性能,然而在泄漏電流以及擊穿強度等方面,相較于傳統氧化物介質,它們在電學可靠性方面正面臨著嚴峻的挑戰。

圖3:一種互連電介質測試結構

熱載流子注入(HCI)

當載流子在強電場環境中運動時,若其從電場獲取的能量大于在散射過程中與晶格原子碰撞所損失的能量,載流子的平均動能便會顯著超出熱平衡載流子的平均動能,此時載流子具備高于熱能(kT)的能量,這種類似于被“加熱”的載流子被稱作熱載流子。溝道熱載流子注入(HCI)描述的是電子(或者空穴)沿著MOSFET的溝道加速,進而獲取足夠動能的過程(見圖4)。這些載流子能夠跨越存在于Si/SiO?界面處的3.1eV勢壘(針對電子而言)或者4.7eV勢壘(針對空穴而言),進入到氧化層陷阱當中。當溝道電子從源極向漏極加速時,它們能夠獲取進入SiO?層所必需的能量,尤其是那些處于玻爾茲曼分布尾部附近的“幸運電子”。由于MOSFET器件漏極附近的溝道電場最強,晶格電子在此處也極有可能發生碰撞電離,這些熱載流子隨后被散射至柵極氧化物。HCI會對界面造成損害,極有可能產生界面態。

圖4:沿NMOSOFT溝道移動的載流子從源極到漏極的加速過程

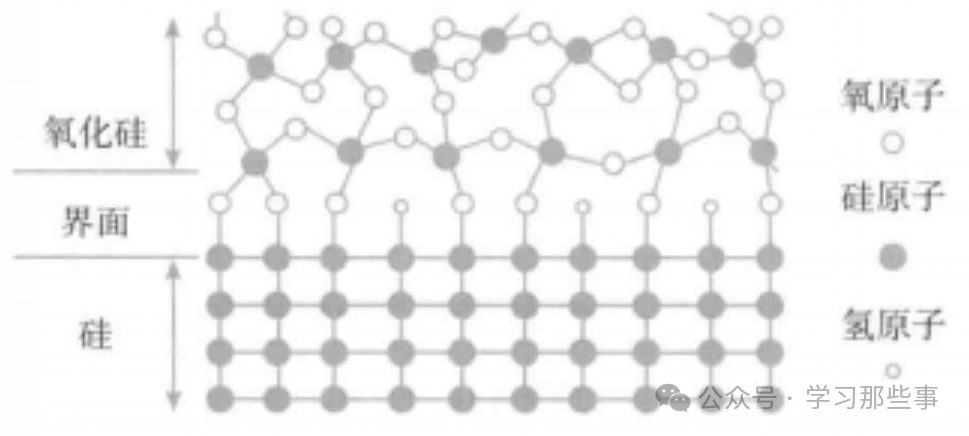

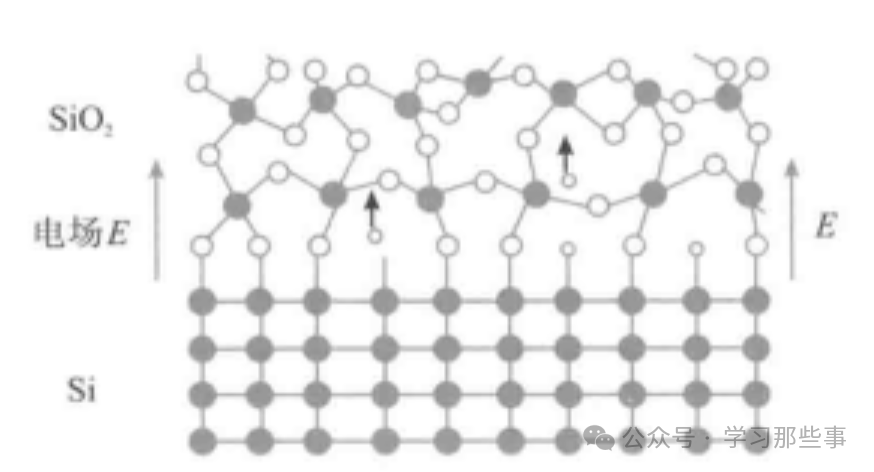

在這種HCI機制的作用下,界面態的生成以及電荷捕獲現象會導致晶體管參數出現退化,特別是在先進技術中,載流子加速的溝道電場的增加速度要快于工作電壓的降低速度。所以,HCI可能成為一種對MOSFET造成退化的重要機制。鑒于MOSFET屬于場效應器件,硅襯底與SiO?柵介質之間的界面顯得尤為關鍵。通常情況下,該界面處的鍵斷裂退化現象,會致使器件的穩定性受到影響,如圖5所示。

圖5:硅襯底和 Si0:柵極電介質之間的界面

硅襯底里的硅原子在晶格中構建起金剛石般的結構。而SiO?層呈現非晶態結構,一個硅原子與四個相鄰的氧原子形成化學鍵,每個晶格拐角處的氧原子則與相鄰的兩個硅原子相連。由于界面處晶格結構存在不匹配情況,并非所有硅鍵都能實現完美匹配,進而產生硅懸空鍵。一般在MOSFET制造環節會引入氫元素,用于鈍化這些懸空鍵,防止它們帶電。接下來將探討Si/SiO?界面處化學鍵斷裂對MOSFET的影響。在SiO?剛形成時,SiO?內部以及Si/SiO?界面就已存在一些斷裂的鍵,部分Si-O鍵的結合能也較弱。依據費米能級的位置,這些懸空鍵可被視作電子陷阱、空穴陷阱,也可能呈中性狀態。在MOSFET運行期間,這些陷阱、懸掛鍵會被電子、空穴填充,進而導致MOSFET的性能參數出現退化。對于MOSFET的可靠運作而言,界面穩定性至關重要。要是熱載流子注入破壞了界面處的Si - H鍵,形成帶電的Si懸空鍵,將會使MOSFET的工作參數發生退化。所以,為確保MOSFET穩定工作,界面必須維持相對穩定狀態。

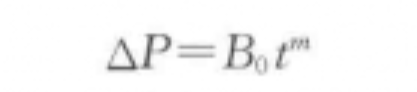

把某種特性P(比如Vth、gm、Idsat等)按時間t進行泰勒級數展開,由HCI導致的晶體管特性退化能夠描述為:

式7

其中,B是與材料和器件相關的參數;m是HCI時間相關性的冪律指數,屬于可調擬合參數,一般取值m≈0.5 。

針對N型MOSFET器件的熱載流子注入(HCI)效應,其物理機制如圖6所示:在漏極附近的高場區域,高能電子引發碰撞電離效應,伴隨生成電子-空穴對。其中,部分高能電子被Si/SiO?界面勢壘捕獲,在漏端附近微區誘發界面陷阱積累;而空穴則向襯底漂移形成特征電流Isub。值得注意的是,該襯底電流雖非直接損傷因子(實際致損機制為柵極電流引發的界面氧化層擊穿),但因其與損傷程度的正相關性(相關系數>0.92),在工程測量中常作為等效應力參數。相較于需精密探針臺的柵極電流測試,Isub的檢測可通過集成襯底接觸直接獲取,這種測試便捷性使其成為工藝監控的關鍵指標。

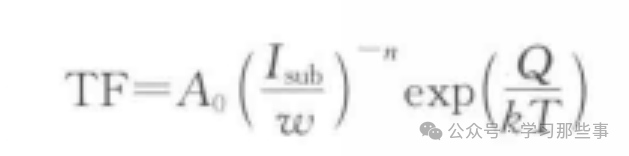

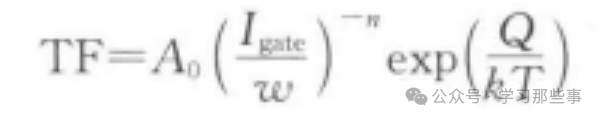

通常用于計算N溝道晶體管的失效時間(TF)的表達式為

式8

Isub是應力期間的峰值襯底電流;w是晶體管的寬度;n是冪律指數,約等于3;Q是激活能,與溝道長度相關,一般在-0.25 ~ +0.25eV;A?是與器件相關的參數,因器件不同而不同,會產生與失效時間相關的分布;k是玻爾茲曼常數;T為絕對溫度。

將峰值襯底電流I???除以晶體管寬度w,使得Isub / w成為真正意義上的應力,即大致與器件寬度無關。HCI的激活能較小,依據溝道長度可為正值也可為負值。通常僅在柵極長度小于0.25μm時才會觀察到正值激活能。

從歷史情況來看,由于空穴遷移率較低,且空穴注入勢壘高度增加,P型MOSFET的HCI問題不太受關注。對于P溝道器件,有時柵極電流Igate是衡量器件實際應力的更優指標。因此,對于P溝道器件,HCI的失效時間方程一般寫成:

式9

Igate是應力期間的峰值柵極電流;w是晶體管的寬度;n為冪律指數,一般在2-4之間;Q為激活能,通常在-0.25eV到+0.25eV 之間。

對于長溝道MOSFET,HCI退化建模通常采用N管峰值襯底電流Isub、P管峰值柵極電流Igate作為應力指標。在納米工藝中,HCI誘導的電子俘獲會直接衰減N管載流子遷移率,導致驅動電流下降。

盡管晶體管級的退化測量已較成熟,但IC失效預測仍存在兩大難點:其一,實際電路中晶體管承受最大應力的時間占比可能極低(如高速開關管占空比<10%);其二,需明確電路參數(速度/功耗/漏電流)允許的晶體管退化閾值(5%-20%不等)。這些問題需要結合電路工作特性與架構冗余度進行綜合評估。

鑒于上述種種因素,在某些情形下,采用經驗方法來判定HCI對電路工作的影響,反而顯得更為簡便且精準。在這種經驗手段中,先對IC內的器件進行抽樣,隨后在高于預期工作電壓的電壓水平下,針對器件與電路展開工作壽命測試。接著,將器件和電路級別的退化狀況記錄為應力時間的函數。借助從上述模型中能夠輕松提取的加速因子,便可預測電路在正常運行階段預計會出現怎樣的退化情況。

負偏壓溫度不穩定性退化

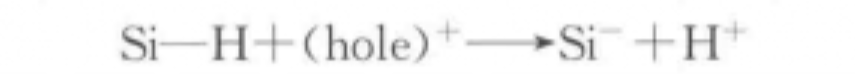

負偏壓溫度不穩定性(NBTI)是集成電路可靠性的主要威脅之一。PMOS 晶體管在高溫負柵壓下會發生退化,表現為閾值電壓絕對值升高,伴隨遷移率、漏電流和跨導的衰減。這種退化源于 Si/SiO?界面(圖 7)的 Si-H 鍵斷裂 —— 當器件工作時,界面處的 Si-H 鍵斷裂產生懸掛鍵,直接導致性能劣化直至失效。由于 PMOS 在負柵壓下工作,SiO?內部電場由界面指向柵極,若 Si-H 鍵斷裂釋放 H+,離子會向遠離界面方向漂移,這解釋了為何 PMOS 的 NBTI 問題比 NMOS 的正偏壓溫度不穩定性(PBTI)更顯著。不過在高 κ 柵介質器件中,PBTI 仍是需重點關注的退化機制。目前認為,Si-H 鍵斷裂與工作時的空穴捕獲相關,可能的反應式為:

式10

其中,Si-H代表正常的Si-H鍵;hole代表空穴;Si代表硅懸掛鍵;H?代表釋放出的氫離子(質子)。由于存在電場作用,如圖7所示

圖7:P型MOSFET的Si/SiO?界面

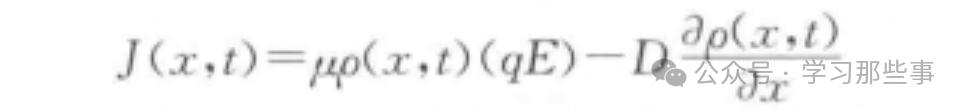

P型MOSFET在負柵極電壓下工作,所以SiO?層中的電場方向背離界面。若在器件工作時Si-H鍵斷裂并釋放出H?,其漂移方向會遠離Si/SiO?界面,也就是說上述反應產生的任何H?都趨向于離開Si/SiO?界面。一旦H?產生,其輸運方程為:

式11

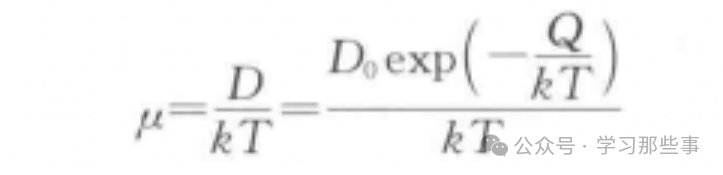

ρ(x,t)是H?在任意時刻t、在距界面x處的濃度;D是H?的擴散系數;qE是作用在H?上的電場力;μ是H?的遷移率,D和μ通過愛因斯坦關系與擴散系數相關:

式12

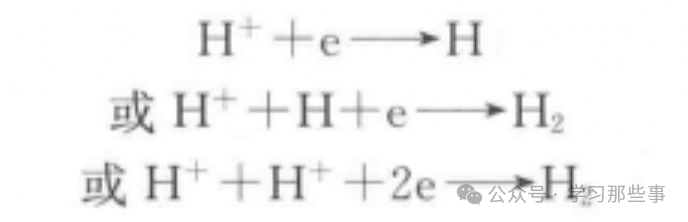

從式11可以發現,由于電場E的存在,H?會朝著遠離界面的方向移動,使得SiO?內部H?濃度逐步上升。隨著SiO?電介質中H?濃度不斷累積,可能出現H?向界面回流的情況。實際情形中,若電場消失(電場力為零),H?回流便會發生,進而讓部分器件性能得到恢復。但H?通常不會完全回流至界面,因為在SiO?柵極電介質內,部分H?可能會參與還原反應。可能存在的還原反應類型如下:

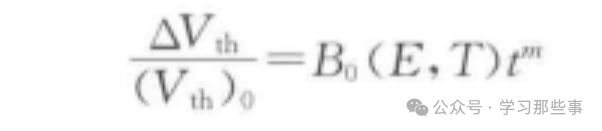

NBTI對P型MOSFET器件電學特性的影響十分突出:器件閾值電壓會產生偏移,反型溝道內的空穴遷移率下降。Vth偏移與遷移率降低,均會導致器件溝道電流(I)減小,進而引發器件性能劣化。閾值電壓Vth隨時間變化的表達式為:

式13

其中,B0(E, T)是與電場E、溫度T相關的因子;m為時間t的冪指數,取值通常在0.15 - 0.35范圍內,一般取m = 0.25。

由于與時間關聯的指數m小于1,隨著時間延續,退化現象會趨向飽和。從圖7所示模型中,能夠推測出這種退化的飽和趨勢。鑒于Si-H鍵數量有限,未斷裂的Si-H鍵會隨時間減少,由Si-H鍵斷裂引發的器件退化速率也會隨之降低。

-

集成電路

+關注

關注

5405文章

11728瀏覽量

364879 -

MOSFET

+關注

關注

148文章

7598瀏覽量

215652 -

工藝

+關注

關注

4文章

629瀏覽量

29031

原文標題:集成電路前段工藝的可靠性

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

集成電路芯片封裝技術教程書籍下載

半導體集成電路的可靠性設計

集成電路可靠性檢查的最佳實踐方案

集成電路封裝可靠性設計

等離子體蝕刻工藝對集成電路可靠性的影響

評論