什么是閂鎖(Latch-up)?

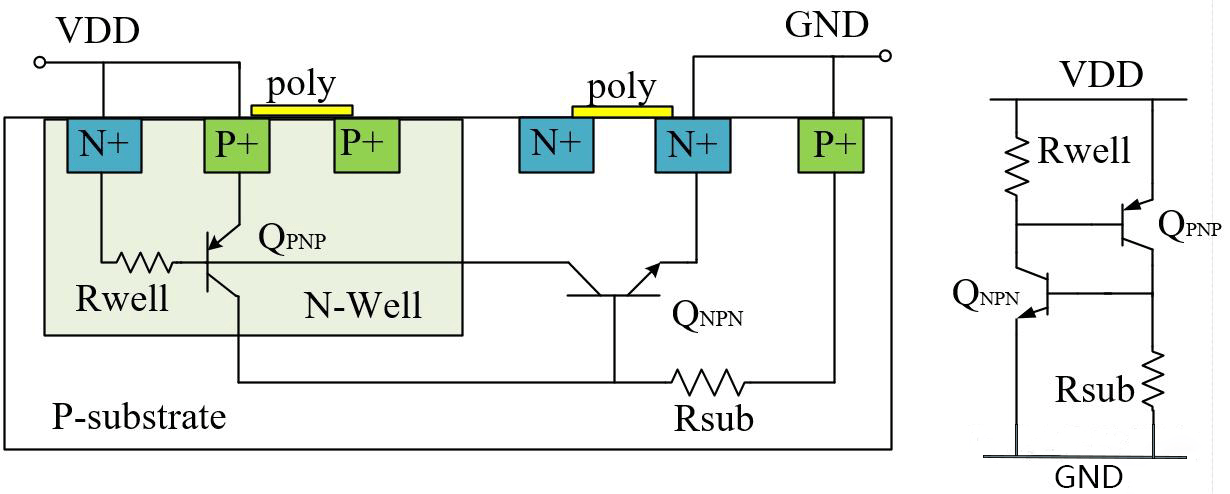

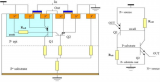

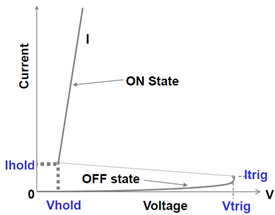

CMOS 工藝中的寄生晶閘管(SCR)結構,是由 NMOS 和 PMOS 的寄生 NPN/PNP 晶體管相互連接形成的。這些寄生晶體管平時處于關閉狀態,但當受到電壓尖峰、靜電干擾或高溫時,會觸發正反饋環路,導致電流在芯片內部無限放大,最終燒毀芯片或迫使系統斷電。這一現象即為閂鎖效應。

CMOS結構(左)及其等效電路(右)

如何快速判斷電路是否存在閂鎖?

如果遇到以下情況,可能是閂鎖在作祟:

l 電流突然激增:芯片耗電猛增,遠超正常工作電流。

l 電壓突然暴跌:電源電壓“斷崖式下跌”, 導致芯片復位或功能紊亂。

l 高溫更易崩潰:芯片在高溫環境下(如>85℃)更容易觸發閂鎖。

檢測方法:

l 靜電測試:模擬人體接觸放電,驗證芯片抗ESD能力(IEC 61000-4-2)。

l 浪涌測試:模擬雷擊或電源波動,測試電路穩定性(IEC 61000-4-5)。

l 電腦模擬:用仿真工具(如TCAD)預判寄生結構的觸發閾值,優化設計。

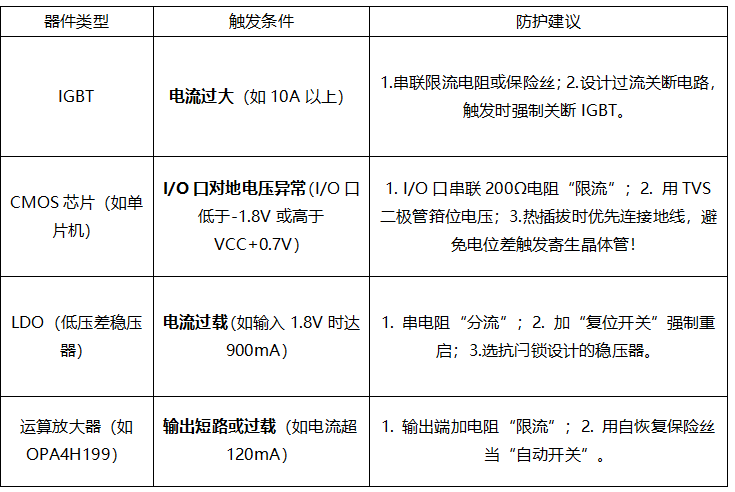

不同器件的“觸發門檻”與防護方案:

雷卯電子的“防閂鎖武器庫”

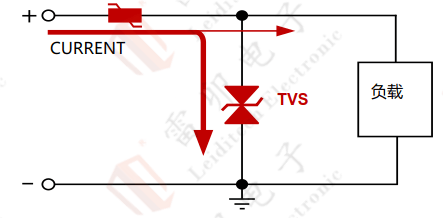

l TVS二極管:納秒級響應,將電壓尖峰箝位至安全閾值,防止寄生晶體管觸發。

l 自恢復保險絲(PPTC):過流時自動斷開電路,故障排除后自動復位,避免持續損壞。兩者協同可阻斷閂鎖觸發條件。

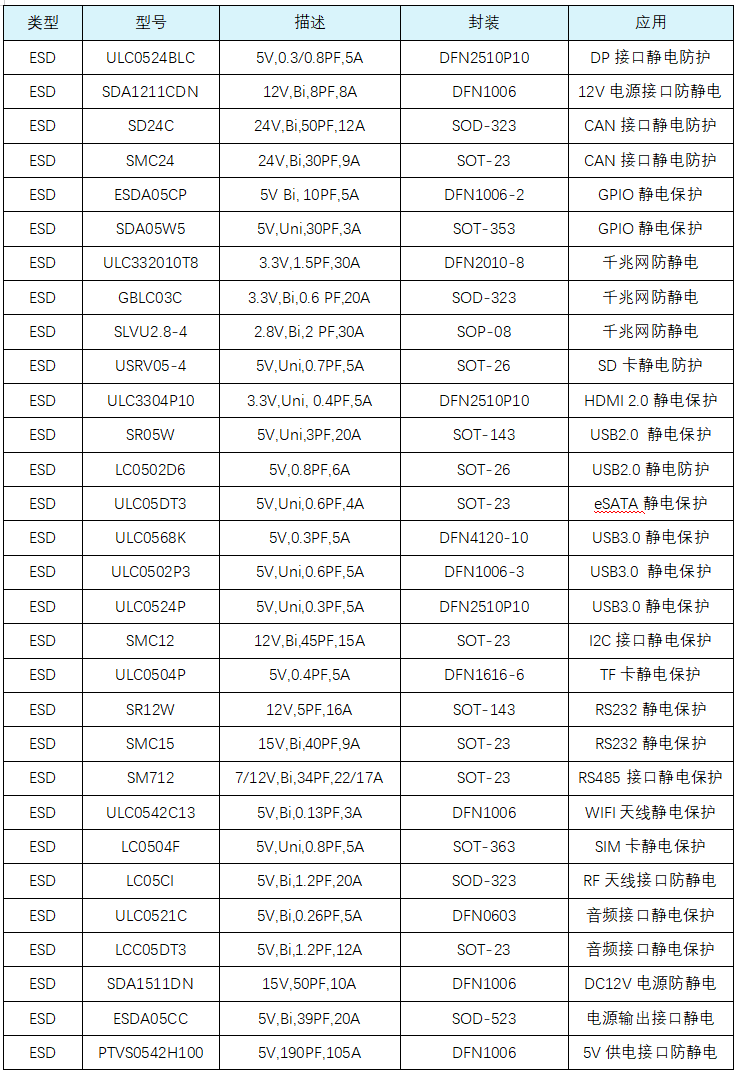

2. 低電壓/高速接口:ESD靜電防護

l 低電容ESD器件:像“防靜電外套”一樣,包裹芯片接口,防止靜電“電擊”觸發閂鎖,同時不影響信號速度(如USB、HDMI)。

雷卯推薦的“防閂鎖武器”清單,按場景選擇,簡單有效,詳細方案可關注雷卯電子公眾號或聯系雷卯EMC小哥

總結:防閂鎖三板斧

1. 設計時“防微杜漸”:

l 電源去耦:芯片電源引腳并聯0.1μF陶瓷電容,抑制電壓毛刺。

l 布局優化:縮短敏感信號線長度,減少寄生電容耦合;增加襯底和阱的接地接觸,降低寄生電阻。。

l 版圖設計:在I/O區域添加Guard Ring(環形接地層),阻止載流子擴散觸發閂鎖。

2. 器件選型“硬核防御”:

l 高功率接口選TVS,PPTC防過流,低壓高速信號選ESD,像給電路穿“防彈衣”。

3. 雷卯“定制服務”:

l 遇到復雜場景?雷卯技術團隊可量身定制方案,像“電路醫生”一樣對癥下藥!

Leiditech雷卯電子致力于成為電磁兼容解決方案和元器件供應領導品牌,供應ESD,TVS,TSS,GDT,MOV,MOSFET,Zener,電感等產品。雷卯擁有一支經驗豐富的研發團隊,能夠根據客戶需求提供個性化定制服務,為客戶提供最優質的解決方案。

審核編輯 黃宇

-

CMOS

+關注

關注

58文章

5841瀏覽量

236957 -

閂鎖效應

+關注

關注

1文章

33瀏覽量

9456

發布評論請先 登錄

相關推薦

閂鎖效應的工作原理

一文搞懂閂鎖效應:電路里的“定時炸彈”與防護指南

解決電路噪聲難題:《電路噪聲防護與優化設計技術白皮書》工程師必備的全面指南

【「典型電子電路設計與測試」閱讀體驗】文氏橋正弦波振蕩電路

0.4KV~35KV中低壓配電系統中ARB6電弧光保護裝置的應用

人員睡崗檢測 AI 算法攝像機

地質災害監測預警解決方案:準確守護,全天候護航

SMT錫珠:影響與對策 —— 打造高質量電子電路板

當尋呼機變“定時炸彈”:如何防范電子設備被惡意篡改

一文搞懂DDR內存原理

濾波電路在電磁脈沖防護中的效應探究

一文搞懂閂鎖效應:電路里的“定時炸彈”與防護指南

一文搞懂閂鎖效應:電路里的“定時炸彈”與防護指南

評論