本文作者:Jonathan Dodge, P.E.

安森美 (onsemi)cascode FET (碳化硅共源共柵場效應晶體管)在硬開關和軟開關應用中有諸多優勢,SiC JFET cascode應用指南講解了共源共柵(cascode)結構、關鍵參數、獨特功能和設計支持。本文為第一篇,將重點介紹Cascode結構。

Cascode簡介

碳化硅結型場效應晶體管(SiC JFET)相比其他競爭技術具有一些顯著的優勢,特別是在給定芯片面積下的低導通電阻(稱為RDS.A)。為了實現最低的RDS.A,需要權衡的一點是其常開特性,這意味著如果沒有柵源電壓,或者JFET的柵極處于懸空狀態,那么JFET將完全導通。

然而,開關模式在應用中通常需要常關狀態。因此,將SiC JFET與低電壓硅MOSFET以cascode 配置結合在一起,構造出一個常關開關模式“FET”,這種結構保留了大部分SiC JFET的優點。

Cascode結構

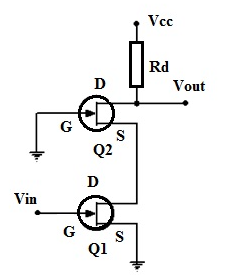

共源共柵(Cascode)結構是通過將一個SiC JFET與一個低壓、常關的硅(Si)MOSFET串聯而成,其中JFET的柵極連接到MOSFET的源極。MOSFET的漏源電壓是JFET柵源電壓的反相,從而使cascode 結構具有常見的常關特性。該結構可在額定漏源電壓范圍內阻斷電流,但如同任何MOSFET(無論是硅基還是碳化硅基器件)一樣,其反向電流始終可以流通。

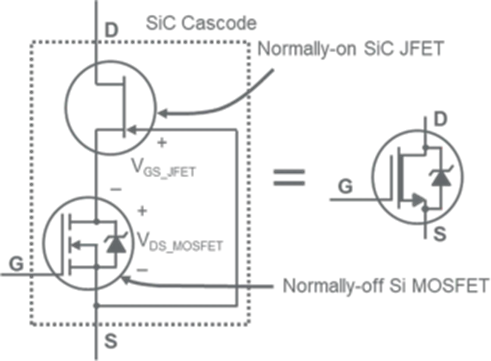

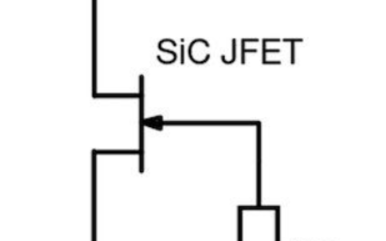

圖 1 Cascode配置

當內部MOSFET導通或有反向電流流過時,不論cascode的柵極電壓如何,JFET的柵極-源極電壓幾乎為零,JFET處于導通狀態。當MOSFET關斷且cascode兩端存在正的VDS(漏源電壓)時,MOSFET的VDS會增加,與此同時JFET的柵源電壓會降低至低于JFET的閾值電壓,從而關斷 JFET。請參見圖1。

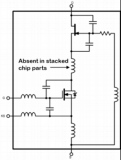

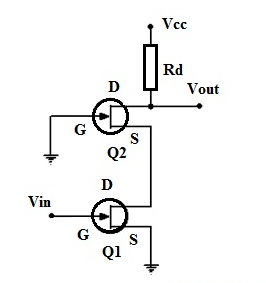

圖 2 分立cascode結構

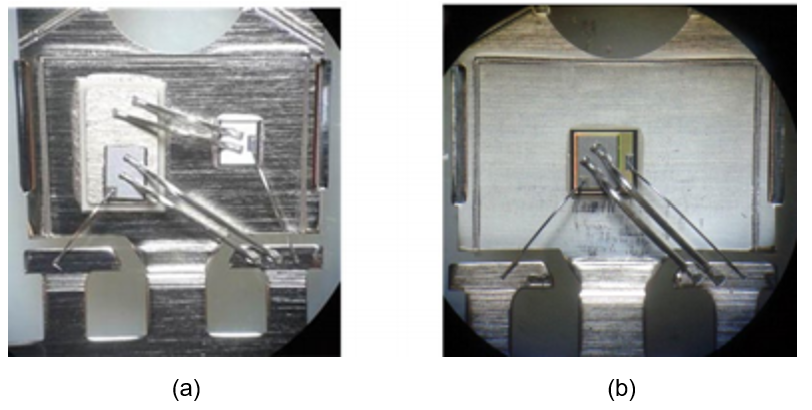

分立cascode 結構采用并排芯片,如圖 2(a)所示,或堆疊芯片,如圖 2(b)所示。在這兩種情況下,SiC JFET 通常都是銀燒結在封裝引線框架上。

在并排配置中,MOSFET 安裝在一個金屬鍍層的陶瓷隔離器上,有兩組源極連接線:一組連接 JFET 源極和 MOSFET 漏極(金屬鍍層陶瓷的頂面),另一組連接 MOSFET 源極和源極引腳。在堆疊芯片配置中,JFET 源極和 MOSFET 漏極之間的連接線被取消,從而減少了雜散電感。并采用直徑較小的連接線連接 JFET 和 MOSFET 柵極。

該MOSFET專為cascode結構設計,其有源區雪崩電壓設定約為25V。MOSFET基于30V 硅工藝制造,具有低導通電阻RDS(on),通常僅為JFET的10%,并且具有低反向恢復電荷QRR等特性。JFET用于阻斷高電壓。大部分的開關和導通損耗都集中在JFET上。

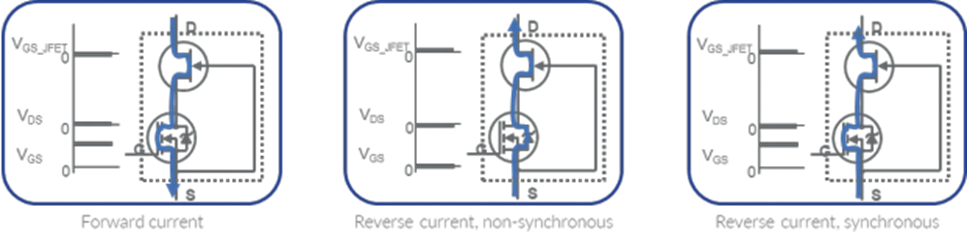

圖 3 Cascode正向和反向電流操作

Cascode的導通電阻RDS(on)包括 SiC JFET 和低壓Si MOSFET 的導通電阻。cascode柵極關斷時,反向電流流經 MOSFET 體二極管,從而自動導通 JFET,如圖 3(b)所示的非同步反向電流情況。

在這種情況下,源極-漏極電壓為 MOSFET 體二極管壓降加上 JFET 導通電阻的壓降。由于cascode內的 MOSFET 由硅制成,因此柵極關斷時的源極-漏極電壓不到同類 SiC MOSFET 的一半。當柵極導通時,cascode結構在正向和反向電流下具有相同的導通損耗。

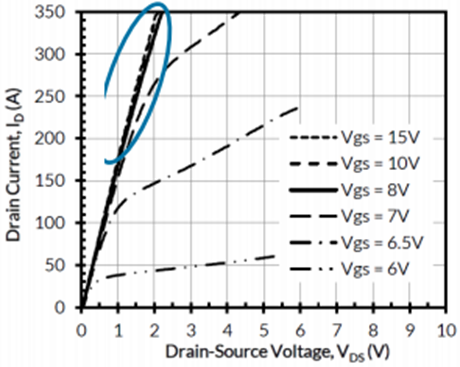

Cascode的柵極電壓范圍非常靈活,原因有二。首先,柵極是 MOSFET 柵極,在室溫下閾值電壓接近 5 V,無需負柵極電壓。柵極電壓范圍為±20 V,且不存在閾值電壓漂移或遲滯風險,同時內置了柵極保護齊納二極管。其次,cascode具有高增益。圖 4 顯示了采用 TOLL (MO-229) 封裝的 750 V、5.4 mΩ第 4 代堆疊芯片結構的cascode—— UJ4SC075005L8S 在 25 °C的輸出特性曲線。

圖 4 Cascode的高增益可實現 10 V 柵極驅動

請注意,當cascode柵源電壓超過約 8 V 時,其電導率的變化非常小。一旦MOSFET導通,JFET即完全導通。這意味著cascode可以用 0 至 10 V 的自舉電壓來驅動,從而最大限度地降低柵極驅動器的功率和成本。 另一方面,更寬的柵極電壓范圍(如 -5 至 +18 V)也不會對器件造成損害。

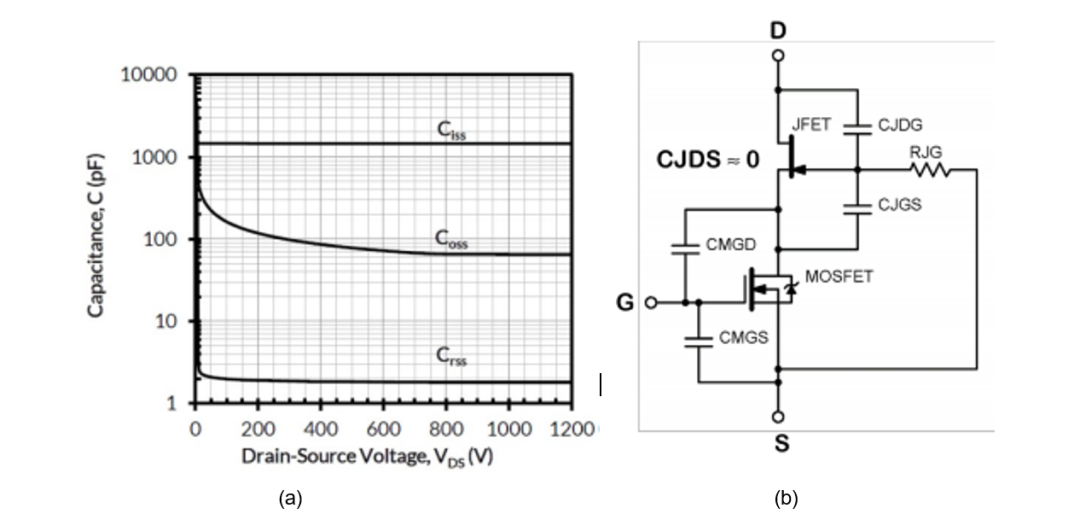

圖 5 Cascode電容

圖 5(a) 顯示了 MOSFET 和 JFET 的芯片電容變化曲線。請注意,圖 5(b) 中的 JFET 柵極電阻 RJG 并不是一個單獨的電阻,而是 JFET 芯片的一部分。cascode與其他功率晶體管的一個主要區別是沒有柵漏電容。當漏源電壓VDS超過JFET閾值電壓后,Crss實際上會降至零。這是因為 JFET 沒有漏極-源極電容(既沒有 PN 結,也沒有體二極管來產生這種電容)。

這意味著在開關電壓轉換過程中,cascode的 dVDS/dt 主要由外部電路而不是cascode柵極電阻決定。Cascode的 MOSFET 開關速度可通過其柵極電阻調節,而 JFET 的開關速度部分由 MOSFET 決定,部分則由外部電路決定。這解釋了為何在硬開關情況下,cascode結構需借助漏源緩沖電路(snubber)來控制關斷速度并抑制電壓過沖,下文將對此進行說明。所有 JFET 輸出電容(包括柵漏電容與漏源電容)都是柵漏電容。cascode輸出電容 Coss約等于 JFET 柵極-漏極電容。cascode輸入電容 Ciss主要來自cascode的 MOSFET 柵極-源極電容。

未完待續,后續推文將介紹Cascode開關特性。

-

MOSFET

+關注

關注

148文章

7690瀏覽量

216074 -

安森美

+關注

關注

32文章

1737瀏覽量

92456 -

晶體管

+關注

關注

77文章

9873瀏覽量

139720 -

SiC

+關注

關注

30文章

3028瀏覽量

63671 -

共源共柵

+關注

關注

0文章

24瀏覽量

10461

原文標題:SiC 市場的下一個爆點:共源共柵(cascode)結構詳解

文章出處:【微信號:onsemi-china,微信公眾號:安森美】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

安森美SiC Cascode JFET的背景知識和并聯設計

超共源共柵簡史

折疊共源共柵放大器的優缺點

安森美SiC cascode JFET并聯設計的挑戰

評論