一個高速器件放在一堆低速電路中,其信號完整性的問題會比較突出;而一個低速器件放在一堆高速電路中, 其驅動能力的問題就會顯得比較突出。 為什么, 請看 “案例: 驅動能力不足造成的時序錯誤”。另外, 也有器件選型和匹配方案不當帶來的驅動能力問題, 當器件驅動的信號沿大大超出其翻轉速率時,所帶來的問題除了信號沿變緩外,還可能造成信號擺幅變小,閾值電平違規等。詳見“案例:錯誤的設計帶來的驅動能力問題”。

1 案例:驅動能力不足造成的時序錯誤

一塊單板,設計有 DSP 和 FPGA。 FPGA 的加載模式設置為 Slave Serial 模式,上電時 DSP 從外掛FLASH 中讀取 FPGA 的 bit 文件,并加載 FPGA。發現的故障是: FPGA 加載有一定失敗的概率。

示波器監測 FPGA 的 INIT_B 信號,發現該信號在加載數據過程中會拉低且無法恢復。(正常流程該信號只在加載初始化時輸出低脈沖)。 INIT_B 信號在加載數據過程中拉低,表示 FPGA 檢測到了數據CRC 出錯。分別導出 FPGA 加載成功和加載失敗兩種情況下, DSP 從 FLASH 中讀到 SDRAM 中的 bit文件,并進行比較,發現二者有少量字節有差異。由此判斷, DSP 在將 FPGA 加載數據從 FLASH 向SDRAM 搬移的過程中,出現了誤碼。 DSP 本身的程序運行依賴于 SDRAM,如果 SDRAM 訪問有問題,DSP 應該容易跑飛。鑒于故障復現時未發生 DSP 跑飛的現象,我們把排查的重點放在讀 FLASH 的過程上。

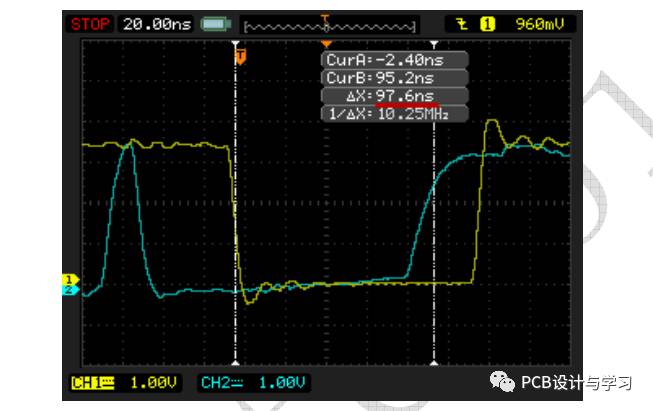

硬件電路上, FLASH 掛在 DSP 的本地總線上,作為異步存儲器被 DSP 訪問, FLASH 的標稱訪問時間是 90ns,依此來檢查 DSP 對 FLASH 空間的時序配置,讀數時的建立保持時間應該都是足夠的。但經過實測發現,建立時間的時序裕量為負值。究其因,是因為 FLASH 輸出的信號沿太緩,幾乎達到了 20ns,如圖 14通道二波形。這樣緩的信號沿,直接導致了 FLASH 訪問時間的延長,超過了 97ns。

找到問題根源后,根據測量結果修改 DSP 對 FLASH 空間的異步時序配置,以保證足夠的裕量,問題便迎刃而解了。在一個總線頻率超過 50MHz 的處理器系統中, FLASH 相對來說屬于較低速的器件,其管腳驅動能力也較弱。如果處理器總線上掛的負載比較多,由于容性負載的增大, FLASH 驅動總線時,其輸出信號沿勢必會變得更緩。而信號沿變緩帶來的額外延時,往往容易被忽略。設計者在處理類似的接口時,應該充分考慮各種可能給時序帶來沖擊的參數,以保證接口的穩定可靠。

2 案例:錯誤的設計帶來的驅動能力問題

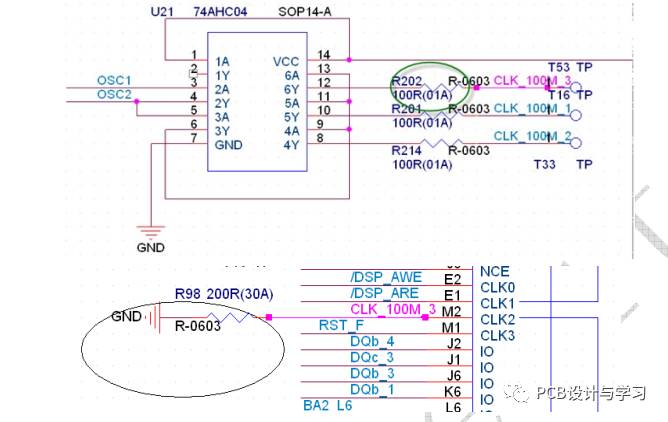

一個 100MHz 時鐘,由晶體驅動反相器 74AHC04 產生,作為 FPGA 的時鐘全局時鐘使用。 FPGA的管腳電平設置為 LVTTL33。電路工作過程中,發現 FPGA 工作紊亂,將時鐘引出測量,時有時無,很不穩定。測量 100MHz 時鐘輸入,發現高電平只有 1.5V 左右。該電平無法保證被 FPGA 正確識別為高。這是一個典型的工程師經驗不足造成的原始設計缺陷。分析這個 100MHz 時鐘的原理圖 (如圖 15),1 分鐘內發現三個問題:1.最大的問題,反相器的選型: 74AHC04 能保證的輸出信號翻轉率很緩(規格書標稱的最小翻轉斜率為 100ns/V),也就是說,這個電路實際是在用一個低速器件驅動一個高速信號。這樣的直接結果便是導致其輸出 100MHz 信號時幅度不夠;2.源端使用了一個 100ohm 的串阻,負載端使用了一個 200ohm 的并行匹配,從阻抗連續的觀點來看, 這種取值起不到阻抗匹配的作用。并行匹配用于 LVTTL/LVCMOS 電平, 也不合適, 100+200=300ohm。電阻的輸出負載較重,對信號沿有進一步拉緩的影響;3.100ohm 和 200ohm 的電阻構成了分壓網絡, 造成 FPGA 輸入端的高電平只有 74AHC04 輸出端的2/3,這樣,接收端得到的信號幅度就更小了。

解決方法:選擇沿更快的反相器;串行匹配使用 10~50ohm 的阻值,具體由仿真確定;去除并行匹配電阻。

這個案例主要的問題就在于器件的選型。 100MHz 的時鐘,已屬于典型的高速信號,用不符合信號沿規格的低速器件驅動,必然會造成信號幅度上的違規。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603037 -

信號完整性

+關注

關注

68文章

1405瀏覽量

95459

原文標題:由驅動能力引起的信號完整性案例解讀

文章出處:【微信號:gh_eb821dd72e77,微信公眾號:PCB和原理圖設計與共享】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

信號完整性與電源完整性的相關資料分享

詳解信號完整性與電源完整性

信號完整性與電源完整性的詳細分析

聽懂什么是信號完整性

信號完整性“案例:錯誤的設計帶來的驅動能力問題”

信號完整性“案例:錯誤的設計帶來的驅動能力問題”

評論