隨著半導體行業的技術進步,尤其是摩爾定律的放緩,芯片設計和制造商們逐漸轉向了更為靈活的解決方案,其中“Chiplet”和“先進封裝”成為了熱門的概念。它們不僅為解決傳統單片集成芯片(SoC)面臨的尺寸、成本和性能瓶頸提供了創新思路,也帶來了全新的設計和制造挑戰。特別是在這一過程中,EDA工具的角色變得尤為關鍵,但也面臨著許多技術上的難題。該文從介紹Chiplet與先進封裝入手,分析兩者結合面臨的挑戰,并探索如何通過EDA工具去解決這些行業痛點。

Chiplet與先進封裝的關系

什么是 Chiplet?

Chiplet是一種將復雜芯片系統分解為多個較小、相對獨立的功能單元的設計方式。這些芯片模塊可以在一個集成封裝中以不同的方式組合,以構建出一個完整的系統。例如,一個高性能的計算平臺可能包含多個處理核心、存儲控制器、通信接口等,這些功能模塊被拆分成不同的Chiplet。它們通過高速的互聯方式(如高速串行總線、片內光互聯等)連接在一起,以實現系統級的協同工作。

Chiplet 的變革

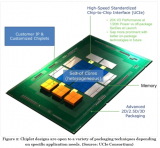

在傳統SoC設計中,開發者通常需要從不同的IP供應商獲取軟核(RTL代碼)、固核(門級網表)或硬核(GDSII版圖),再結合自研模塊,在特定工藝節點(如7nm、5nm)上完成芯片的集成、設計和制造。這種方案需要經歷完整的流片過程,開發周期長,且大尺寸單芯片的良率問題可能導致成本上升。Chiplet技術將傳統IP復用提升至硅片級:開發者無需自行設計或生產某些功能模塊,而是直接采購已流片驗證的Chiplet(如計算單元、I/O模塊等),通過先進封裝技術將這些硅片組合成完整系統。本質上,Chiplet是一種以裸片(Die)形式提供的“硬核IP”,其核心變革在于將系統集成從晶圓級轉移到封裝級。

Chiplet 的核心優勢

1.模塊化設計,靈活擴展

Chiplet將單芯片拆解為多個功能獨立的裸片(Die),支持像“樂高積木”一樣按需組合。例如,通過混合搭配計算、存儲和通信Chiplet,可快速定制適應AI、HPC等不同場景的解決方案。AMD的EPYC處理器正是通過不同數量的CCD(核心復合裸片)和IOD(I/O裸片)組合實現產品系列化。

2.良率提升與成本優化

小尺寸Chiplet(如3mm×3mm)相比大尺寸SoC(如20mm×20mm)顯著降低了晶圓缺陷的影響。根據行業數據,在相同缺陷密度下,Chiplet方案的良率可比傳統SoC提高30%以上,從而減少廢片損耗。

3.異構集成,性能突破

Chiplet打破工藝和材質的限制,允許將不同制程(如5nm邏輯芯片+28nm模擬芯片)、不同基底(硅、碳化硅)的裸片集成。例如,英特爾Ponte Vecchio GPU整合47個Chiplet,結合臺積電5nm與Intel 7工藝,實現算力密度翻倍。

4.降低研發門檻

通過復用已驗證的Chiplet(如HBM內存、SerDes接口),開發者可規避復雜模塊的設計風險,將資源集中于核心功能開發。

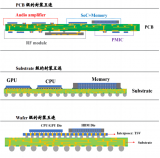

什么是先進封裝?

半導體封裝技術經歷了從傳統到先進的演進歷程。傳統封裝始于三極管直插時代,其典型流程包括:將晶圓切割成裸片(Die),將裸片貼裝在引線框架的小島上,通過引線鍵合(Wire Bond)實現電氣連接,最后進行塑封保護。這一時期的代表封裝形式包括DIP、SOP、TSOP、QFP等。隨著技術進步,先進封裝技術應運而生,突破了傳統封裝的局限。這類技術主要包括倒裝芯片(Flip Chip)、凸塊(Bumping)、晶圓級封裝(WLP)、2.5D封裝(中介層、RDL等)以及3D封裝(TSV)等。通過3D堆疊、系統級封裝(SiP)等創新方法,先進封裝實現了多芯片和功能模塊在單一封裝體內的高度集成。相較于傳統引線鍵合技術,先進封裝憑借高密度互連和異構集成等先進工藝,在系統集成度、尺寸微型化、能效比和性能表現等方面實現了質的飛躍。最初,先進封裝僅有WLP、2.5D和3D封裝等幾種形式,但近年來呈現爆發式發展態勢。各大廠商紛紛推出具有自主知識產權的技術方案,如臺積電的InFO和CoWoS、日月光的FoCoS、Amkor的SLIM和SWIFT等。先進封裝不僅是半導體制造工藝的重大突破,更從根本上重構了芯片設計范式。特別是在Chiplet技術興起后,先進封裝已成為延續摩爾定律的關鍵技術路徑之一,為半導體行業的持續發展提供了新的動力。

先進封裝的關鍵要素

1.晶圓(Wafer):先進封裝的基石

晶圓作為半導體制造的基礎載體,其質量直接影響最終芯片性能。現代先進封裝中,晶圓不僅承擔傳統電路加工功能,更成為異質集成和多芯片封裝的關鍵平臺。隨著制程進步,300mm大尺寸晶圓已成為主流,其對表面平整度和材料純度的要求也日益嚴苛,特別是在3nm以下制程中,晶圓缺陷控制精度需達到原子級水平。

2.凸點(Bump):芯片互連的核心樞紐

作為芯片與封裝基板間的關鍵連接橋梁,凸點技術經歷了從錫鉛合金到銅柱結構的演進。現代銅柱凸點具有以下優勢:1.導電性提升30%以上2.機械強度增加50%3.環保合規性更優,在倒裝芯片技術中,凸點間距已縮小至20μm以下,其排布密度直接影響封裝的信號完整性、散熱效率和機械可靠性。

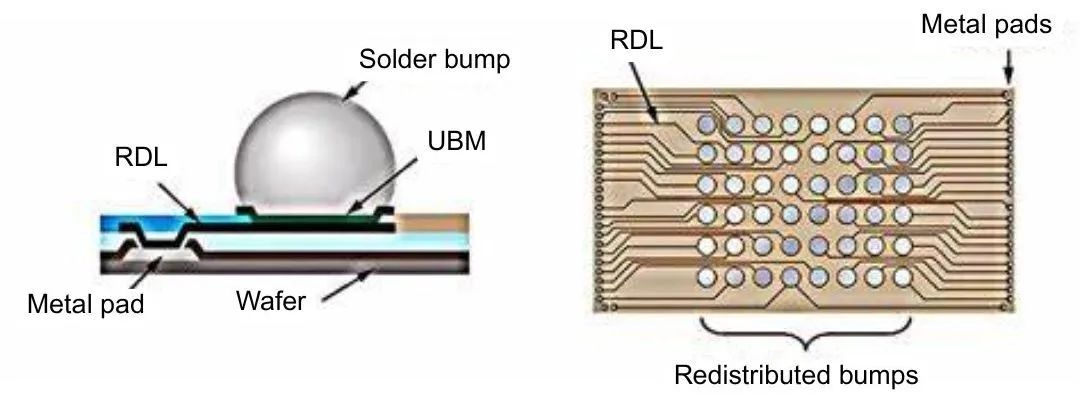

3.重布線層(RDL):信號優化的關鍵路徑

RDL技術通過多層金屬布線實現:I/O密度提升10倍以上,信號傳輸距離縮短40%,阻抗匹配精度提高60%,在扇出型封裝中,RDL層數已發展至5層以上,線寬/線距達到2μm/2μm水平,有效支撐了高密度異質集成需求。

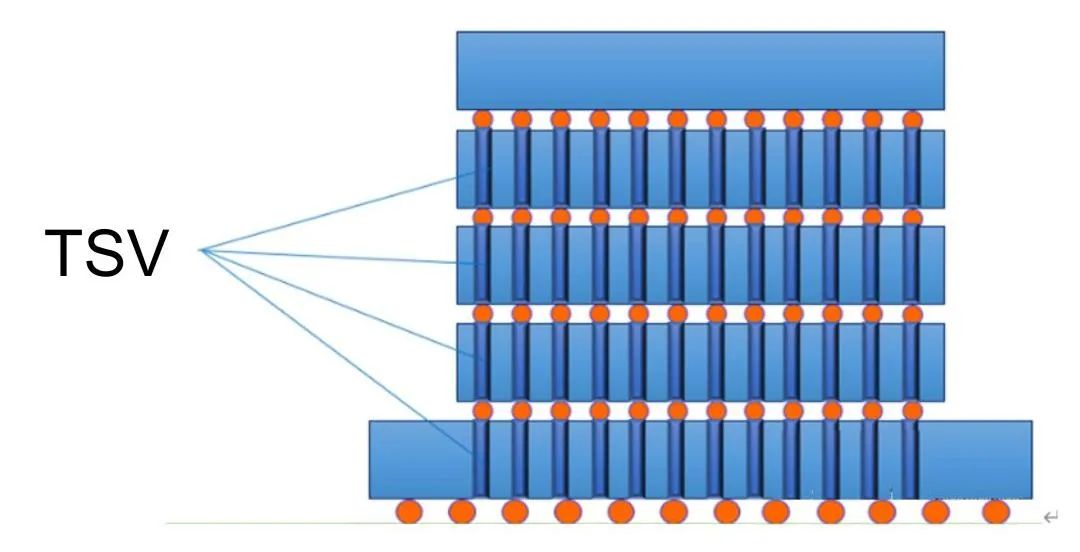

4.硅通孔(TSV):立體集成的技術突破

TSV技術的主要技術指標:深寬比突破10:1,導通電阻降低至毫歐級,信號延遲縮減至皮秒級,在3D IC應用中,TSV可實現超過10層的芯片堆疊,使互連密度達到傳統封裝的100倍,為高性能計算和AI芯片提供關鍵支撐。

這四大要素共同構成了先進封裝的技術矩陣:晶圓提供制造基礎,凸點實現可靠互連,RDL優化信號分布,TSV突破空間限制。

它們的協同創新推動著封裝技術從平面集成向立體系統級集成的跨越式發展,為后摩爾時代的芯片性能提升開辟了新路徑。當前最先進的封裝方案已能實現單封裝集成超過1000億晶體管,信號傳輸帶寬突破TB/s級,這些突破都依賴于這四大核心技術的持續演進。

-

半導體

+關注

關注

335文章

28901瀏覽量

237653 -

eda

+關注

關注

71文章

2924瀏覽量

177930 -

chiplet

+關注

關注

6文章

459瀏覽量

12994 -

先進封裝

+關注

關注

2文章

474瀏覽量

623

原文標題:Chiplet與先進封裝的技術協同及EDA仿真工具面臨的挑戰 (一)

文章出處:【微信號:巨霖,微信公眾號:巨霖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

半導體芯片先進封裝——CHIPLET

SiP與Chiplet成先進封裝技術發展熱點

先進封裝呼聲漸漲 Chiplet或成延續摩爾定律新法寶

光芯片走向Chiplet,顛覆先進封裝

先進封裝Chiplet全球格局分析

何謂先進封裝/Chiplet?先進封裝/Chiplet的意義

一文講透先進封裝Chiplet

什么是先進封裝/Chiple?先進封裝Chiplet優劣分析

先進封裝Chiplet的優缺點與應用場景

先進封裝技術是Chiplet的關鍵?

探討Chiplet封裝的優勢和挑戰

一文解析Chiplet中的先進封裝技術

Chiplet在先進封裝中的重要性

評論