1. 電路的延時

在實際電路中存在兩種延遲,慣性延遲 (Inertial delay) 和傳導延遲 (Transport delay)

慣性延遲

定義:若元件的輸入信號的脈沖寬度小于一定值時,元件的輸出沒有響應,也就是說元件具有一定的慣性。

產生原因:當脈沖到達時,由于脈沖寬度小于元件本身的延遲,當脈沖結束時,元件的新輸出還未建立起來。考慮了電路中存在的大量分布電容。

傳導延遲

定義:輸入信號變化到對應輸出信號變化經過的時間,類似于物理傳輸線的延遲。

產生原因:載流子運動的速度有限,通過導線需要一定的時間。

2. Verilog 中的時序模型

在分析 Verilog HDL 的仿真行為前,我們需要了解 Verilog 中時序模型。

時序模型分為:門級時序模型、過程時序模型。

門級時序模型

適用范圍:所有的連續賦值語句、過程連續賦值語句、門原語、用戶自定義原語。

特點:

任意時刻輸入發生變化,將重新計算輸出。

當之前的的事件未執行完畢時又發生的新的變化,則會撤銷之前的事件,開始新的事件。

過程時序模型

適用范圍:過程語句。

特點:

當敏感列表發生變化時觸發執行。

當之前的的事件未執行完畢時又發生的新的變化,則不撤銷原有事件,同時開始新的事件,如果同時有幾個更新事件,它們的執行順序是不確定的。

3. Verilog 中的仿真延遲語句

Verilog 中的仿真延時語句為 #n,n 表示延時時間,將該語句加在語句中,延遲 n 個時間單位。

延時的添加方法有兩種:正規延遲和內定延遲

正規延遲 (#在外面)

#5 C = A +B

在 T 時刻執行到該語句時,等待 5 個時間單位,然后計算等號右邊的值賦給 C,此時使用的 A B 的值是 T+5 時刻的值。

內定延遲 (#在里面)

C = #5 A +B

在 T 時刻執行到該語句時,先計算 A+B 的值,計算后等待 5 個時間單位將值賦給 C,使用的 A B 的值是 T 時刻的值。

4. 在 Verilog 建模中增加延時

兩種延時的添加方式和三種賦值方式 (連續賦值、阻塞賦值、非阻塞賦值) 一共形成六中添加延遲的方式。

// 1. 連續賦值+ 正規延遲assign#5C = A +B;// 2. 連續賦值+ 內定延遲assign C =#5A +B;// 3. 阻塞賦值 + 正規延遲always @(*) begin #5 C = A +B; end // 4. 阻塞賦值 + 內定延遲 always @(*)begin C =#5A +B;end// 5. 非阻塞賦值 + 正規延遲always @(*) begin #5 C <= A +B; end ?// 6. 非阻塞賦值 + 內定延遲 always @(*)?begin? ? ?C <=?#5?A +B;end

下面對這六種方式逐一分析:

連續賦值+ 正規延遲

在 T 時刻執行到該語句時,等待 5 個時間單位,然后計算等號右邊的值賦給 C1。

使用的 A B 的值是 T+5 時刻的值。

若在等待過程中 A B 的值發生變化再次觸發 assign block,根據 assign block 的門級時序模型特點,仿真器會撤銷先前的等待事件,然后重新執行語句。

當變化脈沖小于 5 個時間單位時,等待事件會被撤銷,該脈沖將不起作用。

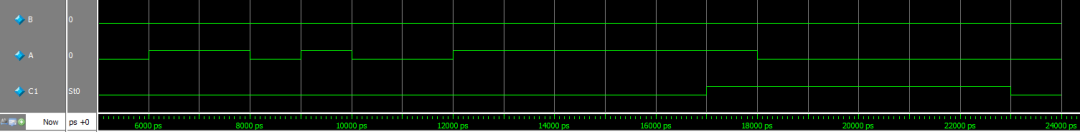

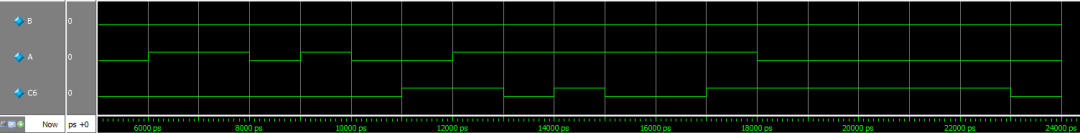

仿真結果:

可以看出在 6ns、8ns、9ns、10ns 時刻 A 發生了變化,但皆因持續時間小于 5ns,所以都沒有對 C1 產生影響,只有在 12ns 和 18ns 的變化持續時間超過 5ns,作用到 C1 上。

連續賦值+ 內定延遲

在 T 時刻執行到該語句時,計算等號右邊的值,等待 5 個時間單位后賦給 C2。

使用的 A B 的值是 T 時刻的值。

若在等待過程中 A B 的值發生變化再次觸發 assign block,根據 assign block 的門級時序模型特點,仿真器會撤銷先前的等待事件,然后重新執行語句。

當變化脈沖小于 5 個時間單位時,等待事件會被撤銷,該脈沖將不起作用。

該種方式有記憶屬性,與連續賦值原則不符,為非法語句,編譯不能通過。

阻塞賦值 + 正規延遲

在 T 時刻執行到該語句時,等待 5 個時間單位,然后計算等號右邊的值阻塞賦給 C3。

使用的 A B 的值是 T+5 時刻的值。

若在等待過程中 A B 的值發生變化再次觸發 always block,根據 always block 的過程時序模型特點,此時還在等待過程,always 語句還未執行結束,不會開始新一輪的事件,仿真器不會對敏感列表反應。

仿真器忽略延遲時間段的數據變化。

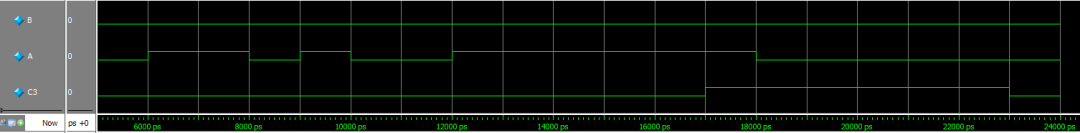

仿真結果:

在 6ns 時刻 A 的值發生變化,always block 開始執行,經過 5ns,用 11ns 時刻的 A B 的值計算出結果賦給 C3,而忽略了 8ns 和 10ns 時刻的變化。

阻塞賦值 + 內定延遲

在 T 時刻執行到該語句時,計算等號右邊的值,等待 5 個時間單位后賦給 C4。

使用的 A B 的值是 T 時刻的值。

若在等待過程中 A B 的值發生變化再次觸發 always block,根據 always block 的過程時序模型特點,由于賦值方式為阻塞賦值,此時 always 語句還未執行結束,不會開始新一輪的事件,仿真器不會對敏感列表反應。

仿真器忽略延遲時間段的數據變化。

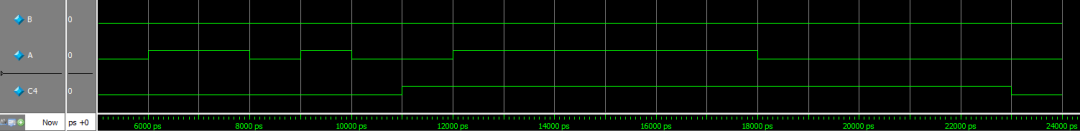

仿真結果:

在 6ns 時刻 A 的值發生變化,always block 開始執行,經過 5ns,用 6ns 時刻的 A B 的變化后的值計算出結果賦給 C4,而忽略了 8ns 和 10ns 時刻的變化。

非阻塞賦值 + 正規延遲

在 T 時刻執行到該語句時,等待 5 個時間單位,然后計算等號右邊的值非阻塞賦給 C5。

使用的 A B 的值是 T+5 時刻的值。

若在等待過程中 A B 的值發生變化再次觸發 always block,根據 always block 的過程時序模型特點,此時還在等待過程,always 語句還未執行結束,不會開始新一輪的事件,仿真器不會對敏感列表反應。

仿真器忽略延遲時間段的數據變化。

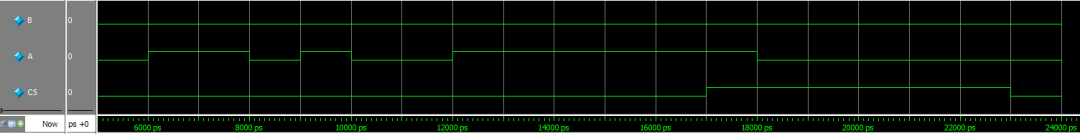

仿真結果:

在 6ns 時刻 A 的值發生變化,always block 開始執行,經過 5ns,用 11ns 時刻的 A B 的值計算出結果賦給 C5,而忽略了 8ns 和 10ns 時刻的變化。

非阻塞賦值 + 內定延遲

在 T 時刻執行到該語句時,計算等號右邊的值,等待 5 個時間單位后賦給 C6。

使用的 A B 的值是 T 時刻的值。

若在等待過程中 A B 的值發生變化再次觸發 always block,根據 always block 的過程時序模型特點,由于賦值方式為非阻塞賦值,將賦值事件放進事件隊列后,always 語句執行結束,等待下一次的觸發,觸發來到時開始新一輪的事件。

仿真器接受延遲時間段的數據變化,輸入的變化延遲會全部反應在輸出上。

仿真結果:

A B 的每一次變化都觸發 always block 的執行,每一次變化都延時 5ns 后反應在 C6 上。

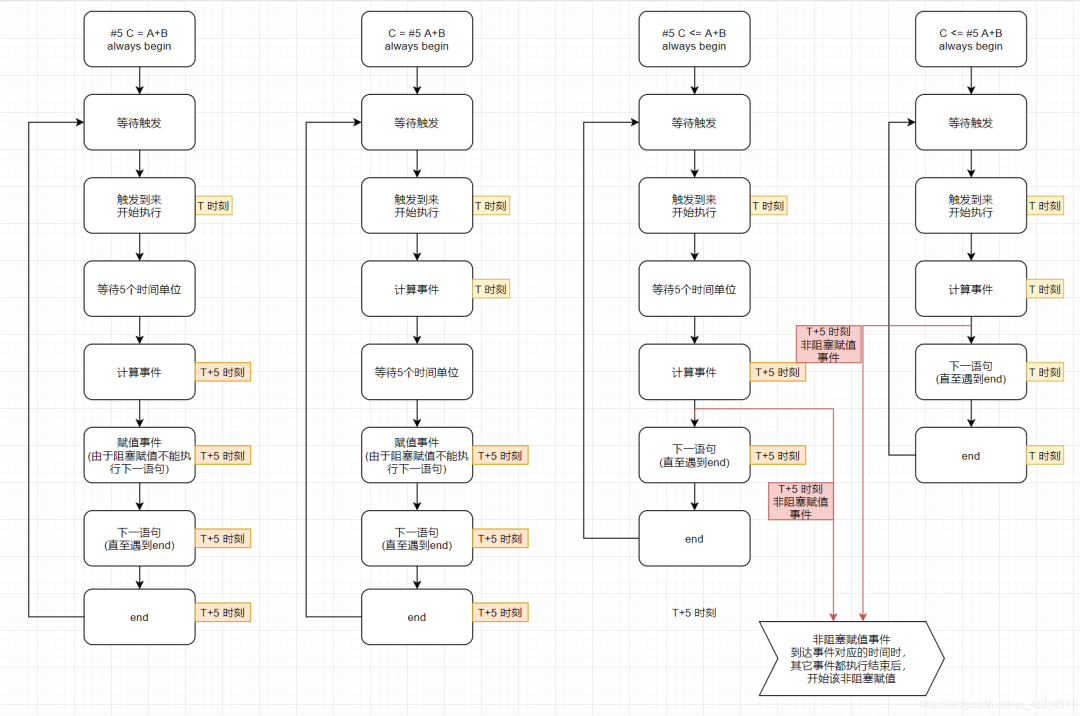

下圖為 always block 中的四種延時方式的仿真流程:

// 仿真源碼`timescale1ns/1ps moduleTestbench;reg A,B;wire C1,C2;reg C3,C4,C5,C6;initialbeginA =0;B =0;C3 =0;C4 =0;C5 =0;C6 =0;#6A =1;#2A =0;#1A =1;#1A =0;#2A =1;#6A =0;end// 1. 連續賦值+ 正規延遲assign#5C1 = A +B;// 3. 阻塞賦值 + 正規延遲always @(*) begin #5 C3 = A +B; end // 4. 阻塞賦值 + 內定延遲 always @(*)begin C4 =#5A +B;end// 5. 非阻塞賦值 + 正規延遲always @(*) begin #5 C5 <= A +B; end ?// 6. 非阻塞賦值 + 內定延遲 always @(*)?begin? ? ?C6 <=?#5?A +B;endendmodule

5. 總結

根據上述分析,容易看出慣性延時對應于連續賦值中的正規延遲,而傳導延時對應于非阻塞賦值中的內定延遲。

所以仿真中常用 “連續賦值 + 正規延遲“ 模擬慣性延遲,用 ”非阻塞賦值 + 內定延遲“ 模擬傳導延遲。

-

仿真

+關注

關注

51文章

4245瀏覽量

135358 -

Verilog

+關注

關注

29文章

1366瀏覽量

111899 -

時序

+關注

關注

5文章

397瀏覽量

37800 -

模型

+關注

關注

1文章

3499瀏覽量

50049 -

延時分析

+關注

關注

0文章

2瀏覽量

5642

原文標題:Verilog 仿真事件中的延時分析

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

北大Verilog課件四百多頁

verilog中乘法器延時問題

北大微電子verilog講義課件

單片機的C語言延時分析實例說明

Verilog設計增加延時的仿真技術

如何使用Icarus Verilog+GTKWave來進行verilog文件的編譯和仿真

FreeRTOS高級篇9---FreeRTOS系統延時分析

評論