概述

ADF4401A 是完全集成的系統(tǒng)級封裝 (SiP) 轉(zhuǎn)換環(huán)路(也稱為偏移環(huán)路)模塊,包括壓控振蕩器 (VCO) 和校準(zhǔn)鎖相環(huán) (PLL) 電路。專為高度抖動敏感的應(yīng)用而設(shè)計(jì),與設(shè)計(jì)在印刷電路板 (PCB) 上的傳統(tǒng)離散轉(zhuǎn)換環(huán)路解決方案相比,該解決方案減少了電路板空間和復(fù)雜性。通過利用這種高度集成的解決方案以及封裝電路和增強(qiáng)的隔離功能(可減少雜散元件),可以大大縮短產(chǎn)品上市時(shí)間。ADF4401A 為工程師提供了頻率合成解決方案,可設(shè)計(jì)出具有高度競爭性的系統(tǒng)。

ADF4401A 需要一個(gè)外部鑒相器或相位頻率檢波器 (PFD) 和一個(gè)外部本地振蕩器 (LO),以形成頻率合成解決方案。

ADF4401A 在反饋環(huán)路中集成了下變頻混頻級,將環(huán)路增益設(shè)置為 1,并較大程度降低了帶內(nèi)相位噪聲。通過將頻率下變頻級與 ADI 公司的低噪聲、集成寬帶 VCO 技術(shù)相結(jié)合,ADF4401A 可在 8 GHz 輸出時(shí),提供 9 fs rms 的寬帶抖動性能。輸出抖動性能在很大程度上取決于外部偏移 LO 的性能。

ADF4401A 模塊使用內(nèi)部 PFD 和 VCO 校準(zhǔn)電路,來選擇合適的 VCO 頻段。用戶可以禁用校準(zhǔn)電路,并使用外部 PFD 閉合環(huán)路。所有片內(nèi)寄存器均通過串行端口接口 (SPI) 進(jìn)行控制。

數(shù)據(jù)表:*附件:ADF4401A轉(zhuǎn)換環(huán)路、PLL、VCO模塊技術(shù)手冊.pdf

應(yīng)用

- 儀器儀表和測量

- 自動測試設(shè)備

- 航空航天和防務(wù)

特性 - RF 輸出頻率范圍:62.5 MHz 至 8000 MHz

- 8 GHz 輸出時(shí),RMS 抖動為 9 fs

- 6 GHz RF 輸出時(shí),輸出功率為 17 dBm IF

- 90 dBc LO_IN 至 RF 輸出

- 90 dBc 無雜散動態(tài)范圍

- 低相位噪聲、壓控振蕩器

- 可編程的 1、2、4、8、16、32 或 64 分頻輸出

- 3.3 V 模擬、數(shù)字和混頻器電源

- 5 V 放大器和 VCO 電源

- RF 輸出靜音功能

- 18.00 mm × 18.00 mm、80 端子 LGA_CAV

- 在[ADIsimPLL] 設(shè)計(jì)工具中提供支持

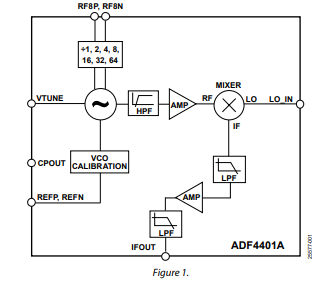

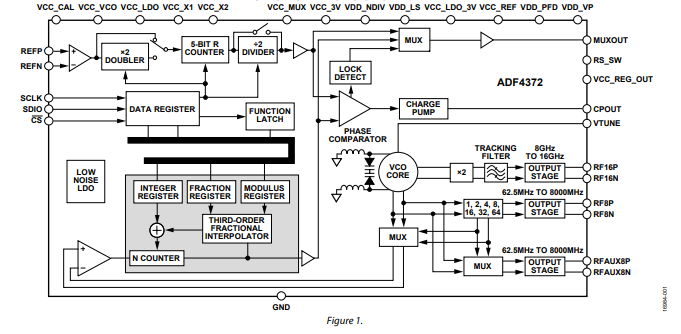

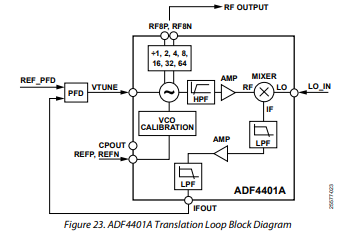

框圖

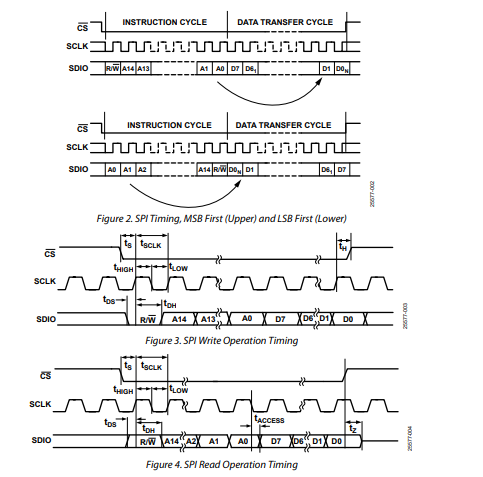

時(shí)序圖

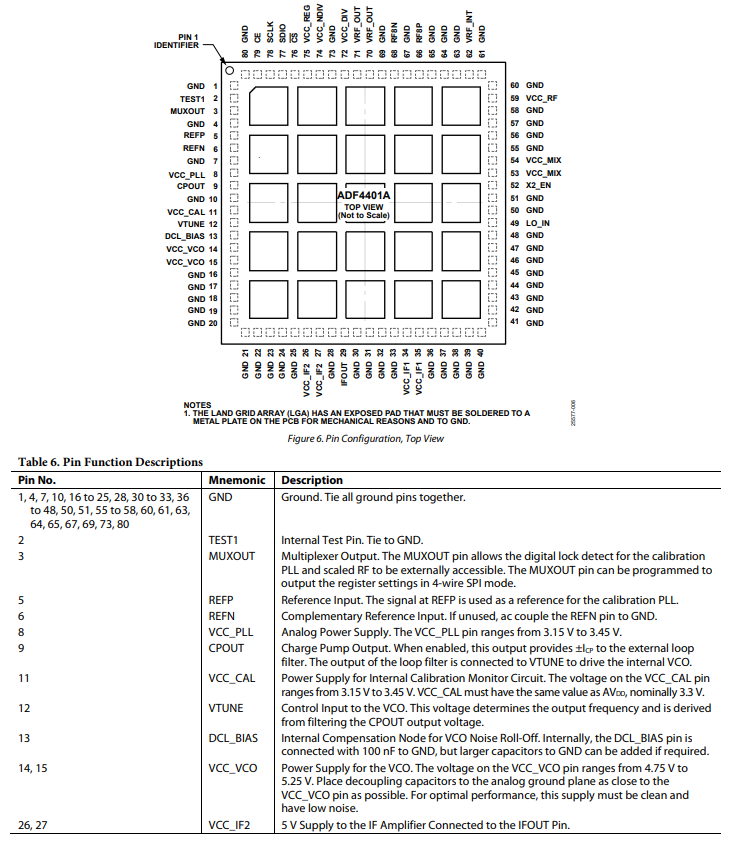

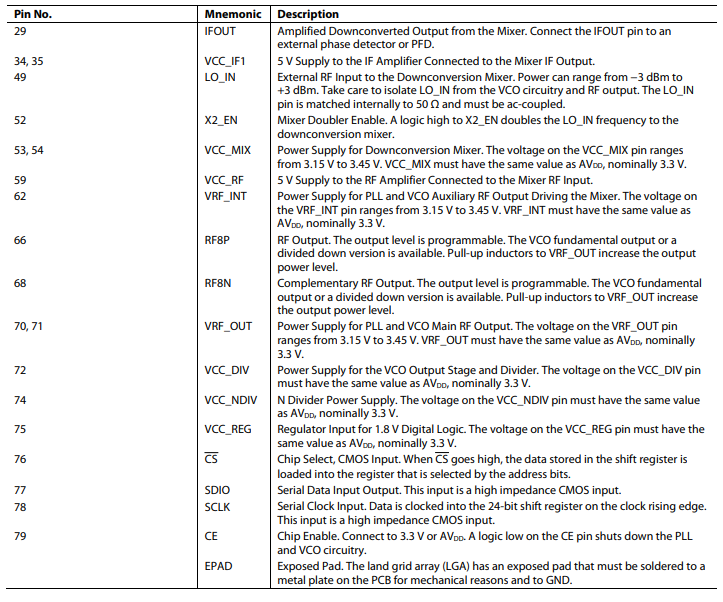

引腳配置描述

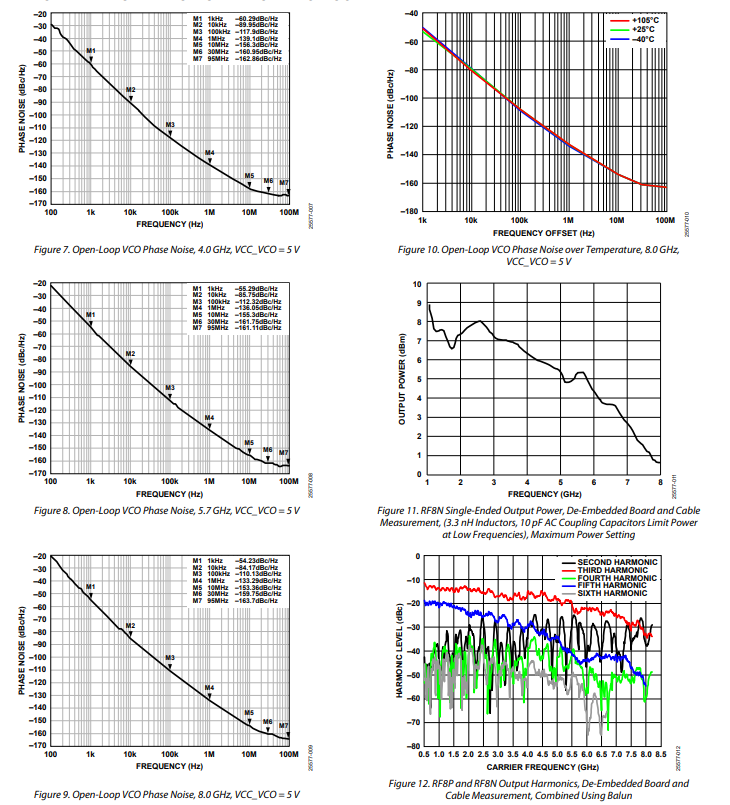

典型性能特征

圖23. ADF4401A 轉(zhuǎn)換環(huán)路框圖

ADF4401A是一款系統(tǒng)級封裝(SiP)轉(zhuǎn)換環(huán)路(偏移環(huán)路)模塊,內(nèi)含壓控振蕩器(VCO)及校準(zhǔn)鎖相環(huán)(PLL)電路、下變頻混頻器,以及R分頻器和N分頻器。該SiP將外部鑒頻鑒相器(REF_PFD)的較低頻率轉(zhuǎn)換為4GHz至8GHz的較高頻率范圍,具體由LO_IN引腳決定。

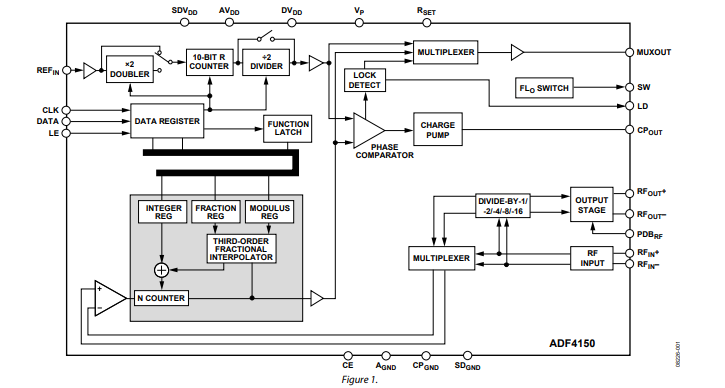

鎖相環(huán)(PLL)電路中的相位噪聲可描述為包含兩個(gè)部分:一個(gè)是平坦噪聲部分,即PLL的噪聲基底;另一個(gè)是1/f噪聲部分,即PLL的1/f噪聲。N分頻器值較低的PLL電路能讓用戶設(shè)計(jì)出相應(yīng)低相位噪聲性能的頻率合成器。更多信息請參見“射頻N分頻器”部分。

轉(zhuǎn)換環(huán)路合成器將所需的信道間隔與N分頻器值解耦,以優(yōu)化PLL的相位噪聲。如圖23所示,ADF4401A鎖定4GHz至8GHz射頻輸出頻率范圍中較高的頻率,該頻率為外部REF_PFD頻率的整數(shù)倍。集成混頻器和LO_IN引腳執(zhí)行該P(yáng)LL電路的分頻功能。集成射頻放大器提供所需的射頻隔離,中頻(IF)放大器提供所需的外部IFOUT電平。

由于本振(LO)在反饋環(huán)路中,外部鑒頻鑒相器(PFD)的公式如下(適用于高邊注入,即IF = LO - RF):

[ REF_PFD/R=(LO_IN - RF8x)/N ]

其中:

- R 是R分頻器。

- N 是N分頻器。

對于低邊注入(即IF = RF - LO):

[ REF_PFD/R=(RF8x - LO_IN)/N ]

在本電路中,R 和 N 均為1。因此,輸出頻率為:

[ RF8x = LO_IN pm REF_PFD ]

-

SiP

+關(guān)注

關(guān)注

5文章

523瀏覽量

106117 -

pll

+關(guān)注

關(guān)注

6文章

880瀏覽量

136023 -

VCO

+關(guān)注

關(guān)注

13文章

311瀏覽量

69965

發(fā)布評論請先 登錄

請問ADF9010使用內(nèi)部VCO,PLL無法鎖定

請問能否給我一個(gè)adf4159數(shù)據(jù)手冊上的環(huán)路濾波器仿真?

用于無線應(yīng)用的集成PLL和VCO

PLL的電源管理設(shè)計(jì)

用于ADF41020 PLL頻率合成器的評估板EV-ADF41020EB1Z

基于高壓VCO的高性能PLL設(shè)計(jì)

EV-ADF411xSD1Z用于評估ADF411x整數(shù)N和小數(shù)N分頻PLL頻率合成器

集成低噪聲VCO的ADF4350系列PLL之特性和應(yīng)用

UG-1922: Evaluating the ADF4401A Translation Loop, PLL, VCO Module

ADF4401A: Translation Loop, PLL, VCO Module Data Sheet

EVAL-ADF4401A EVAL-ADF4401A評估板

ADF4372帶集成VCO的微波寬帶頻率合成器技術(shù)手冊

ADF4155整數(shù)N/小數(shù)N分頻PLL頻率合成器技術(shù)手冊

ADF4150小數(shù)N/整數(shù)N分頻PLL頻率合成器技術(shù)手冊

評論