概述

AD6676是一款高度集成的中頻子系統,可數字化高達160 MHz的射頻(RF)頻段,并且此頻段在70 MHz至450 MHz中頻(IF)范圍內為寬度居中。 與傳統奈奎斯特IF采樣ADC不同,AD6676依靠具有高過采樣率的可調諧帶通Σ-Δ型ADC,無需特定頻段的IF SAW濾波器和增益級,極大簡化寬帶無線電接收機架構。 片內正交數字下變頻后接可選抽取濾波器,可將復數的數據速率降低至62.5 MSPS至266.7 MSPS范圍內便于管理的速率。 16位復數輸出數據通過單通道或雙通道JESD204B接口傳輸至主機,支持的線路速率高達5.333 Gbps。

數據表:*附件:AD6676寬帶中頻接收機子系統技術手冊.pdf

應用

特性

- 高瞬時動態范圍

- 噪聲系數(NF)低至13 dB

- 噪聲頻譜密度(NSD)低至?159 dBFS/Hz

- IIP3高達36.9 dBm,雜散音低于?99 dBFS

- 可調諧帶通Σ-Δ型模數轉換器(ADC)

- 片內數字信號處理

- NCO和正交數字下變頻器(QDDC)

- 可選抽取系數:12、16、24和32

- 支持自動增益控制(AGC)

- 單通道或多通道,支持JESD204B

- 低功耗:1.20 W

- 電源電壓:1.1 V和2.5 V

- TDD省電高達60%

- 4.3 mm × 5.0 mm WLCSP

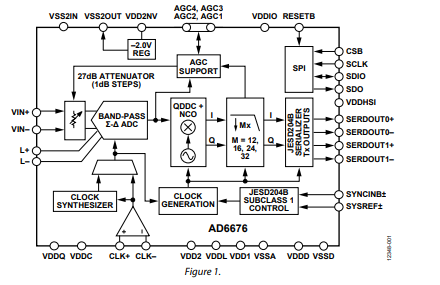

框圖

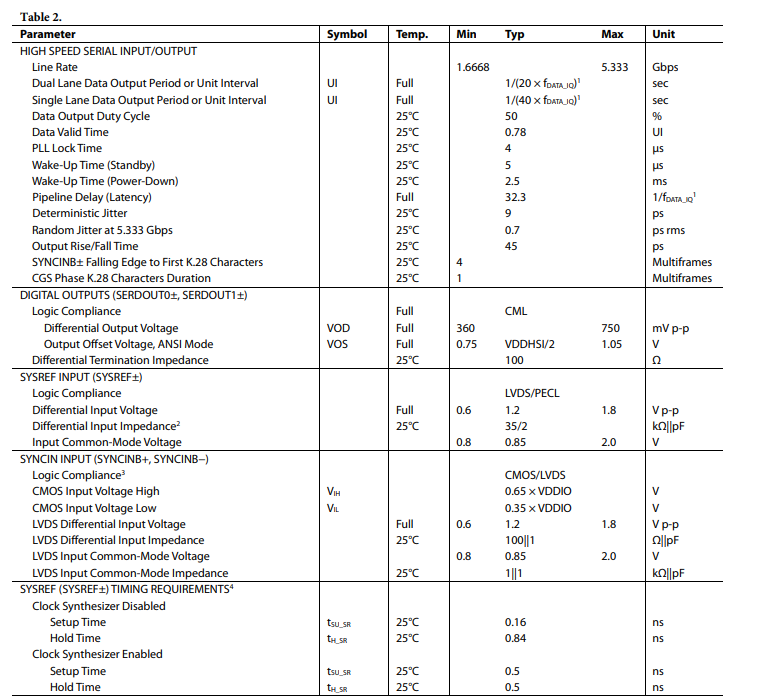

數字高速SERDES規格

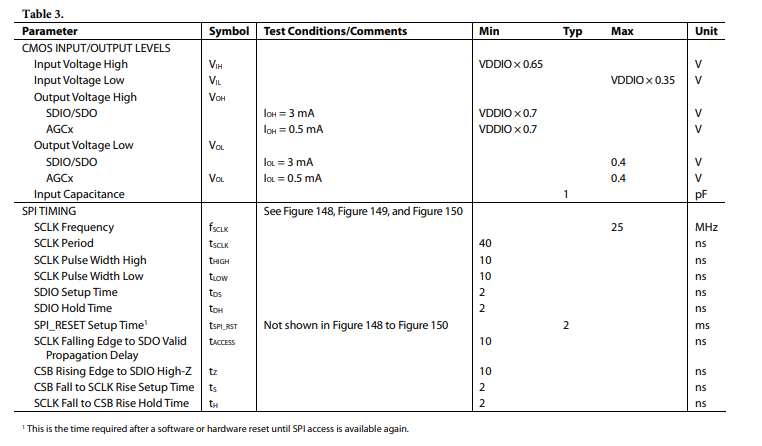

數字CMOS輸入/輸出規格

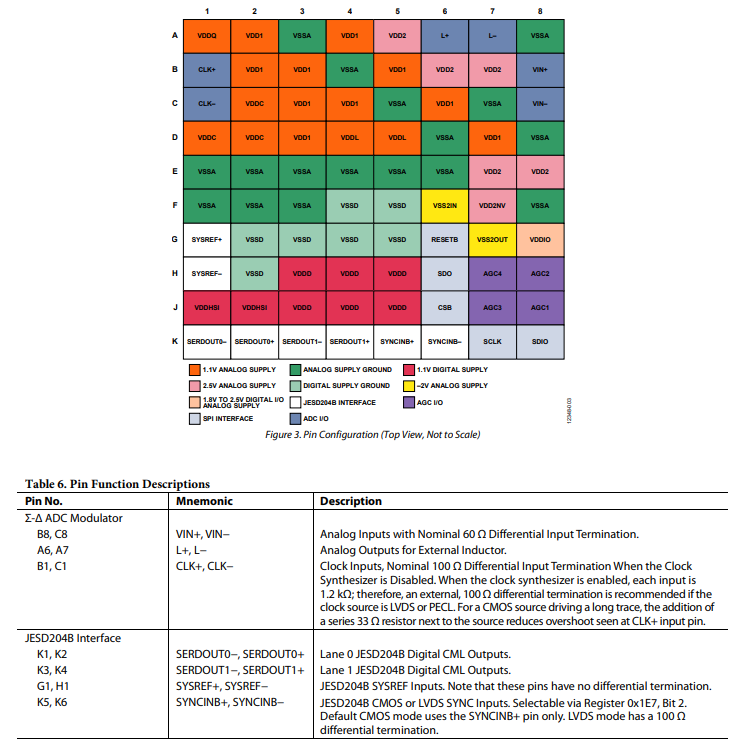

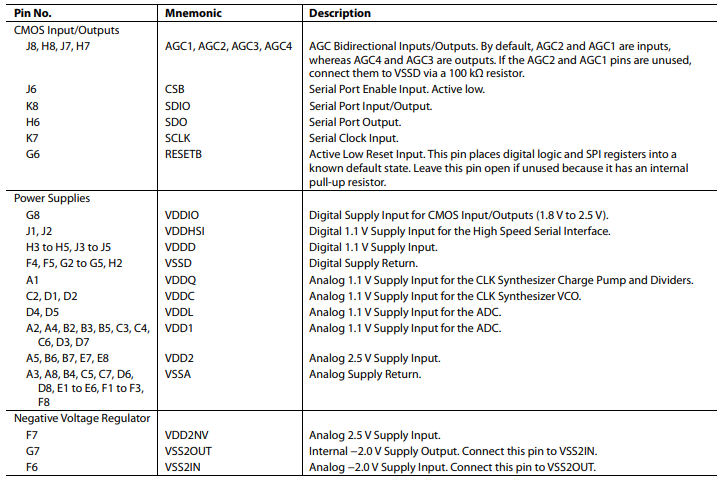

引腳配置描述

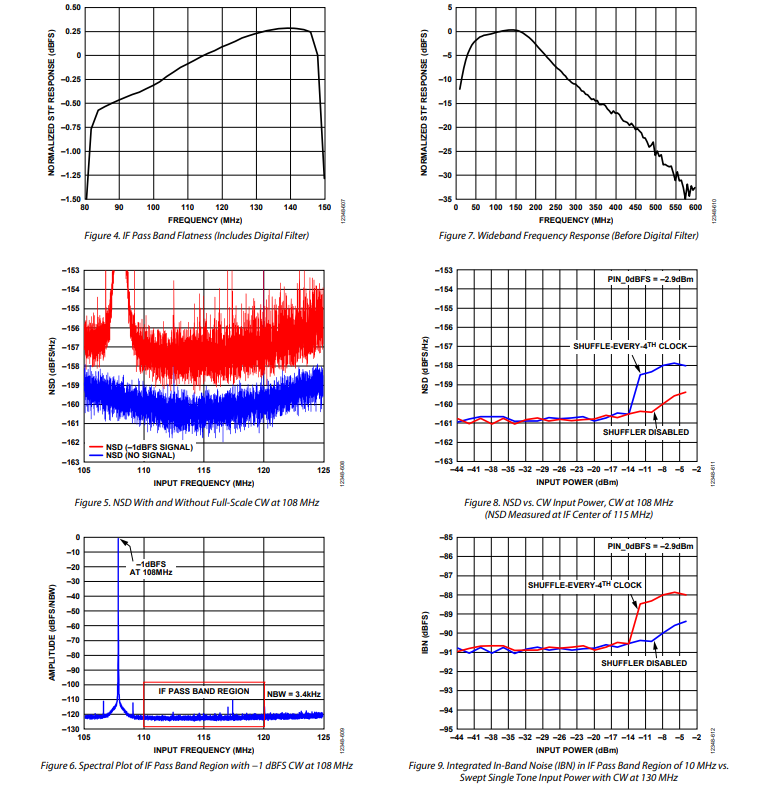

典型性能特征

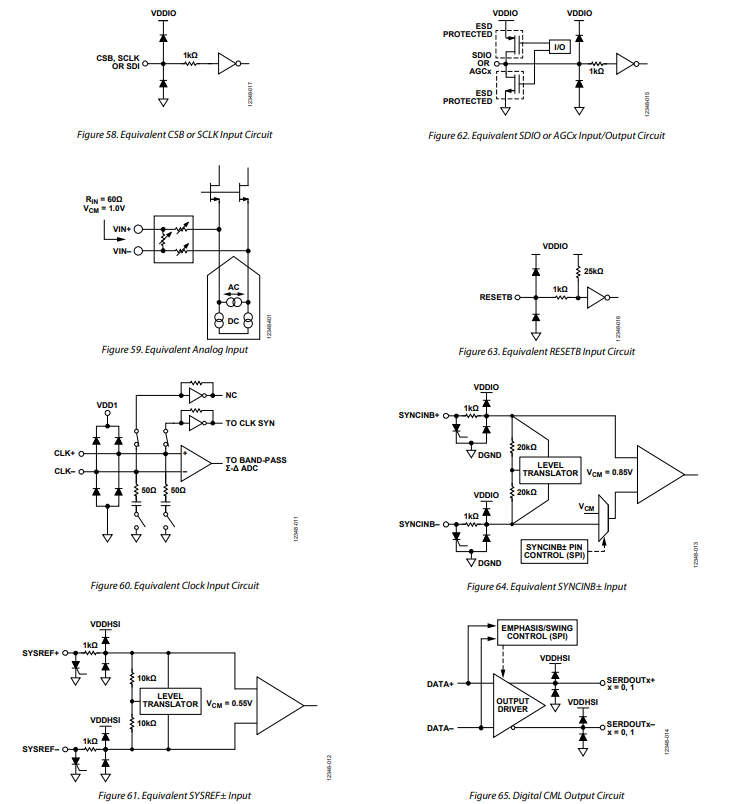

等效電路

概述

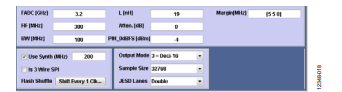

AD6676是一款高度集成且靈活的中頻(IF)子系統,能夠對中頻信號進行數字化處理。它具備調節中頻頻率和帶寬的能力,從而針對不同的應用場景優化Σ - Δ ADC的帶寬與動態范圍。為了便于評估和設計,還提供了一款軟件工具,即AD6676EBZ開發平臺,用于配置和評估該器件。此工具可存儲SPI初始化和配置序列,以供后續使用。圖形用戶界面(GUI)前面板的截圖(圖66)展示了不同的應用參數設置,這些設置可對AD6676進行配置。以下討論將深入介紹器件的操作原理,以及這些應用參數對性能的影響。

圖66. 有助于器件配置和評估的AD6676 GUI軟件工具截圖

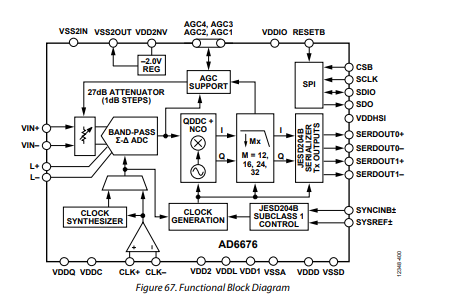

AD6676的功能框圖如圖67所示。其核心是連續時間帶通Σ - Δ ADC,工作時鐘頻率在2.0 GHz至3.2 GHz之間。片上控制器會根據用戶指定的應用參數來配置Σ - Δ ADC。Σ - Δ ADC可在期望的中頻范圍內提供出色的動態范圍和帶外抑制能力,同時將帶內平坦度控制在0.5 dB以內。片上時鐘合成器可提供2.94 GHz至3.2 GHz的Σ - Δ ADC時鐘。或者,也可提供外部時鐘,以實現更低的時鐘速率或更好的相位噪聲性能。

片上數字信號處理模塊包括一個正交數字下變頻器(QDDC),其后是可選的抽取濾波器,支持的抽取因子為12、16、24或32。QDDC能夠對復信號進行處理,使其以直流為中心,即零中頻。級聯抽取濾波器可去除ADC固有的帶外噪聲以及其他帶外信號成分,從而將16位復數IQ數據速率降低至更易于管理的水平,以便通過單通道或雙通道JESD204B接口傳輸至主機,該接口支持的速率高達5.333 Gbps。

AD6676還具備自動增益控制(AGC)支持和/或電平規劃功能。AGC支持功能包括能夠監測Σ - Δ ADC輸出的峰值功率,或監測第一個內部抽取級后的均方根功率。主機可通過配置各種標志位來啟動快速AGC操作,這些標志位的狀態可通過AGCA至AGCI引腳獲取。這些標志位可設置可編程閾值,以指示信號電平是高于還是低于設定水平。此外,還提供了一個步長為1 dB的27 dB衰減器,用于在初始系統校準期間進行電平規劃。或者,標稱0 dBFS滿量程輸入功率引腳(PIN_0dBFS)的 - 2 dBm輸入功率可衰減12 dB,從而進一步降低射頻/中頻增益要求。SPI可對AD6676的眾多參數進行編程,使其能夠針對各種應用進行優化。

-

射頻

+關注

關注

106文章

5734瀏覽量

169866 -

接收機

+關注

關注

8文章

1219瀏覽量

54265 -

子系統

+關注

關注

0文章

115瀏覽量

12702

發布評論請先 登錄

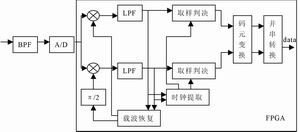

零中頻接收機設計

評論