我知道,我對與電子有關的所有事情都很著迷,但不論從哪個角度看,今天的現場可編程門陣列(FPGA),都顯得“鶴立雞群”,真是非常棒的器件。如果在這個智能時代,在這個領域,想擁有一技之長的你還沒有關注FPGA,那么世界將拋棄你,時代將拋棄你。本公眾號作者ALIFPGA,多年FPGA開發經驗,所有文章皆為多年學習和工作經驗之總結。

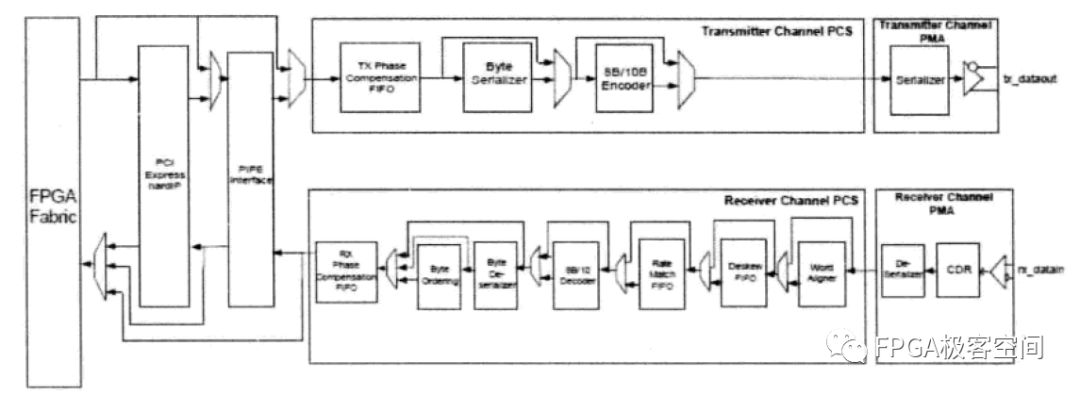

Stratix IV GX內嵌SERDES結構如圖所示

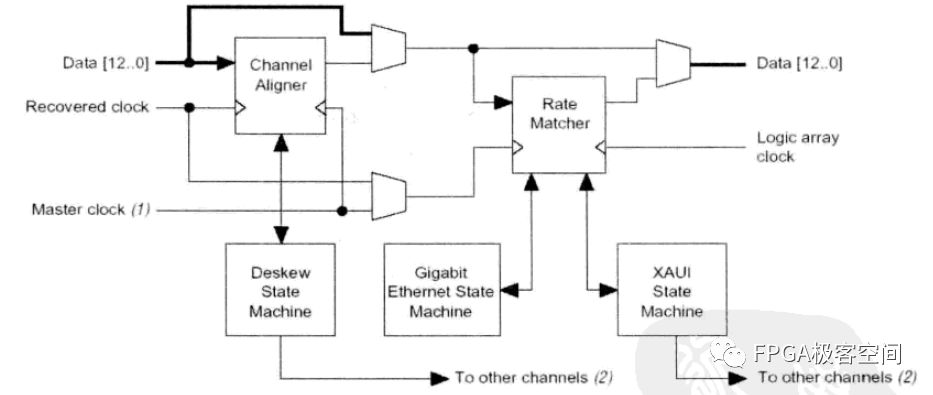

通道對齊(Channel Aligner)和速率匹配(Rate Matcher)。

Channel Aligner和Rate Matcher根據各種接口標準的物理編碼子層(PCS,Phsical Coding Sub-layer)規定,將數據的所有通道對齊,并適配數據速率,同步編碼狀態機。常用的接口標準有GE、10GE和XAUI等,這部分電路結構示意圖所示。

8B/10B解碼。

8B/10B解碼器在這里完成8B/10B解碼的功能,將10bit數據轉換為8bit源數據。

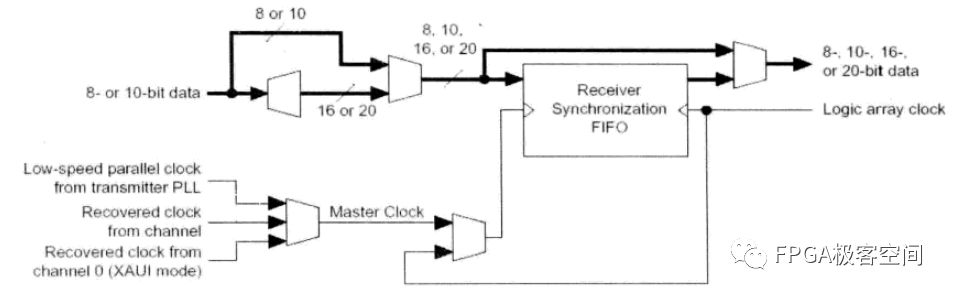

收端到邏輯資源的接口。

SERDES恢復出的數據進入FPGA有一個解復用和時鐘域轉換的問題,Stratix GX包含了專用電路可以完成8/10bit數據到8/10/20bit數據的Mux/Demux,另外SERDES收端到FPGA內部通用邏輯資源之間還有FIFO可以完成數據接口同步,其電路結構如圖所示。

發送方向的結構相對簡單多,只要按照收端數據流向反向追溯,就非常容易理解發端主要模塊的功能與結構,發端主要包含以下功能模塊。

(1)FPGA邏輯資料SERDES發端的接口電路。

從FPGA邏輯資源到發端內嵌8字節深的FIFO用以完成數據接口的同步,另外還有Mux/Demux電路,其結構與收端到FPGA邏輯資源接口電路相似。

(2)8B/10B編碼。

將8bit源數據編碼為10bit數據,減少連”0”或連”1”串。

(3)發端PLL。

發端PLL參數如圖所示。

(4)并串轉換電路(Serializer)。

其并串轉換的順序是低位(LSB)先出。

(5)輸出緩沖。

其支持的I/O標準和可編程匹配阻抗特性與收端緩沖性能相似。值得一提的是,其Vod電壓動態可編程范圍為400Mv~1600mV,而且新器件的預加重范圍提升為0%~140%(Vod為800mV條件下)。

值得強調的是,Altera Stratix GX的SERDES模塊的可測試性非常好,提供豐富的環回模式,便于用戶上板調試。Stratix GX的SERDES支持以下測試模式。

信道環回(Channel loopback):包括串行環回(Serial loopback)、反向鏈路串行環回(Reverse serial loopback )、并信環回(Parallerl loopback)和方向鏈路并行環回((Reverse parallel loopback)4種模式。

BIST(Built-In Self Test,內嵌式自測)產生與校驗(BIST generator &verifier):包括BIST 8B并行環回、BIST并行環回和BIST串行環回3種模式。

PRBS產生與校驗(BIST generator& verifier):包括PRBS并行環回和PRBS串行環回兩種模

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603010 -

解碼器

+關注

關注

9文章

1143瀏覽量

40718

原文標題:Stratix IV GX內嵌的SERDES(二)

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

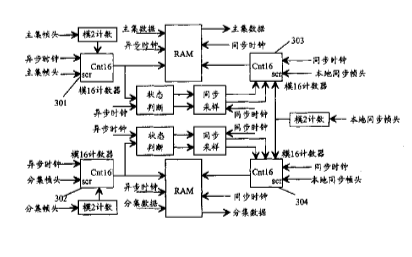

實時仿真系統信號復用/解復用算法

如何利用FPGA設計一個跨時鐘域的同步策略?

解決FPGA一個解復用和時鐘域轉換問題

解決FPGA一個解復用和時鐘域轉換問題

評論