PCI-X

PCI-X總線在PCI總線的基礎上發(fā)展而來,其在軟件和硬件層面上都是兼容PCI總線的,但是卻顯著的提高了總線的性能。也就是說PCI-X的設備可以直接插到PCI的插槽中去,PCI的設備也可以直接插到PCI-X的插槽中去。

從硬件層面上來說,PCI-X繼承了PCI總線中的Reflected-Wave Signaling,但是在信號的輸入端加入了輸入寄存器以增強時序性能,提高了總線的時鐘頻率。在PCI-X2.0的Spec中還提出了DDR和QDR技術,進一步提高了PCI-X總線的帶寬。

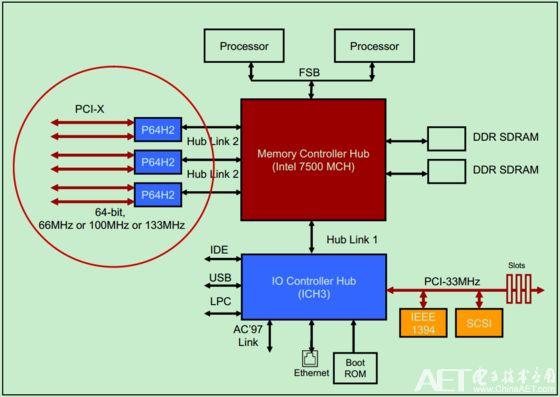

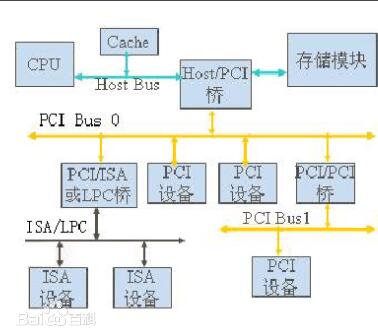

一個典型的PCI-X總線系統(tǒng)的例子如下圖所示:

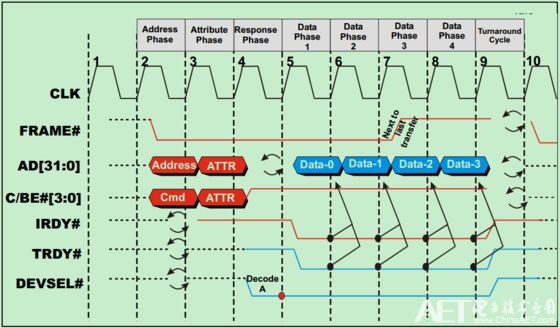

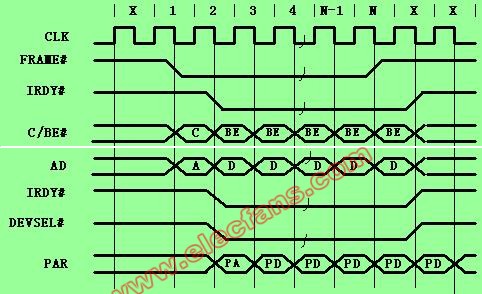

下面是一個PCI-X 突發(fā)讀存儲操作(Burst Memory Read Bus Cycle)的例子:

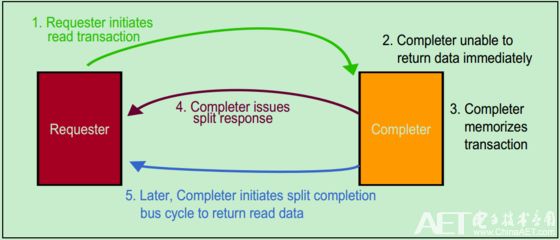

在PCI總線中,以總線主機從從機設備讀操作為例,當從機設備尚未準備好結束這次操作(從機設備未就緒,且數(shù)據(jù)尚未發(fā)送完)時,可以通過鎖存數(shù)據(jù)并插入等待周期,或者發(fā)起Retry操作。PCI-X總線采用了一種叫做Split Transaction的方式來處理這種情況,如下圖所示。此時,發(fā)起讀操作的總線主機被稱為Requester,而接受并向總線上發(fā)送數(shù)據(jù)的從機設備被稱為Completer。

注:PCIe Spec中繼承了PCI-X的這種命名方式。

采用這種方式的PCI-X總線的總線傳輸利用率(效率)可以達到85%,而標準的PCI總線只有50%-60%。關于Split Transaction的詳細內容,建議大家去參考PCI-X的Spec,這里不再詳細地介紹。此外,PCI-X總線還配置地址寄存器(Configuration Address Register)中加入了NS(No Snoop)和RO(Relaxed Ordering)兩位以提高總線傳輸效率。

前面的文章中介紹過,PCI總線的中斷操作是通過一系列的邊帶信號(Sideband Signals)來完成的,在PCI-X Spce中引入了消息信號中斷(MSI,Message Signaled Interrupts)的機制,以取代這些邊帶信號,進而精簡系統(tǒng)設計。

注:關于MSI的詳細內容,建議參考PCI-X Spec,此處不再詳細介紹。

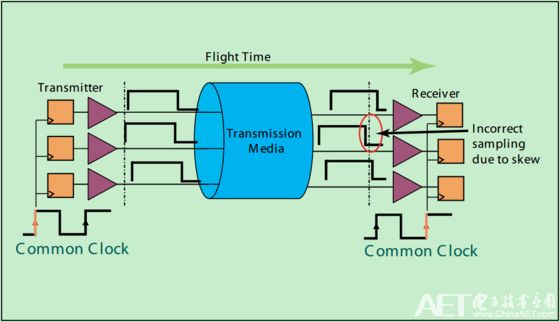

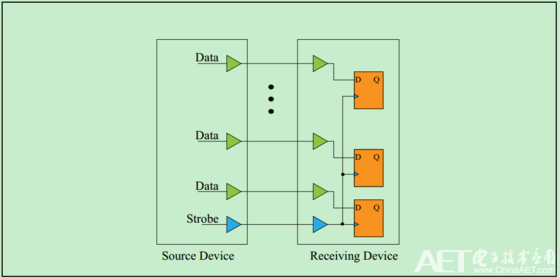

在介紹PCI-X2.0中提出的源同步模型之前,首先先來簡單地聊一聊非源同步模型的內在問題。所謂非源同步,就是說,信號的發(fā)送端和接收端的時鐘分別由一個或者兩個時鐘源驅動,發(fā)送端和接受端的時鐘同頻率,但是卻很難保證其同相位(即存在時鐘的相位偏差,skew)。

如上圖所示,由于信號線眾多,在PCB設計的時候,很難保證每一條信號線的長度都完全相同(更不要說還有過孔等因素)。因此,即使信號在發(fā)送時完全沿對沿的(實際上也是不可能的,對于PCI總線來說),也很難保證信號在同一時間到達接收端,此時的信號必然不再是沿對沿的了。如果不同信號線之間的傳輸延時差異較大,就很容易導致信號在接收端的采樣錯誤,進而提高數(shù)據(jù)傳輸?shù)恼`碼率。

為了解決這些問題,在PCI-X2.0的Spec中提出了源同步模型(實際上,在目前高速的FPGA邏輯設計和數(shù)字ASIC設計中采用的基本上都是源同步的模型)。如下圖所示,此時系統(tǒng)的時鐘由發(fā)送端(即Source Device)直接提供,并和數(shù)據(jù)信號一同傳輸至接收端,這就很好地解決非源同步模型中的時鐘相位差(Skew)的問題。此外,PCI-X2.0還在接收端輸入寄存器的基礎上支持了DDR輸入,甚至是QDR輸入,極大地提高了總線的帶寬。64-bit的133MHz PCI-X2.0 QDR總線的帶寬甚至達到了驚人的4262MB/s!基本上算是并行總線的巔峰了(DDR SDRAM不算是總線)。

然而,有意思的是,PCI-X2.0似乎生不逢時,雖然它顯著地提高了PCI總線的帶寬,但依舊無法掩蓋并行總線在高速總線數(shù)據(jù)傳輸中劣勢。PCI-X2.0總線雖然性能優(yōu)異,但是卻幾乎很少得到應用,由于其高功耗高成本,且并行總線的引腳過多,需要極其復雜的PCB設計,導致PCI-X2.0只在極少數(shù)高端的市場中得到了應用(如服務器市場等)。導致PCI-X2.0未能達到大規(guī)模應用的另一個因素就是PCI Express(PCIe)總線時代的到來,其標志著高速串行總線取代傳統(tǒng)的并行總線的時代的開端。

-

PCI

+關注

關注

4文章

663瀏覽量

130251 -

總線

+關注

關注

10文章

2878瀏覽量

88052

原文標題:【博文連載】PCIe掃盲——PCI-X總線基本概念

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

PCI PCI-X PCI-E介紹 精選資料分享

PCI-X Initiator/Target Core pd

基于FPGA的PCI總線接口設計

PCI總線仲裁器的設計及實現(xiàn)

PCI總線原理

基于FPGA的PCI總線接口設計

PCI-X總線FPGA開發(fā)板資料說明

從PCI、PCI-X到PCI-Express之間的連接

基于PCI總線的信號定義

LSISAS3080X-R PCI-X到3.0 Gbit/s SAS主機總線適配器安裝

關于PCI總線和PCI-X總線的簡要介紹

關于PCI總線和PCI-X總線的簡要介紹

評論