近日,IC 圈里出了一件大事,聯發科技宣布推出業內第一個通過 7nm FinFET 硅驗證的 56G PAM4 SerDes IP,擴大 ASIC 產品陣線。據了解,該 IP 方案具有一流的性能、功耗及晶粒尺寸(Die-area),已通過 7nm 和 16nm 原型芯片實體驗證,可以很容易地整合進各種前端產品設計中。

聯發科技在 ASIC 方面志向遠大,涉足多種應用領域:企業級與超大規模數據中心、超高性能網絡交換機、路由器、4G/5G 基礎設施(回程線路Backhaul)、人工智能及深度學習應用、需要超高頻寬和長距互聯的新型計算應用。

一貫擅長 SoC 設計的聯發科技,為什么要做 ASIC ? 這款 SerDes 方案有何優勢?如何滿足新一代以太網的高速傳輸需求?除 IP 外,聯發科技提供怎樣的 ASIC 服務?

小編為你帶來最勁爆的分析~

Why ASIC?

ASIC 是 Application-Specific Integrated Circuit 的縮寫,即“專用集成電路”,是指應特定用戶要求,在一個芯片上實現特定部分或全部功能的集成電路。在服裝界有定制的概念,根據個人的喜好和要求,為某個人單獨設計一套衣服,滿足人們的個性化需求。如果套用這個概念,ASIC 可以說是定制芯片,根據客戶的需求,量身打造專用芯片,是企業實現產品差異化的好工具。

近年來,我們注意到,物聯網、通信及一些消費領域的企業,尤其需要獨特的 ASIC 解決方案。聯發科技提供通過 7nm和 16nm 制程硅驗證的 IP,可無縫整合進入先進的 ASIC 產品,更好地滿足市場所需。

廣泛的 SerDes 產品組合

SerDes 是英文 Serializer (串行器)和 Deserializer (解串器)的簡稱,取兩個單詞的前三個字母組合而成。

在介紹 SerDes 之前,我們有必要了解下串行和并行的區別。我們可以把串行比喻成一個車道,并行比喻成 8 個車道。并行雖然一次傳輸的字節數量多,但是由于 8 條通道之間的互相干擾,傳輸速度不免受到限制,而且當傳輸出錯時,要同時重新傳 8 位數據。而串行一次只傳輸一個字節,抗干擾能力更強,傳輸出錯后重發一位就可以了,所以在長距離傳輸時,速度要比并行快。

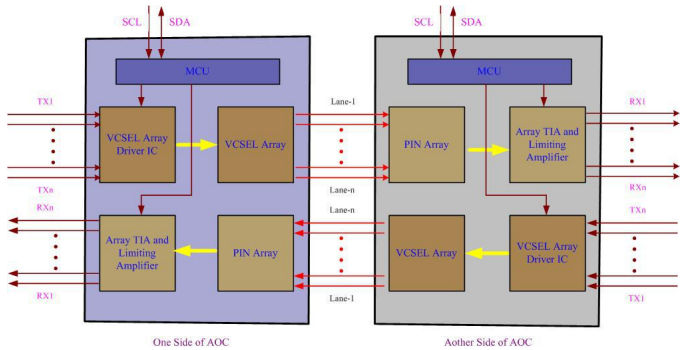

SerDes 在發送端將多路低速并行信號轉換成高速串行信號,經過傳輸介質,最后在接收端,高速串行信號重新轉換成低速并行信號,非常適合端到端的長距離高速傳輸需求。除了高速率外,聯發科技 SerDes IP 的厲害之處還在于,可以保障信號在串/并行轉換和傳輸過程中不失真。聯發科技具有業界最廣泛的 SerDes 產品組合,能為 ASIC 設計提供從 10G、28G、56G 到 112G 的多種解決方案。

用 PAM4 迎合新一代以太網

當大數據、云計算和物聯網走向規模應用,萬物的智能互聯引發數據生態的巨變,從骨干網,核心網到交換中心的數據流量均大幅增加,因此必須提高網絡帶寬,以應對激增的數據壓力。

PAM4(4 級脈沖幅度調制)被公認為是實現新一代線路速率的最高可擴展性多級信號協議,它能夠將現有基礎架構的帶寬提升一倍,幫助推進新一代以太網部署。

聯發科技最新發布的 SerDes 解決方案基于數字信號處理(DSP)技術,采用高速傳輸信號 PAM4,可實現 56Gbps 的傳輸速率,滿足高性能網絡交換機、大規模數據中心等對數據傳輸的需求。

端到端完整的 ASIC 服務

不只提供 IP,聯發科技還提供完整的 ASIC 服務,致力幫助尋求專業設計及客制化芯片設計方案的客戶,在多個領域拓展商機,如:有線和無線通信、超高性能計算、低功耗物聯網、無線連接、個人多媒體、先進傳感器和射頻。

聯發科技的 ASIC 服務涵蓋從前端到后端的任何階段— 系統及平臺設計、系統單芯片(SoC)設計、系統整合及芯片物理布局(Physical layout)、生產支持和產品導入。

ASIC 市場正在迎來新的發展機遇。我們相信,每一次小的升級、大的發布,都是去到下一個里程碑過程中的重要步驟。采用聯發科技 56G SerDes IP 的首款產品已經在開發中,預計于 2018下半年上市,讓我們一起期待吧!

-

IC

+關注

關注

36文章

5975瀏覽量

175926 -

云計算

+關注

關注

39文章

7852瀏覽量

137663 -

物聯網

+關注

關注

2912文章

44868瀏覽量

375554 -

大數據

+關注

關注

64文章

8903瀏覽量

137610

原文標題:為您量身定制的專屬芯片了解一下~

文章出處:【微信號:mtk1997,微信公眾號:聯發科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AMD Versal自適應SoC GTM如何用XSIM仿真和觀察PAM4信號

所謂的7nm芯片上沒有一個圖形是7nm的

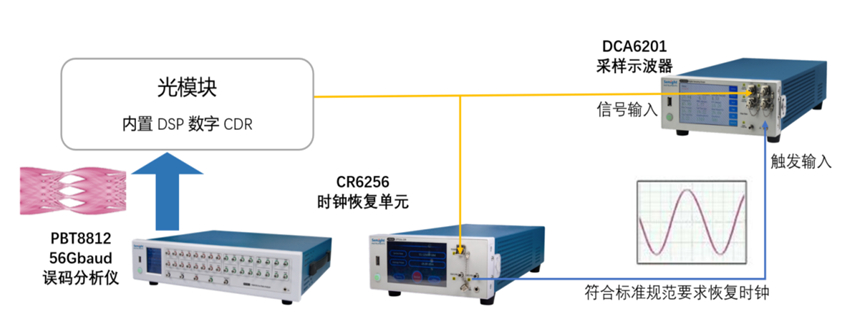

56Gbaud CR6256!400G/800G單多模光模塊及接口的時鐘提取

古希臘掌管224G 的神 | Samtec 224G PAM4 高速互連大合集!

DS560MB410低功耗56Gbps PAM4 4通道線性轉接驅動數據表

Samtec技術前沿 | 新型 Samtec前面板電纜系統帶來112 Gbps PAM4優異性能

廣和通攜手聯發科技推出基于FG370和Filogic 660 Wi-Fi 7芯片組的5G CPE解決方案

廣和通攜手聯發科技推出基于FG370和Filogic 660 Wi-Fi 7芯片組的5G CPE解決方案

SG3225EEN在PAM4光模塊和400G,QSFP-DD光模塊中的應用

2024年全球與中國7nm智能座艙芯片行業總體規模、主要企業國內外市場占有率及排名

Ethernovia推出全球首款采用7nm工藝的汽車PHY收發器系列樣品

AMD硅芯片設計中112G PAM4串擾優化分析

56G QSFP+ SR4光模塊最新解決方案

聯發科技推出 7nm 56G PAM4 SerDes IP,擴大 ASIC 產品陣線

聯發科技推出 7nm 56G PAM4 SerDes IP,擴大 ASIC 產品陣線

評論