EDA軟件中allegro的模塊復(fù)用非常實(shí)用,可能通常我們的PCB工程師還用的不多,但它在某些場(chǎng)合下還是很有用的,一個(gè)是它能減少我們重復(fù)性的工作,可以重用的原理圖和PCB我們就不需要重復(fù)設(shè)計(jì)了,也就是REUSE。

以下給大家講解詳細(xì)操作:

1、在orcad中畫(huà)好模塊的原理圖,設(shè)定好封裝,做好drc,做好元件編號(hào)。

2、檢查元件屬性是否設(shè)為current properties,其它設(shè)定可能出錯(cuò)。

3、在annotate-->allegro reuse中,選中g(shù)enerate reuse module,renumber design for using modules,選中unconditional,其它不選。

4、生成netlist.

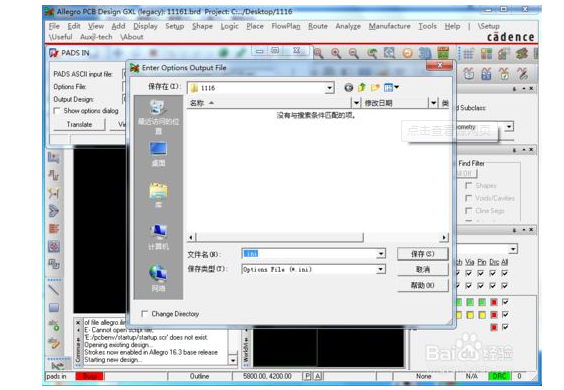

5、將netlist導(dǎo)入到allegro,布線,布局,若無(wú)rename等需要與orcad交互的動(dòng)作,選tools-->creat modules生成mdd文件.mdd文件的文件名一定要定義為:DSN NAME_ROOT SCHEMATIC NAME.mdd。DSN NAME為你定義的orcad中的dsn文件名,ROOT SCHEMATIC NAME是這個(gè)文件中的頁(yè)名字。這里若定義不對(duì),在reuse時(shí)找不到mdd文件。之后跳到第6步。

6、在orcad中back annotate,之后回到第2步。

7、模塊制作完成。

使用生成的模塊

1、在新的orcad設(shè)計(jì)中,選place-->herarhical block,reference中填入BLK?(注意,這里使用BLK是為了與原理圖中的U?R?C?區(qū)別,保證BLK這個(gè)名字專(zhuān)用于moduel,不然在做完allegro后,rename 時(shí),導(dǎo)回到orcad中出問(wèn)題。)在implementation type中選schematic view,在implementtation name中填入先前模塊的頁(yè)名稱(chēng),在path and file name中選擇相應(yīng)的dsn文件,之后在你的原理圖中出現(xiàn)一個(gè)block.

2、繼續(xù)其它設(shè)計(jì),之后在annotate-->packageing中,選中reset part name to "?",同時(shí)選中update occurrences,執(zhí)行一下,將所有的元件(包括module的name改為?),在annotate-->allegro reuse中,選中 renumber design for using modules,選中incremental,選中do not change the page number,選中select modules to mark for框里的內(nèi)容。其它不選。

3、drc后,出netlist.

4、導(dǎo)入到allegro后,palce-->manually place,選mudule instances,將module放入。注意一下mdd文件路徑的設(shè)定,不正確會(huì)找不到mdd 文件的。

5、在allegro中布好線后,可以rename到arcad中,與正常設(shè)計(jì)無(wú)區(qū)別。

6、over.

做reuse時(shí)的幾個(gè)注意事項(xiàng):

1:當(dāng)reuse模塊已經(jīng)放在電路中使用,重新修改reuse模塊的port口后,在使用的原理中右擊這個(gè)模塊,選synchronize up,則實(shí)現(xiàn)修改的同步。

2:在reuse模塊中,不能使用room屬性,不然可能與使用reuse的電路圖混淆。

3: reuse模塊中不能使用全局變量,特別是電源和地,使用port口傳遞數(shù)據(jù)。

4: reuse模塊內(nèi)部修改后,只要port口沒(méi)有變,則在使用它的原理圖不用同步。

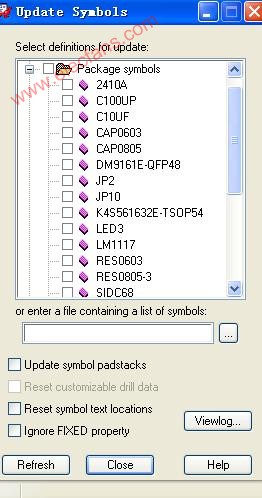

5: 做好的模塊文件用在pcb中后,若需要修改這部分文件,在修改完成后,在原pcb中使用update symbol功能,選相應(yīng)的moddle,之后更新就行了,注意生成mdd文件時(shí),原點(diǎn)的選擇,這然更新后一些線會(huì)錯(cuò)位。

6:當(dāng)導(dǎo)入到allegro的模塊出現(xiàn)dummy net的錯(cuò)誤時(shí),怎么辦?

出錯(cuò)的可能原因是由于模塊的orcad文件造成的,可能是對(duì)原始的orcad取一部分進(jìn)行修改,這些元件帶有原來(lái)文件的一些屬性。將相關(guān)orcad文件的所有元件和連線copy到一個(gè)新的頁(yè)內(nèi),將當(dāng)前頁(yè)的內(nèi)容刪除,從剛才copy到新頁(yè)的內(nèi)容copy回來(lái),這時(shí)看元件的屬性時(shí),沒(méi)有黃色的部分,按正常步驟重新生成mdd文件,在調(diào)用這個(gè)模塊的orcad文件中,重新編一次元件編號(hào),生成網(wǎng)表,問(wèn)題解決。

7:當(dāng)含有reuse的設(shè)計(jì)導(dǎo)入到allegro并布線完成,若重新修改原理圖,比如換一個(gè)10pin的IDC插座到16pin,不能用annotate-->allegro reuse命令,不然生成的網(wǎng)表會(huì)導(dǎo)入到allegro中會(huì)出錯(cuò),不知是什么原因?

答:在原理圖設(shè)計(jì)中,當(dāng)使用reset to ?后,使用annotate-->allegro reuse命令,將netlist導(dǎo)出到allegro后,不能再使用使用reset to ?,新增的元件使用increase功能,不要將所有的元件reset to ?,不然會(huì)出錯(cuò)。

-

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

394文章

4683瀏覽量

85548 -

eda

+關(guān)注

關(guān)注

71文章

2755瀏覽量

173201 -

PCB工程師

+關(guān)注

關(guān)注

1文章

22瀏覽量

7760 -

可制造性設(shè)計(jì)

+關(guān)注

關(guān)注

10文章

2065瀏覽量

15533 -

華秋DFM

+關(guān)注

關(guān)注

20文章

3494瀏覽量

4457

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

教你設(shè)置Allegro差分線

關(guān)于Allegro的轉(zhuǎn)換功能

也談PADS的reuse功能

PADS通過(guò)Add Reuse拼板出現(xiàn)錯(cuò)誤

PADS使用復(fù)用(Reuse)功能的一些體會(huì)

在allegro中實(shí)現(xiàn)銅皮挖字,填補(bǔ)allegro功能空白

Pads-Make_reuse模塊電路復(fù)用功能簡(jiǎn)析

Allegro軟件的菜單功能介紹

Allegro 16.2 新功能介紹

教你在allegro中更換元件封裝

allegro 軟件常用功能

教你使用allegro 的reuse功能

教你使用allegro 的reuse功能

評(píng)論