芯片面積估計的概念

芯片面積的主要涵蓋部分分為三部分

Standard cell : 實現芯片的功能邏輯

Macro block :第三方IP( PLLDAC POR Memory .etc )

芯片面積估計就是通過目標工藝的庫信息,設計的spec、以往設計的信息及,部分IP的綜合報告來統計這主要部分的總面積的過程。

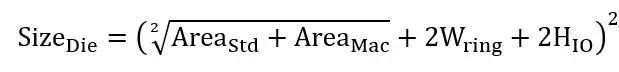

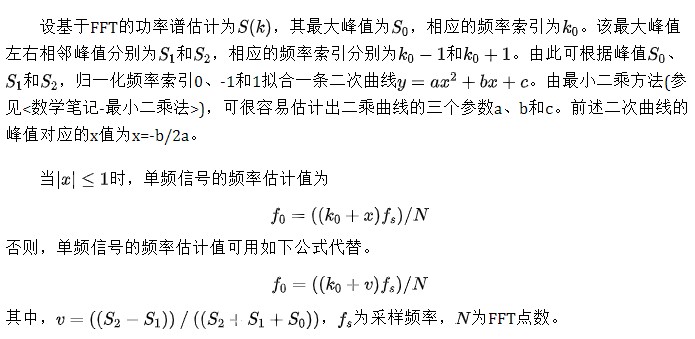

圖1,IO,Standard cell,Macro block

芯片面積估計的具體過程

獲得面積信息

獲得IO面積:通過目標工藝的IO庫文件得到各種IO的長寬及size大小,再根據我們的設計是spec,pin_list文檔中的pad選型和數量統計出。

獲得Standard cell面積:可以通過單獨IP的綜合過進行統計,轉產項目科根據原設計的全芯片綜合報個得到,對與沒有完整RTL的IP可以根據IP的復雜程度由設計方提供預估的等效邏輯門數,通過等效邏輯門※的數量計算面積。

※等效邏輯門:對數字設計的復雜程度一般用等效邏輯門的數量來評價,等效邏輯門一般為目標工藝下的一個標準大小(最小驅動能力)的與非門表示A(10k Gates)B(um2)=C(mm2),SMIC 110nm B=4.12。

獲得Macro block面積:第三方IP提供方提供的IP文檔中會有形狀及面積,Memorycompiler生成的memory文檔中也有memory的形狀及面積

幾種面積估計的方法

有了以上三種面積基本信息,就可以進行面積估算了。

首先要對獲得的Standard cell及Marco block的面積信息進行一下轉換,Standard cell的轉換(如果Standard cell的總面積是需要做SCAN但是未插入SCAN,需要乘以一個SCAN后的面積增量,經驗值為105%)主要是由于density◎,需將Standard cell的總面積除以density值,Macro block主要是由于blockage●,需將Macro block的長寬加上兩倍blockage的寬度再做乘積。

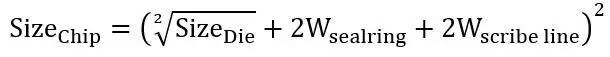

●density:由于芯片的Timing等原因,導致用于擺放Standard cell的區域不能全部被Standard cell(圖2中藍色部分)填滿,Standard cell的總面積占用于擺放Standard cell的區域的百分比就是density。

圖2 Standard cell,閑置區域(包含電源布線)

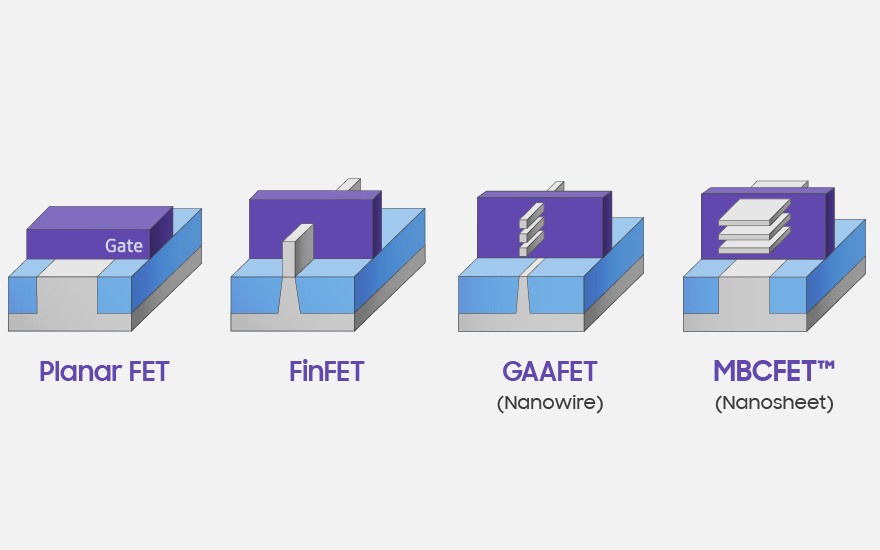

● blockage:第三方IP(多為模擬IP,圖3中央藍色的正方形)為了防止外圍環境的電氣干擾,在文檔中會要求保留一定的空區域或者用電源ring環繞,這部分區域就是blockage。

圖3

Pad Limit

這種情況是將芯片全部IO在四邊緊密的排滿,中間的面積大于轉換過的Standard cell與Macro block的總和,因為四邊排滿IO沒有辦法在縮小,所以芯片的主體面積就是有IO排列決定的這塊區域的面積,不需要估計由后端工程師排列好IO直接給出

2. Core Limit

這種情況是將芯片全部IO在四邊緊密的排滿,中間的面積小于CORE面積(轉換過的Standard cell與Macro block的總和),這時CORE的面積決定了芯片面積的大小。

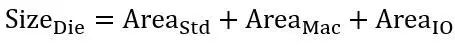

Core Limit的時候如果設計有在IO ring上不能擺放其他單元的要求,估算時將CORE當做正方形(因為正方形在芯片生產的時候在wafer上浪費的面積最小,也有利有芯片內部電源布線,減少IRdrop),將面積值開方的到正方形的邊長加上一個寬度為固定值或者邊長百分比的ring(power ring等)的寬度的兩倍,再加上IO高度的兩倍,再進行平方得到芯片的主體面積。

Core Limit的時候如果設計無要在IO ring上不能擺放其他單元的要求,估算是將CORE面積與IO面積相加即可。

芯片生產出來的時候是許多芯片在一片wafer上的需要用劃片機將芯片分割開來,這個時候就需要為分割芯片預留的空間scribe line,在分割芯片及芯片運輸封裝的過程中,芯片邊緣的應力會產生變化,設計上需要在芯片周邊做一圈鈍化的區域(sealring)以保護芯片不碎裂以及屏蔽和防潮功能。

這樣整個芯片的面積就是芯片主體邊長(主體面積開方)加上兩倍的scribe line的寬度和兩倍的sealring寬度再平方。

-

芯片

+關注

關注

456文章

51154瀏覽量

426292

原文標題:芯片面積估計方法簡介

文章出處:【微信號:eetop-1,微信公眾號:EETOP】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

三星3nm工藝創新采用‘GAAFET結構’ 芯片面積減少45%

異步電機速度估計方法之直接計算法

聲源定位中的時延估計方法研究

英飛凌以塑封料溫度測量為基礎的一種結溫計算方法

以塑封料溫度測量為基礎的一種結溫計算方法

新品# 極小的芯片面積,超強音質ANC codec ADAU1850主動降噪芯片

中芯發布0.11μm超高密度IP庫方案 可節省31%芯片面積

無線傳感網絡缺失值估計方法

葉面積儀操作方法和效果分析

活體葉面積儀的應用使得測量葉片面積更加方便

使用SRAM如何節省芯片面積

芯片面積估計的概念和方法

芯片面積估計的概念和方法

評論