隨著電子技術的發展,在系統設計中對信號頻率的穩定度和準確度要求越來越高,一般的LC,RC 振蕩器已不能夠滿足要求。晶體振蕩器的高精度與高穩定度剛好滿足了這一要求,但其頻率單一,且頻率值不高。于是出現了以這一穩定頻率為核心的,同時能產生大量具有相同精度和穩定度頻率的方法,這就是頻率合成“。 它用個高穩定度和高準確度的標準頻率源作為參考,通過對頻率進行加、減、乘、除運算,產生大量的同一穩定度和準確度的不同頻率。頻率合成器是電子設備的重要組成部分,是影響電子設備系統性能的關鍵因素之一。

一、國內外發展趨勢

頻率合成器在國外已經發展得相當成熟,形成了一系列的單片集成頻綜芯片,包括鎖相式整數/ 分數頻率合成器、直接數字頻率合成器、雙環或者多環鎖相式頻率合成器、DDS 與PL 混合式頻率合成器。

美國National Semiconductor 的LMX243X 鎖相式頻綜芯片的噪聲基底已經達到- 219 dBc /Hz,而ADI 公司的ADF4107 工作頻率可以達到7GHZ。目前,國內還沒有生產單片雙環或者多環鎖相式頻綜的能力。

目前DDS 的雜散一般可以做到- 70dB 左右。AD 公司生產的單片集成DDS芯片AD9858 采樣頻率達到1GHz,最大輸出為400MHZ。本世紀初出現的ROM-LESS 的DDS 方式,降低了電路功耗,是直接數字頻率合成中最前沿的技術。國內采用0.35Hm 常規互補金屬氧化物半導體電路( CMOS)C藝,研制出合成時鐘頻率達2GHZ 的新一代ROMLESS DDS 高速芯片。

國外混合式頻率合成器所達到的技術指標是: DDS + DAS 合成方式下,轉換速度可達IlHs,雜散分量- 65dBc,頻率范[ 圍10MHz~ 18GHz,步進間隔1F Iz,比較典型的代表是Wathing Johnson Company的WJ45 100 型頻率合成器。 而在DDS+ PLL 合成方式下,轉換速度可達100H,雜散分量-75dBc,相位噪聲- l15dBc /Hz@ 10 kHz,頻率范圍500MHz~ 2 5 GHz,分段合成,步進間隔1Hz,比較典型的弋表是Commun icat ion Techniques Inc.的FSFR 頻率合成器系列。

二、技術體制分析

頻率合成技術主要分為三類: 直接模擬式頻率合成技術( DAS)、直接數字式頻率合成技術(DDS) 和間接瑣相式頻率合成技術( PL)。

各種體制的合成器具有相應特點: 直接模擬式頻率合成器技術是以一個或多個高穩定參考信號為基準,通過倍頻、分頻、混頻及開關濾波放大等多種方法組合而成的一種頻率綜合器,具有頻率穩定度高、頻率轉換速度快、相位噪聲低等優點,但系統復雜、體積大、成本高、并且因混頻環節多容易引起較高的雜散電平,通常使用于頻率點較少、相位噪聲要求高的場合。

直接數字頻率合成技術是近年來剛剛發展起來的一種新型頻率合成技術,它具有頻率轉換速度快、相位噪聲低、相位連續和極高的頻率分辨率、體積小、重量輕等優點,主要缺點是工作頻段較低、頻段較窄,不能直接用于寬帶微波頻段,通常用于基帶信號的產生。

間接鎖相式頻率合成技術是利用鎖相環(PLL) 通過標準頻率源來控制壓控振蕩器得到所需的頻率,它具有電路簡單、相位噪聲低、輸出頻帶寬和控制靈活等優點,但是由于環路濾波器的存在,使得其轉換速度慢,一般使用于具有寬頻帶、較高頻率分辨率要求的場合。

1、直接模擬式頻率合成

直接模擬式頻率合成是最早出現的一種頻率合成器類型,其工作原理就是用倍頻、混頻電路對個或幾個基準頻率進行加、減、乘和除運算,從而產生所要求的頻率信號,根據其合成方法分為相關合成和非相關合成兩種。

直接模擬式頻率合成器的優點是頻率轉換快(一般可以做到1~2Hs)、分辨率高、相噪低、輸出頻率高; 缺點是合成結構復雜、尺寸及重量大,且輸出諧波、噪聲及寄生頻率難以抑制,適于頻率步進大、點頻數不多的電子系統。

2、鎖相式頻率合成

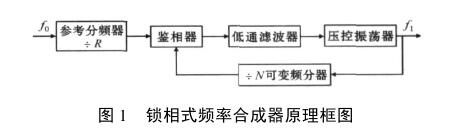

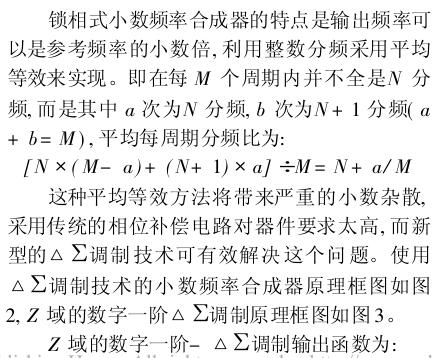

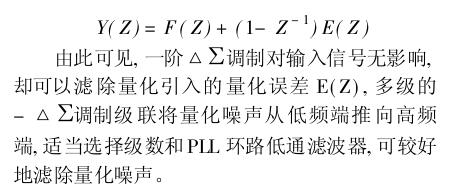

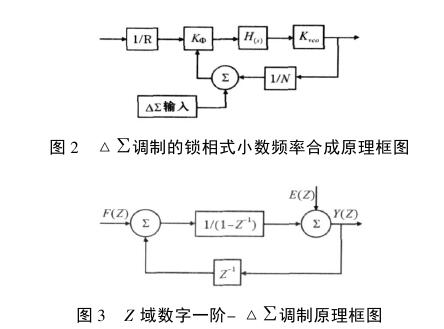

鎖相式頻率合成器是采用鎖相環( PIL) 進行頻率合成的一種頻率合成器,其工作原理是將壓控振蕩器產生的射頻信號和晶振輸出的參考信號分別進行分頻,得到兩個頻率近似相同的信號,并送到鑒相器進行比較,輸出誤差信號,經濾波后去控制壓控振蕩器的輸出,使壓控振蕩器輸出的射頻信號保持穩定,工作原理如圖1所示!

鎖相式頻率合成器分為整數頻率合成器和小數頻率合成器兩種。整數頻率合成器的頻率分辨率為參考頻率fr,為了獲得較高的頻率分辨率必然要減小fr,必然同時減小環路帶寬( 為保證環路穩定,一般要求環路帶寬小于參考頻率fr 的十分之一),從而導致轉換時間變長。因此,在實際應用中,為了獲得較高的頻率分辨率、快速轉換時間和寬頻帶特性,通常采用多環頻率合成技術和小數頻率合成技術。多環頻率合成器由多個鎖相環路組成,其中高位環提供頻率間隔較大的較高頻率輸出,低位環提供頻率間隔較小的較低頻率輸出,將兩部分輸出相加,便可獲得工作頻率和頻率分辨力高、轉換速度快的合成信號輸出。

鎖相式頻率合成器的優點是結構簡單、體積小、易于集成、調試方便、雜散低,所以應用非常廣泛,缺點是頻率轉換時間相對較長,難以滿足對跳頻時間要求快的電子系統。

3、直接數字式頻率合成

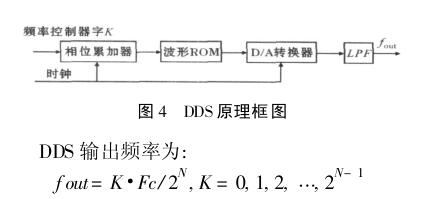

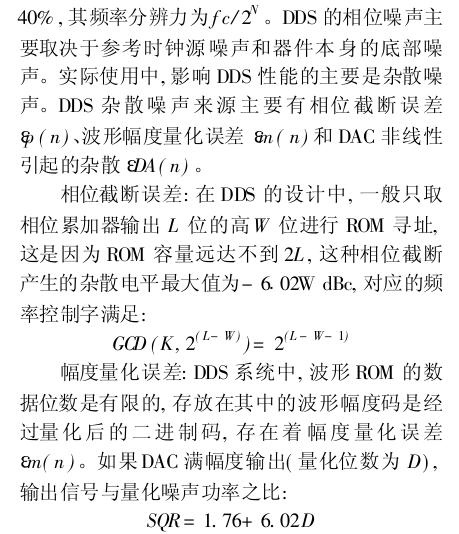

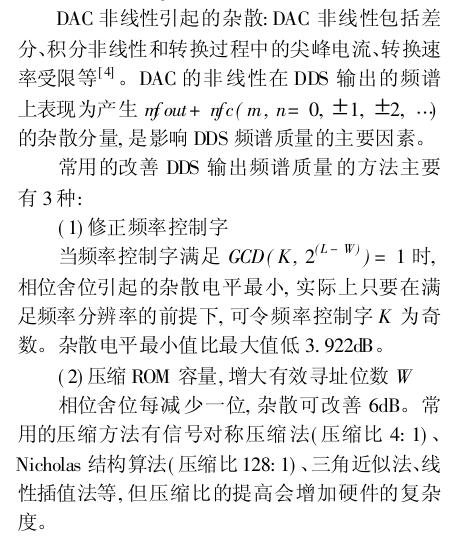

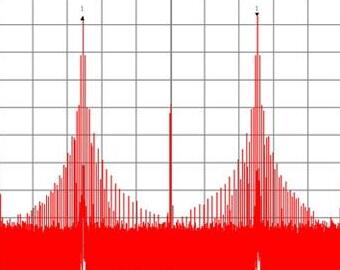

直接數字式頻率合成( DDS) 技術是采用全數字化實現方式。近年來,隨著集成電路工藝技術水平的提高,DDS 技術得到了迅速發展。DDS 主要由相位累加器、正弦波形表、D/A 轉換器、低通濾波器組成,工作原理如圖4。在系統時鐘fc 的控制下,將頻率控制字K 送到相位累加器,更新相位累加器的數據,然后把相位累加器中的數據N 作為地址對正弦ROM 表進行查詢,通過改變相位增量就可以改變DDS 的輸出頻率值。由波形ROM 存儲器取出的波形量化數據,經過A/ D 轉換器轉換成模擬電壓/ 電流,再經過低通濾波器將波形中的高次諧波濾除,得到DDS 的輸出頻率。

(3) 擾碼注入技術

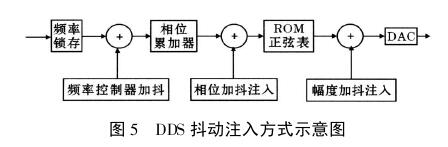

相位舍位引起雜散最根本的原因是$( n )是一個周期序列,因此破壞這種周期性成為減少DDS 雜散的主要研究方法。幾種抖動主入的方法; 可以對頻率控制字加抖; 可以對ROM 的尋址地址加抖,即相位抖動主入; 還可以對DAC 轉換前的數據加抖,即幅度抖動主入,如圖5 所示。

DDS 是- 一個全數字化的系統,具有易于集成、極快的跳頻速度、極高的頻率分辨率和頻率切換時相位連續等優點,缺點是雜散比較大、輸出頻率低。

4、混合式頻率合成

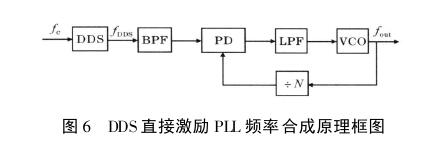

混合式頻率合成是近幾年非常流行的合成技術,主要有DDS 激勵PLL.DDS 內插PLL.DDS+ 倍頻( DAS)、DDS+ 混頻幾種合成方式。DDS 激勵PLL 頻率合成原理框圖如圖6。這種方案利用了DDS 的高分辨力來提高PLL 輸出的頻率分辨力和實現較高的頻率輸出,同時PLL 環路內的低通濾波器對帶外DDS 雜散起到很好的抑制作用,但頻率轉換時間取決于PIL。

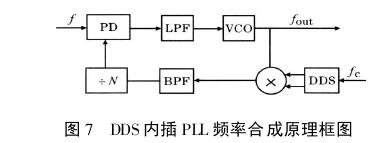

DDS 內插PLL 頻率合成原理框圖見圖7。由于DDS 輸出不經過PL 的倍頻,使DDS引入的相位噪聲和雜散不會使輸出端惡化,具有低的相位噪聲和良好的雜散性能,頻譜純度大大優于DDS激勵PL,作!這種方案仍然基于PL,頻率轉換時間仍然很慢。

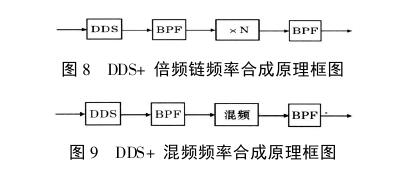

DDS+ 倍頻頻率合成原理框圖見圖8。用模擬倍頻器代替PLL,克服了DDS+ PLL 的頻率轉換時間長的弱點,同時利用多個倍頻器和濾波器組成的倍頻鏈提高頻綜器輸出頻率,拓展了頻綜器的輸出帶寬。但隨著輸出頻率擴高擴寬,輸出濾波器的復雜度越來越大,甚至不能用單一濾波器而是要用開關、濾波器組件來實現,目前國內研制的超高速頻率綜合器大都采用了這種方案。缺點是輸出帶寬均不寬,一般只有幾十兆赫。

DDS+ 混頻頻率合成原理框圖如圖9 所示,使用混頻器將DDS 輸出頻率直接搬移到微波頻段。第- 一級BPF 用來濾除DDS 的寬帶雜散,第二級BPF 用來濾除本振頻率、無用邊帶頻率和其它無用的混頻產物。本方案的優點在于DDS 本身的雜散電平和相位噪聲不增加,且頻率的捷變速度和分辨率均保持不變,即保持了DDS 的良好性能; 缺點在于輸出頻率范圍窄(當DDS 輸出頻率范圍超過一個倍頻程時,其低頻端二次諧波在混頻器輸出端變成雜散而無法濾除),且存在雙邊帶輸出、本振泄漏和其它混頻產物。

三、結束語

頻率合成技術從上世紀70年代開始,先后經歷了直接模擬式( DAS)、間接鎖相式、直接數字式(DDS): 三個階段的發展。隨著電子設備系統性能要求的不斷提高,頻率合成器技術也得到了快速發展,如體積小、性能高、高度集成的頻率合成器以及將DDS 和鎖相結合的混合式頻率合成器逐漸成為發展趨勢。同時,頻率合成器的小型化、低成本、高性能、多品種特性,也進一步推動了各種軍/ 民用電子系統的更新換代。

-

頻率合成

+關注

關注

1文章

20瀏覽量

22161 -

頻率合成技術

+關注

關注

1文章

4瀏覽量

6122

發布評論請先 登錄

集成電源是電源技術發展的必由之路

淺析開關電源技術發展趨勢

什么是集成無源元件?對PCB技術發展產生了什么影響?

光學活性中間體化學合成技術發展趨勢

淺析低成本CMOS圖像傳感器對醫學技術發展前景

鎖相與頻率合成技術圖書下載

評論