物聯(lián)網(wǎng) (IoT) 包括了如此廣泛的應(yīng)用,但往往是一項(xiàng)設(shè)計(jì)就需要多個(gè)無(wú)線接口,增加了空間、功耗和成本。聰明的物聯(lián)網(wǎng)設(shè)計(jì)師需要一種靈活的替代方式來(lái)支持多種不斷發(fā)展的標(biāo)準(zhǔn)。這便是軟件定義無(wú)線電 (SDR) 技術(shù)。SDR 這一理念并不新鮮;SDR 的創(chuàng)新之處在于解決了物聯(lián)網(wǎng)的困境:在同一網(wǎng)絡(luò)基礎(chǔ)設(shè)施上融合多種射頻技術(shù)的同時(shí)簡(jiǎn)化了設(shè)計(jì)、縮短了開發(fā)周期,并且降低了總體成本。本文介紹了基于定制 FPGA 主板的 SDR 設(shè)計(jì)已用于創(chuàng)建多協(xié)議無(wú)線數(shù)字基帶解決方案。

SDR 增加了網(wǎng)絡(luò)套接字的性能和效率

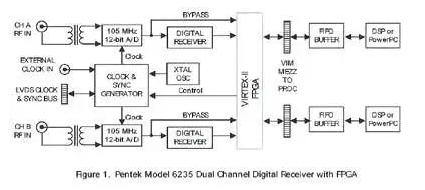

顧名思義,SDR 技術(shù)可以在同一硬件上支持多個(gè)無(wú)線協(xié)議。因?qū)嵤┣闆r而異,該技術(shù)可以同時(shí)支持這些協(xié)議,并且支持寬廣(或狹窄)的頻譜范圍。而且,使用 FPGA 在像基站這樣的無(wú)線設(shè)備中實(shí)施時(shí),隨著無(wú)線連接協(xié)議的不斷發(fā)展,SDR 平臺(tái)甚至可以通過(guò)重新編程來(lái)滿足網(wǎng)絡(luò)基礎(chǔ)設(shè)施的未來(lái)需求。VotaryTech的 SDR 平臺(tái) Arria 10AX115U3F4512SG 便是展現(xiàn) SDR 潛能的范例(圖 1)。這款英特爾?Arria?10 FPGA SoC 型網(wǎng)卡支持廣泛的無(wú)線應(yīng)用,包括移動(dòng)通信全球系統(tǒng) (GSM)、通用分組無(wú)線業(yè)務(wù) (GPRS)、LTE 網(wǎng)絡(luò)寬帶信號(hào)處理、跟蹤和遙測(cè)。這款主板是一個(gè)前端射頻平臺(tái),支持從 70 MHz 到 6 GHz 的無(wú)線應(yīng)用,但其可擴(kuò)展頻率可高達(dá) 15 GHz。

圖 1. 定制 FPGA 主板的視圖(適用于支持多種無(wú)線技術(shù)的基帶設(shè)計(jì))。(資料來(lái)源:英特爾)

定制 10AX115U3F4512SG 支持網(wǎng)絡(luò)應(yīng)用的所有信號(hào)處理要求,包括各種調(diào)制和解調(diào)方案。主板的基帶處理功能包括數(shù)字上變頻、數(shù)字下變頻以及標(biāo)準(zhǔn)調(diào)制器和解調(diào)器通信內(nèi)核。因此,該款 SDR 平臺(tái)支持無(wú)線信號(hào)收發(fā)。而且,10AX115U3F4512SG 可以在 Arria 10 FPGA 內(nèi)部執(zhí)行可編程和可微調(diào)基帶處理。Arria 10 FPGA 可執(zhí)行中頻濾波和下變頻等任務(wù)。

為什么在 SDR 中使用 FPGA

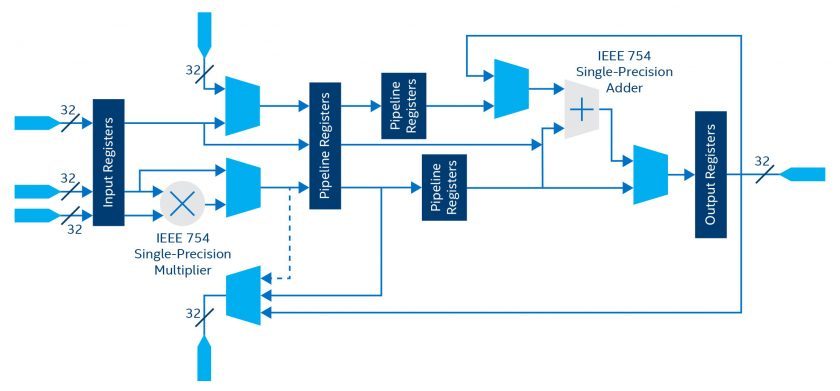

早期的 SDR 設(shè)計(jì)采用射頻前端模塊,深受工程師追捧,展現(xiàn)出了優(yōu)秀的潛能。但作為一項(xiàng)注重應(yīng)用的技術(shù),SDR 的設(shè)計(jì)并未取得實(shí)質(zhì)進(jìn)展。這在某種程度上是此類系統(tǒng)中定制 ASIC 的要求(和成本)造成的。目前,低風(fēng)險(xiǎn)的 SoC 正在取代 SDR 平臺(tái)中使用的傳統(tǒng) ASIC。舉例來(lái)說(shuō),相比上一代高端 FPGA 而言,中檔 FPGA SoC(例如采用 20 納米工藝制造的英特爾 Arria 10)的性能提升高達(dá) 15%,功耗則下降了 60%(圖 2)。而且,設(shè)備產(chǎn)生的熱量大幅下降,這在無(wú)線設(shè)備基站、移動(dòng)回程和遠(yuǎn)程無(wú)線頭設(shè)計(jì)中至關(guān)重要。更為重要的是,英特爾 Arria FPGA SoC 提供了大量可變精度 DSP 模塊和雙核 Arm Cortex-A9 處理器選項(xiàng)。Arria 10 FPGA SoC 中的 DSP 模塊采用三種模式:標(biāo)準(zhǔn)精度定點(diǎn)、高精度定點(diǎn)和單精度浮點(diǎn)(圖 2)。這使得無(wú)線系統(tǒng)設(shè)計(jì)師能夠?qū)?shù)字上變頻和下變頻及多速率濾波實(shí)施各種算法。

圖 2. 英特爾?Arria?10 FPGA 中的 DSP 模塊采用標(biāo)準(zhǔn)精度定點(diǎn)、高精度定點(diǎn)和單精度浮點(diǎn)模式。此處介紹的是單精度 DSP 模塊。(資料來(lái)源:英特爾)

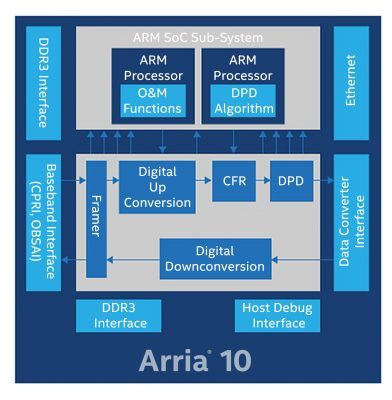

將這些計(jì)算功能與超過(guò) 100 萬(wàn)個(gè) FPGA 邏輯元素 (LE) 和 2,400 Mbps DDR4 SDRAM 內(nèi)存接口相結(jié)合,便成就了一款可編程度高的自適應(yīng)平臺(tái),可以適應(yīng)目前和不斷涌現(xiàn)的無(wú)線技術(shù)(圖 3)。

圖 3. 該無(wú)線回程設(shè)計(jì)結(jié)構(gòu)圖基于英特爾?Arria?10 FPGA SoC。(資料來(lái)源:英特爾)

可合成的 IP 內(nèi)核也可以集成到 FPGA 結(jié)構(gòu)中,允許無(wú)線設(shè)備設(shè)計(jì)人員將模數(shù)轉(zhuǎn)換器 (ADC) 輸出和數(shù)模轉(zhuǎn)換器 (DAC) 輸入提供到 FGPA 內(nèi)的基帶中。這就與 I/O 和協(xié)議控制一起,在協(xié)助基于 SDR 的射頻處理和基帶接口方面起到了重要作用。輕松訪問電路原理圖以及可以使用 10AX115U3F4512SG 的 Gerber 和電路板文件簡(jiǎn)化了 SDR 功能集成。Arria 10 對(duì)于通用公共無(wú)線電接口 (CPRI) 規(guī)格的支持也提升了平臺(tái)對(duì)于無(wú)線基站設(shè)計(jì)的適用性。

可編程性達(dá)到了物聯(lián)網(wǎng)的基本要求

VotaryTech 最初開發(fā)的這項(xiàng) SDR 設(shè)計(jì)是為了滿足對(duì)于無(wú)線調(diào)制解調(diào)器應(yīng)用的需要,但自從可以對(duì)硬件進(jìn)行編程以后,也可用于遙測(cè)和波形生成模擬器等應(yīng)用。Arria 10 FPGA SoC 實(shí)現(xiàn)的這種靈活性也使得 10AX115U3F4512SG 這類電路板十分適合物聯(lián)網(wǎng)部署,比如由各種不斷發(fā)展的技術(shù)和應(yīng)用構(gòu)成的物聯(lián)網(wǎng)。但或許最重要的是,本文展示了小型設(shè)計(jì)室如何利用具有高可配置度的 FPGA SoC 設(shè)備提供適應(yīng)目前和未來(lái)需求的解決方案。

作者簡(jiǎn)介

Majeed Ahmad is former Editor-in-Chief of EE Times Asia, a sister publication of EE Times. Moreover, as the Editor-in-Chief at Global Sources, a Hong Kong-based trade and technology publishing house, he spearheaded magazines related to electronic components, consumer electronics, and computer, security and telecom products. Majeed is a journalist with an engineering background and two decades of experience in writing, editing and acquiring technical content. He is also author of six books on electronics: Smartphone, Nokia’s Smartphone Problem and The Next Web of 50 Billion Devices, Mobile Commerce 2.0, Age of Mobile Data, and Essential 4G Guide.

-

FPGA

+關(guān)注

關(guān)注

1629文章

21748瀏覽量

603795 -

物聯(lián)網(wǎng)

+關(guān)注

關(guān)注

2909文章

44694瀏覽量

373906 -

軟件定義無(wú)線電

+關(guān)注

關(guān)注

0文章

10瀏覽量

8610

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

用于無(wú)線電的衰減器選擇指南

NVIDIA推出適用于網(wǎng)絡(luò)安全的NIM Blueprint

陸地移動(dòng)無(wú)線電調(diào)制分析儀的技術(shù)原理和應(yīng)用場(chǎng)景

智能選擇ADC/DAC可實(shí)現(xiàn)更好的軟件定義無(wú)線電設(shè)計(jì)

適用于 Microsemi? RTG4? FPGA 的 TI 航天級(jí)電源解決方案應(yīng)用手冊(cè)

高頻與射頻技術(shù)只能應(yīng)用于無(wú)線電系統(tǒng)嗎

無(wú)線電時(shí)鐘的dcf信號(hào)是什么意思

適用于電池充電器的無(wú)線電源解決方案

如何利用藍(lán)牙產(chǎn)品執(zhí)行射頻無(wú)線電測(cè)試

將FPGA嵌入DSP驅(qū)動(dòng)的軟件無(wú)線電應(yīng)用中

適用于 Xilinx? MPSoC 和 FPGA的可配置多軌PMU TPS650864數(shù)據(jù)表

適用于 Xilinx? MPSoC 和 FPGA 的可配置多軌PMU TPS650864數(shù)據(jù)表

網(wǎng)絡(luò)研討會(huì)預(yù)告 | 《如何使用Zynq Ultrascale+ RFSoC實(shí)現(xiàn)軟件定義無(wú)線電》

軟件無(wú)線電安全之GNU Radio基礎(chǔ)知識(shí)

適用于Linux的QRadioLink SDR客戶應(yīng)用程序

利用定制 FPGA 主板實(shí)施適用于物聯(lián)網(wǎng)的軟件定義無(wú)線電

利用定制 FPGA 主板實(shí)施適用于物聯(lián)網(wǎng)的軟件定義無(wú)線電

評(píng)論