0 引言

隨著集成電路設計的快速發(fā)展,系統(tǒng)芯片(System-on-a-Chip,SoC)的集成度越來越高,從而對信號之間交流的要求也變高[1-2]。由于串行外設接口(Serial Peripheral Interface,SPI)總線協(xié)議具有全雙工模式、占用I/O端口少、協(xié)議靈活等優(yōu)點,在實時時鐘、AD轉(zhuǎn)換器、數(shù)字信號處理器和數(shù)字信號解碼器之間得到了廣泛應用[3-4]。

目前,SPI IP核已經(jīng)成為SoC的標準配置,相關人員也做了很多研究。例如,周雪榮等人面向AD9222設計的一款SPI模塊[5],可以配置為主機模式且符合AD9222芯片的接口時序;汪永琳等人設計的SPI接口[6],實現(xiàn)了SPI主從機之間數(shù)據(jù)的雙向傳輸且滿足三線半全工工作方式;李大江等人基于FPGA的SPI總線設計[7],分別設計了主機和從機。上述SPI設計可以適用于不同的應用場合,但是在SoC中進行通信時,不具有主從模式下動態(tài)可重構的能力。因此,本文根據(jù)SPI總線協(xié)議,設計了一種主從模式動態(tài)可重構,支持四線全雙工,允許七種時鐘傳輸速率的SPI IP核,并對其邏輯資源消耗和功耗問題進行了優(yōu)化。

1 SPI工作原理

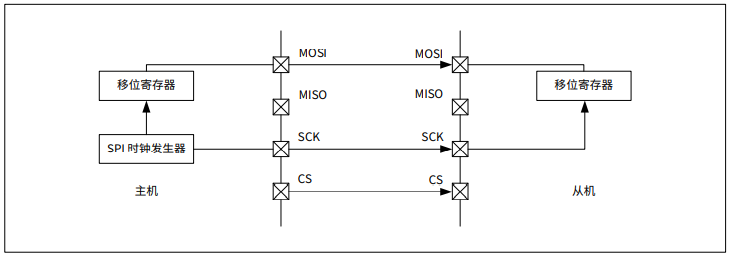

SPI總線協(xié)議是由Motorola公司首先提出的,主要應用于單片機系統(tǒng)中短程通信的同步串行通信接口規(guī)范[8]。SPI總線協(xié)議規(guī)定,它以主機或從機方式工作,主從機之間的數(shù)據(jù)傳輸存在4種數(shù)據(jù)傳輸模式并由cpol(時鐘極性)和cpha(時鐘相位)來控制,如表1所示。當cpol=0時,sclk的空閑電平為0;當cpol=1時,sclk的空閑電平為1。當cpha=0時,在空閑狀態(tài)到有效狀態(tài)邊沿采集數(shù)據(jù);當cpha=1時,在有效狀態(tài)到空閑狀態(tài)邊沿采集數(shù)據(jù)[9]。

在SoC中SPI IP核的傳統(tǒng)連接方式如圖1所示。通信過程中,SPI通過片上總線將CPU核傳輸?shù)牟⑿袛?shù)據(jù)轉(zhuǎn)換為串行數(shù)據(jù),與從機進行數(shù)據(jù)交換;并把從機傳輸?shù)拇袛?shù)據(jù)轉(zhuǎn)換成并行數(shù)據(jù),通過片上總線發(fā)送給CPU核[10]。對SPI從機來說,它會在被主機選中的情況下與主機進行數(shù)據(jù)的傳輸[11]。

2 SPI IP核設計

2.1 模塊劃分和接口定義

2.1.1 模塊劃分

根據(jù)SPI功能的不同,將所設計的SPI IP核劃分為如圖2所示的3個模塊:寄存器配置塊(Register Configuration Block,RCB)、數(shù)據(jù)傳輸塊(Data Transfer Block,DTB)和錯誤中斷塊(Fault Interrupt Block,F(xiàn)IB)。RCB由CPU核對其進行配置,如主從模式、時鐘極性和時鐘相位等;DTB根據(jù)配置的信息來進行主從機間的數(shù)據(jù)傳輸;FIB在出現(xiàn)模式錯誤(例如當SPI配置為主機時,從機選擇端口被拉低)、讀寫沖突等問題時會向CPU核發(fā)出中斷請求。

2.1.2 端口定義

nwr和nrd分別是寫使能和讀使能端口;addr是地址端口;idata和odata分別是數(shù)據(jù)輸入和輸出端口。當?shù)刂酚行r,數(shù)據(jù)輸入和輸出端口根據(jù)讀寫使能的配置來進行數(shù)據(jù)的輸入和輸出操作。spen、mstr、cpol和cpha 4個端口依次是SPI使能端、主從機配置端、時鐘極性和時鐘相位端,使得對SPI IP核進行配置更加直接和方便。

misoo、misotri和misoi 3個端口與一個三態(tài)緩沖器連接,以提供一個外部雙向端口miso,外部雙向端口mosi和sclk原理相同。這些雙向端口在有限狀態(tài)機模塊的控制下被配置為不同的傳輸方向,以此來解決主機模式和從機模式下數(shù)據(jù)傳輸端口傳輸方向相反的問題。miso在從機模式下發(fā)送數(shù)據(jù),在主機模式下接收數(shù)據(jù);mosi在主機模式下發(fā)送數(shù)據(jù),在從機模式下接收數(shù)據(jù);sclk在主機模式下發(fā)送時鐘,在從機模式下接收時鐘。同時,SPI IP核通過復用一個移位寄存器就可以完成主機和從機模式下的數(shù)據(jù)傳輸,實現(xiàn)了主從模式可配置的能力并節(jié)省了芯片面積。ssn是從機選擇端口,配置為從機時才使用,低電平有效。

int是中斷控制端口,當數(shù)據(jù)傳輸完成或SPI被配置為主機而ssn(從機選擇)端口為低電平等情況時,F(xiàn)IB模塊就會產(chǎn)生中斷請求。

2.2 電路設計

2.2.1 SPI可重構電路狀態(tài)機的設計

SPI可重構電路狀態(tài)機的設計,如圖3所示。當復位信號有效或者SPI使能端口spen被配置為低電平無效狀態(tài)時,可重構電路狀態(tài)機就會處于空閑狀態(tài)。此時,可向主機模式或從機模式進行轉(zhuǎn)移。

轉(zhuǎn)移為主機模式時,首先需要把mstr端口配置為1。然后,有兩種情況可以轉(zhuǎn)移到主機模式:(1)配置從機選擇端口無效位ssdis為高電平有效狀態(tài);(2)配置ssn端口為高電平無效狀態(tài)。

轉(zhuǎn)移為從機模式時,首先需要把mstr配置為0。然后,有3種情況可以轉(zhuǎn)移到從機模式:(1)當配置cpha為高電平時,并配置ssdis位為有效狀態(tài),此種情況適用于只有一個從機下的數(shù)據(jù)傳輸;(2)當配置cpha為高電平時,檢測到ssn端口為低電平;(3)當配置cpha為低電平時,檢測到ssn端口的下降沿。

當狀態(tài)機從空閑狀態(tài)已經(jīng)過渡到主機或者從機模式時,就會判斷數(shù)據(jù)的傳輸是否完成,當傳輸未完成時,就會保持在當前狀態(tài);當傳輸已完成時,就會轉(zhuǎn)移到空閑狀態(tài)。此外,當前模式出現(xiàn)錯誤時,也會轉(zhuǎn)移到空閑狀態(tài)。SPI可重構電路狀態(tài)機如圖3所示。

由狀態(tài)轉(zhuǎn)移圖可知,此SPI IP核可實現(xiàn)空閑狀態(tài)、主機模式和從機模式之間的狀態(tài)轉(zhuǎn)換,具有在線動態(tài)可重構的特性。

2.2.2 時鐘分頻

主機模式下的串行時鐘由7位計數(shù)器、數(shù)據(jù)選擇器和D觸發(fā)器組成的時鐘分頻模塊產(chǎn)生,如圖4所示。

輸出時鐘sclko取決于CPU核對控制寄存器的配置,當對控制器寄存器相應的三位配置都為1時,sclko的值為cpol的值,不產(chǎn)生時鐘,其他情況均對時鐘有分頻作用。因此,此時鐘分頻模塊可對系統(tǒng)時鐘產(chǎn)生7種分頻,如表2所示。

3 仿真與驗證

3.1 仿真平臺搭建

為了方便驗證此SPI IP核的正確性,設計了模擬CPU核功能的發(fā)送接收模塊、驗證IP核(Verification IP,VIP)模塊和數(shù)據(jù)比較模塊等。發(fā)送接收模塊產(chǎn)生指令和數(shù)據(jù)對SPI IP核和VIP模塊進行配置。配置完成后,SPI IP核和VIP模塊進行主從機之間數(shù)據(jù)的傳輸;傳輸完成后,發(fā)送接收模塊分別讀取SPI IP核和VIP模塊傳輸?shù)臄?shù)據(jù)。最后,比較模塊從CPU核讀取所傳輸?shù)臄?shù)據(jù)并驗證數(shù)據(jù)的正確性。仿真原理如圖5所示。

3.2 仿真及結果分析

最后,使用NC-Verilog對其進行仿真驗證,主從模式下的仿真時序如圖6所示。首先,通過發(fā)送接收模塊對SPI IP核的控制寄存器依次寫入h’10和h’50(配置SPI為主機模式,SPI接口有效)。同時,配置VIP模塊為從機。然后,設置主機要發(fā)送的數(shù)據(jù)為h’aa,從機要發(fā)送的數(shù)據(jù)為h’55,在sclko(對clk時鐘2分頻)時鐘頻率下,主機的mosio(主機輸出,從機輸入)端口串行發(fā)送數(shù)據(jù)h’aa,misoi(主機輸入,從機輸出)端口串行接收數(shù)據(jù)h’55,傳輸完成后讀取狀態(tài)寄存器的值為h’80(傳輸完成),讀取數(shù)據(jù)寄存器的值為h’55(傳輸成功)。然后,對控制寄存器寫入h’40(配置SPI為從機,SPI接口有效)。同時,配置VIP模塊為主機,ssn(從機選擇端口)變?yōu)榈碗娖接行顟B(tài)。在sclki(對clk時鐘4分頻)時鐘頻率下,從機的miso(從機輸出,主機輸入)端口串行發(fā)送數(shù)據(jù)h’55,mosii(從機輸入,主機輸出)端口串行接收數(shù)據(jù)h’aa,傳輸完成后讀取狀態(tài)寄存器的值為h’80(傳輸完成),讀取數(shù)據(jù)寄存器的值為h’aa(傳輸成功)。

主機模式下不同時鐘速率下的數(shù)據(jù)傳輸如圖7所示。圖中給出了對clk時鐘2分頻時,主機發(fā)送數(shù)據(jù)為h’aa,接收數(shù)據(jù)為h’55;對clk時鐘4分頻時,主機發(fā)送數(shù)據(jù)為h’55,接收數(shù)據(jù)為h’aa;對clk時鐘8分頻時,主機發(fā)送數(shù)據(jù)為h’aa,接收數(shù)據(jù)為h’55等情況下的數(shù)據(jù)傳輸情況。在不同分頻模式下,數(shù)據(jù)傳輸能正常傳輸且結果正確。

仿真結果表明:此SPI IP核符合SPI總線協(xié)議并且滿足設計規(guī)范的要求。綜合結果顯示:在0.13 μm工藝下消耗1 062個邏輯門,在系統(tǒng)工作頻率80 MHz下的功耗約為0.395 7 mW。

4 結論

本文根據(jù)SPI總線協(xié)議設計了一種高性能主從模式動態(tài)可重構的SPI IP核,并對該IP核的模塊劃分、接口定義和可重構電路狀態(tài)機等進行了詳細描述。結果顯示,此設計符合SPI總線協(xié)議,實現(xiàn)了7種時鐘分頻,支持4種數(shù)據(jù)傳輸模式;在保證功能和性能情況下,邏輯資源消耗更少、功耗更低。

-

soc

+關注

關注

38文章

4182瀏覽量

218512 -

SPI接口

+關注

關注

0文章

259瀏覽量

34431 -

IP核

+關注

關注

4文章

329瀏覽量

49549

發(fā)布評論請先 登錄

相關推薦

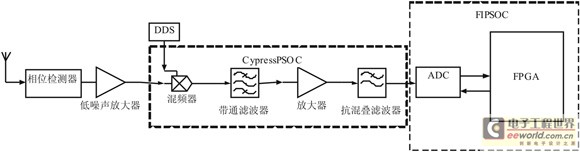

基于PAD的接收機動態(tài)可重構結構應用

怎么設計PAD在接收機動態(tài)可重構結構中的應用?

可擴展的高性能RISC-V 內(nèi)核IP

可重構體系結構分為哪幾種?動態(tài)可重構系統(tǒng)有哪些應用實例?

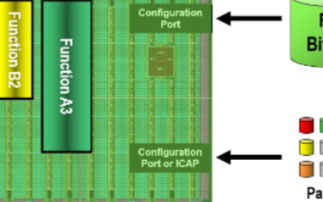

怎么實現(xiàn)基于FPGA的動態(tài)可重構系統(tǒng)設計?

可滿足高性能數(shù)字接收機動態(tài)性能要求的ADC和射頻器件有哪些?

劃分和時延驅(qū)動的動態(tài)可重構FPGA在線布局算法

動態(tài)可重構系統(tǒng)的通信結構分析

PAD在接收機動態(tài)可重構結構中的應用設計

可重構技術分析及動態(tài)可重構系統(tǒng)設計

FPGA動態(tài)可重構技術是什么,局部動態(tài)可重構的時序問題解決方案

可重構計算:基于FPGA可重構計算的理論與實踐 1.器件架構 譯文(一)

關于高性能主從模式動態(tài)可重構的SPI IP核的設計

關于高性能主從模式動態(tài)可重構的SPI IP核的設計

評論