Quartus II 11.0中調用ModelSim-Altera 6.5e詳細

一、Altera官網下載兩款軟件并安裝

下載網址:https://www.altera.com/download/software/modelsim/zh_cn,選擇Quartus II 網絡版、ModelSim-Altera入門版。目前這兩款軟件都是免費的,不需要許可證,安裝簡單,使用期限是30天。

【注意】務必記住安裝的路徑,特別是ModelSim-Altera的安裝路徑。

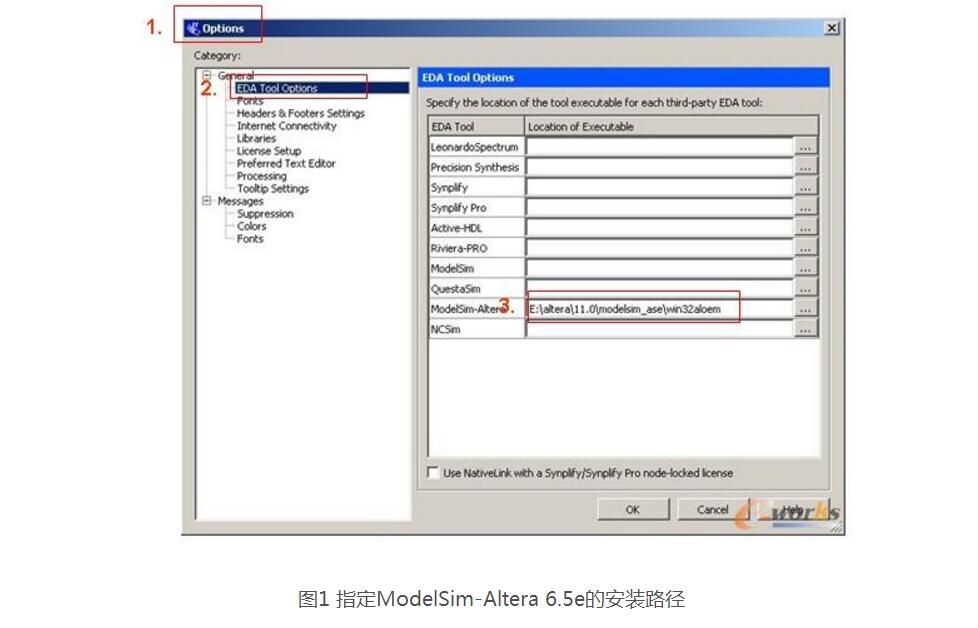

二、指定ModelSim-Altera 6.5e的安裝路徑

打開Quartus II 11.0軟件,新建工程和文件并保存。

1.然后在菜單欄選擇 tools-》options;

2.在options選項卡中選中EDA tool options;

3.在該選項卡中下面的ModelSim-Altera一項指定安裝路徑為E:/Altera/11.0/modelsim_ae/win32aloem(其中E:/Altera/11.0/modelsim_ae/為我電腦中ModelSim-Altera 6.5e的安裝路徑)

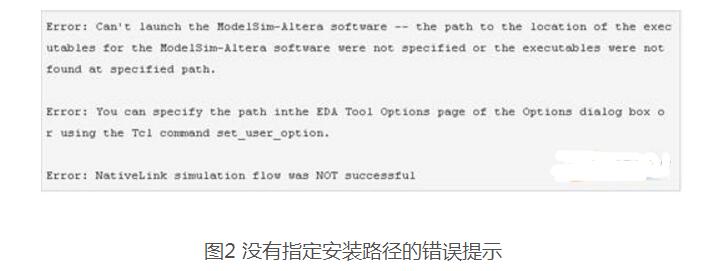

【注意】 如果沒有指定ModelSim-Altera 6.5e的安裝路徑,調用ModelSim-Altera的時候會出現如下的錯誤提示:

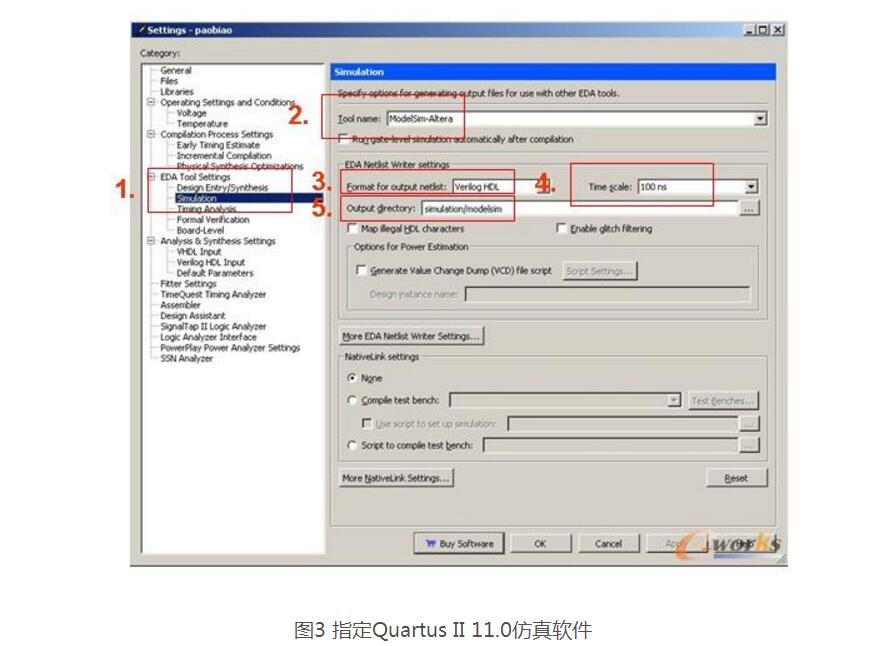

三、指定Quartus II 11.0仿真軟件

在Quartus II 11.0界面菜單欄中選擇Assignments-》Settings。

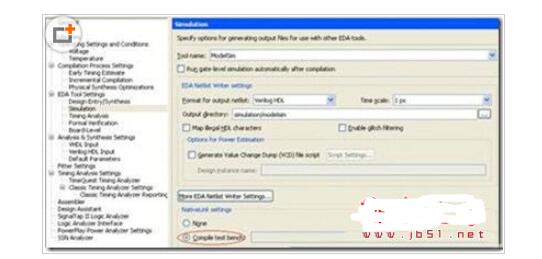

1.選中該界面下EDA Tool settings中的Simulation一項;

2.Tool name中選擇ModelSim-Altera;

3.Format for output netlist中選擇開發語言的類型Verilog或者VHDL等,

4.Time scale 指定時間單位級別

5.Output directory指定測試文件模板的輸出路徑(該路徑是工程文件的相對路徑)。

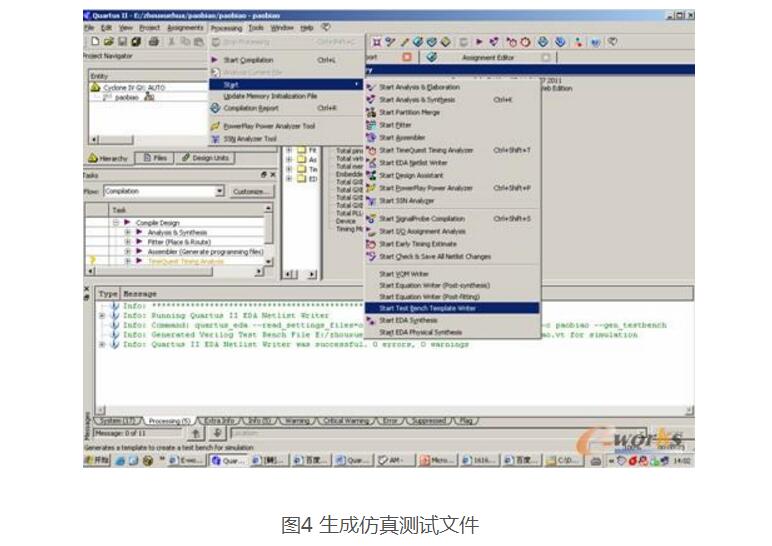

四、生成仿真測試文件

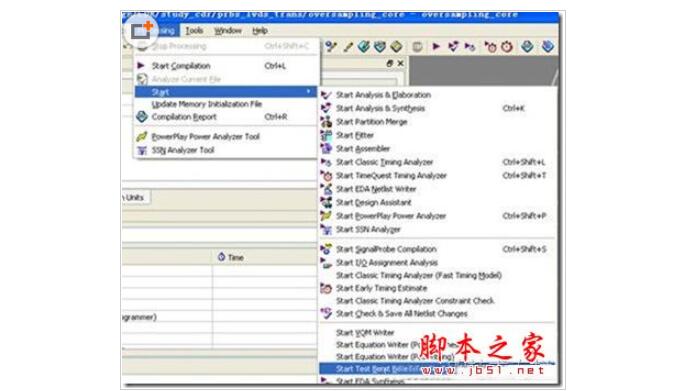

選擇Quartus II 11.0開發界面菜單欄下Processing-》Start-》Start Test Bench Template Writer,提示生成成功。

五、配置選擇仿真文件

打開仿真測試文件(在上述3中指定的Output directory 目錄下找到后綴名為“.vt”的文件)并根據自己需要進行編輯。

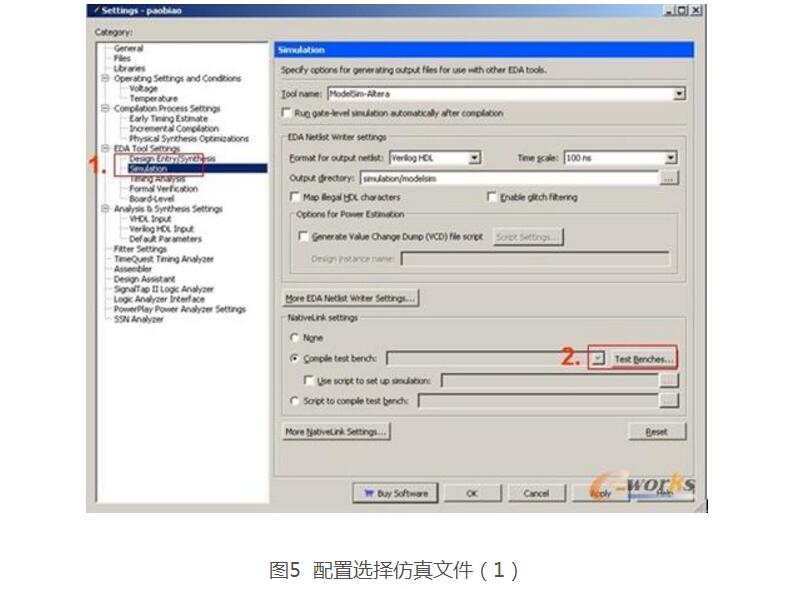

1. 在Quartus II 11.0界面菜單欄中選擇Assignments-》Settings-》EDA Tool settings-》Simulation;

2.選擇Compile test bench右邊的Test benches;

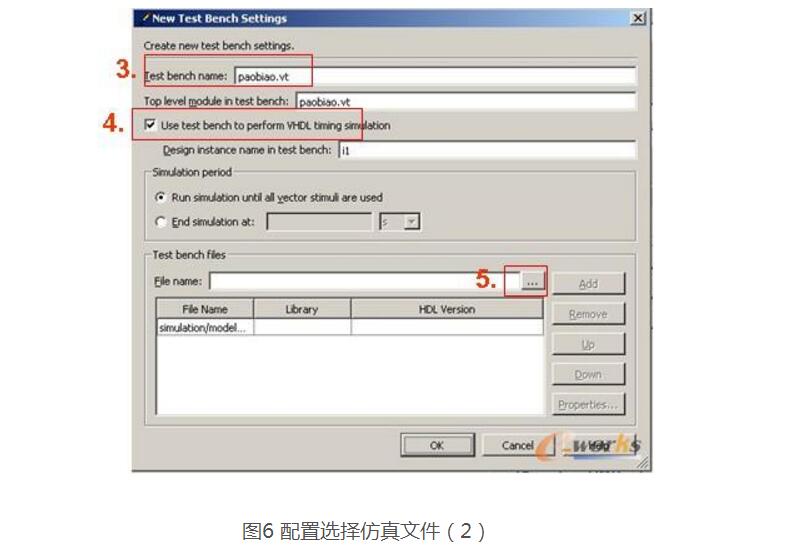

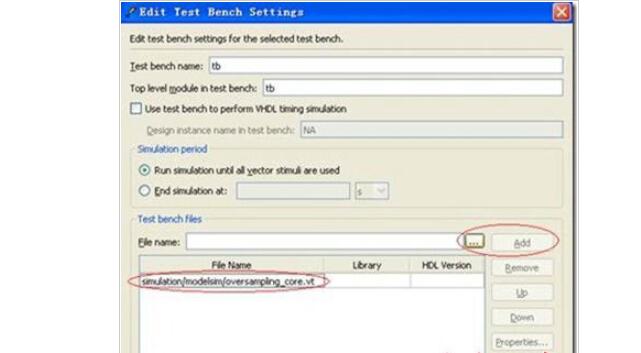

3.然后在出現的界面中選擇New,在新出現的界面中Test bench name 輸入測試文件名字,在Top level module in test bench 欄中輸入測試文件中的頂層模塊名;

4.選中Use test bench to perform VHDL timing simulation并在Design instance name in test bench中輸入設計測試文件中設計例化名默認為i1;

5.然后在Test bench files欄下的file name 選擇測試文件(在第3步中指定的測試文件輸出路徑下的后綴名為“ .vt ” 文件的測試文件),然后點擊add,一步一步OK。

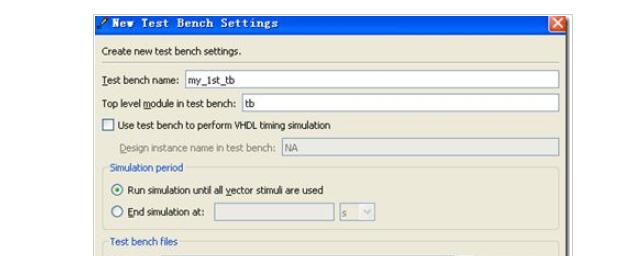

【注意】Test bench name和Top level module in test bench 以及Design instance name in test bench分別為“.vt”文件的文件名、vt文件中頂層實體模塊名、Verilog或者VHDL文件中的模塊的例化名。

六、仿真文件配置完成后回到Quartus II 11.0 開發界面

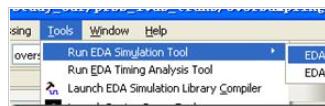

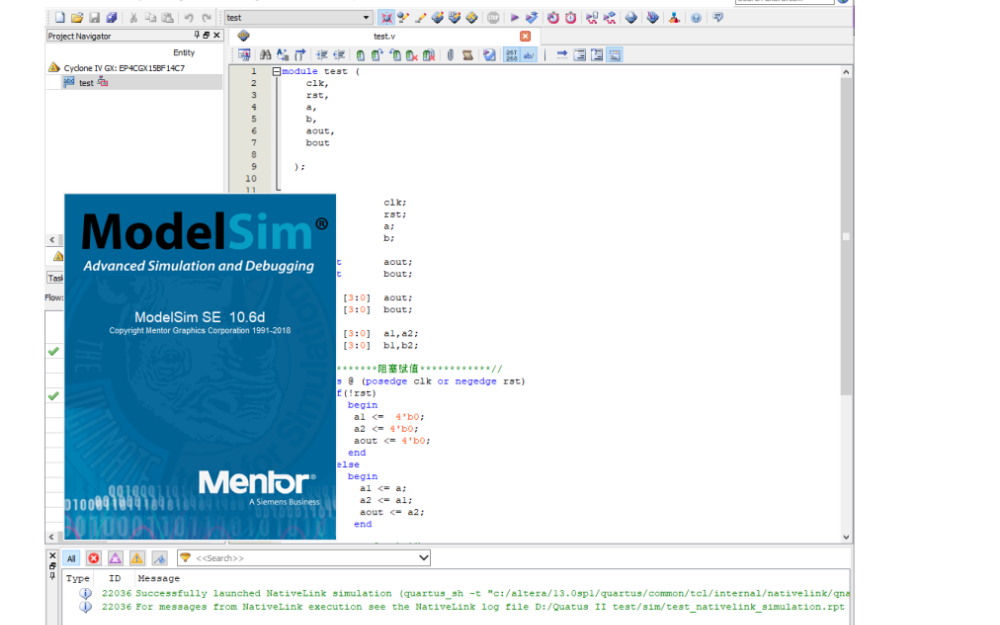

在Quartus II 11.0界面菜單欄中選擇菜單欄Tools中的Run EDA Simulation Tool-》EDA RTL Simulation 進行行為級仿真,接下來就可以看到ModelSim-Altera 6.5e的運行界面,觀察仿真波形。

Quartus II調用modelsim無縫仿真詳細圖文教程

1. 設定仿真工具

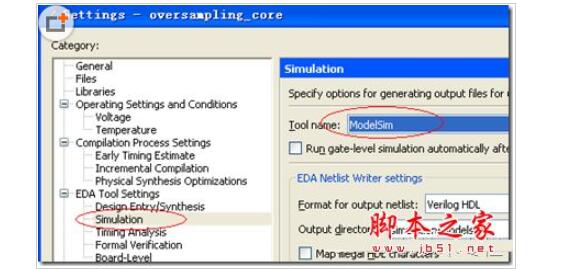

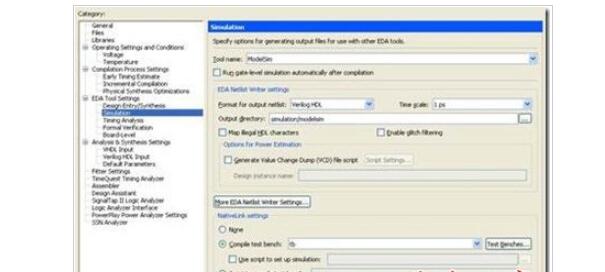

assignmentèsettingèEDA tool settingèsimulation 選擇你需要的工具。

2. 自動產生測試激勵文件模板:

processingèstartèStart test bench template writer

我們點擊之后系統會自動在目錄:當前文件夾è simulation è modelsim (這個文件夾名字跟你選的仿真工具有關) 中產生一個測試激勵文件 xxx.vt(Verilog test bench) 或者 xxx.vht(VHDL test bench), 文件名跟你工程中的Top module 的名字一樣, 后綴為.vt或者.vht。

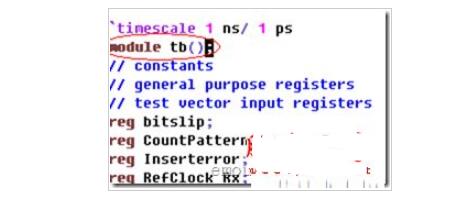

3. 編輯走動生成的test bench文件

我們加入自己需要的激勵以及初始化語句,這里我們還要修改test bench的模塊名字為tb(我們會看到這個名字和后面的設定有聯系)。

4. 連接test bench,我們需要從Quartus中自動調用仿真工具,所以需要設定Native Link選項。

a) 還是在simulation的設置頁面里,設定 Native Link對話框中的設定。我們這里因為需要工具自動調用激勵所以選中

b) 點擊右邊的Test Benches, 我們需要在這里設定一個相關聯的test bench.

這里會彈出一個讓你指定test bench的對話框,因為我們之前沒有指定任何的test bench,所以這里是空白的。

c) 指定test bench

因為我們是第一次產生test bench,點擊new.

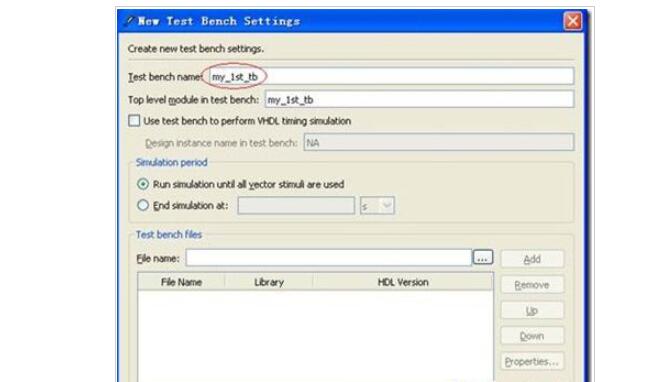

點擊New之后會產生一個New Test bench setting的對話框,在這里你將test bench和你的相應的test bench file進行綁定。

我們這里在Test bench name的對話框中輸入一個名字”my_1st_tb”, 我們將看到,在下面的Top level module in test bench對話框中也自動顯示”my_1st_tb”。 注意這個名字應該和你的test bench 中的module name一直,我們之前在第3步的時候將test bench的module name已經改成了tb,所以我們這里應該把對話框中的名字改成tb。

d) 加入test bench文件

5. 進行仿真

當這些設定都完成了之后, 選擇菜單

toolèRun EDA Simulation toolèEDA RTL simulation

就可以直接調用modelsim進行仿真。

6. 小技巧:

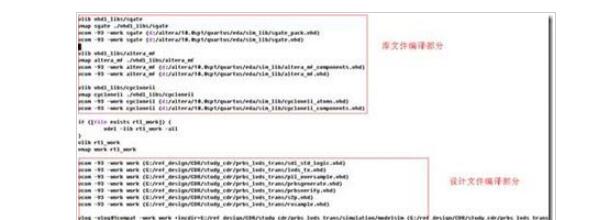

我們這樣調用仿真,如果是Modelsim AE每次不會編譯lib文件,但如果我們使用的是Modelsim SE版本,每次調用都需要重新編譯庫,非常不爽,在這里我們建議自己修改腳本文件,進行仿真。

a) 當我們按照之前的描述,運行完仿真之后,停留在Modelsim的界面。

b) 在Modelsim界面的命令行上,我們點向上的方向鍵,就會出現我們上一條指令, 我們可以看到是

do xxxx.do 這說明工具執行的上一個命令式 xxxx.do這個腳本文件,我們這里的例子是

do oversampling_core_run_msim_rtl_verilog.do

i. 我們知道了工具執行的腳本,我們就可以按照自己的想法去改變這個腳本了。使用edit oversampling_core_run_msim_rtl_verilog.do命令,可以看到這個腳本的內容(當然我們也可以使用Ultra Edit或者VIM等文本編輯軟件去打開這個腳本文件)。這個腳本通常分成3部分 庫文件編譯部分,設計文件編譯,運行參數設定和開始執行部分

ii. 通常來說庫文件只在第一次編譯的時候,需要編譯,后面我們只需要在仿真的時候指定庫文件的位置就好了,不需要每次都編譯。因此我們可以注釋掉“庫文件編譯部分”。下面圖中紅色框中的部分就是被注釋掉的庫編譯部分,這樣會節省我們的仿真時間,注意在腳本語言中#是注釋符。

iii. 我們將編輯過的腳本文件另存為sim.do, 在以后的仿真中我們可以在Modelsim命令行中,直接在腳本中運行do sim.do(當然是先需要將Modelsim的工作目錄改到 工程所在文件夾/simulation/modelsim/)。

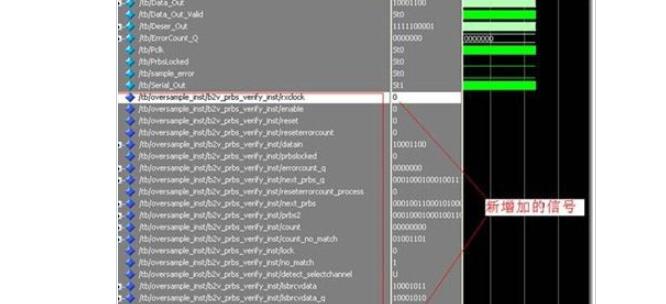

c) 另外腳本生成的波形文件通常是將test bench的頂層加入到圖形畫面中我們可以看到在腳本的第3部分(運行參數和開始執行)部分,默認命令式

add wave *, 這條命令就是講 test bench頂層的所有信好加入到wave窗口中。

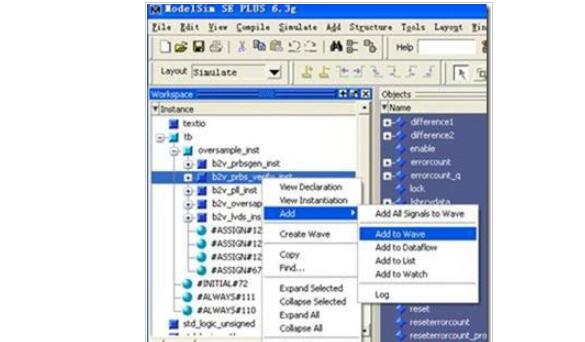

對我們來說,在調試階段,有很多底層信號都是想觀測的,所以需要再手動修改一下命令

i. 在modelsim的窗口中,選中自己想要關心的模塊,右鍵可以將自己關心的信號加入wave波形中

ii. 此時我們在wave 窗口中可以將這個波形的格式存下來,在wave窗口中點菜單fileèsave… 選擇文件名為wave.do.

iii. 在我們執行的腳本中將add wave *,這個命令替換成do wave .do, 就可以在每次執行仿真的時候自動添加想要觀測的波形了。

7. 接下來最后一個問題,怎樣才能一次性的編譯好庫文件,讓軟件不再每次編譯。其實altera已經為客戶準備了相應的選項,只不過藏得比較深,不好找。

a) 一次性編譯庫:

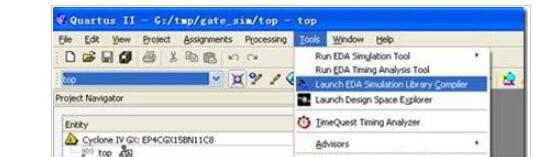

i. 點擊toolè launch EDA simulation Library Compiler

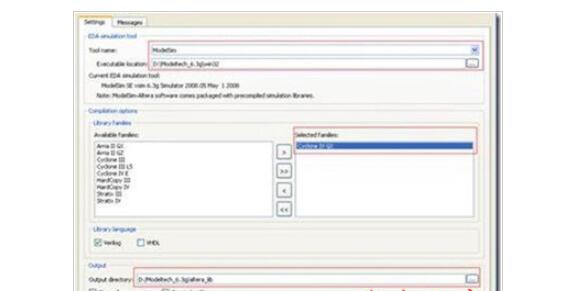

ii. 我們會看到一個讓我們選擇器件的頁面。根據你的實際情況選擇下面的設定。點擊start compile,軟件會自動幫你完成編譯,然后關掉就好,至此你應該已經完成了庫的編譯。

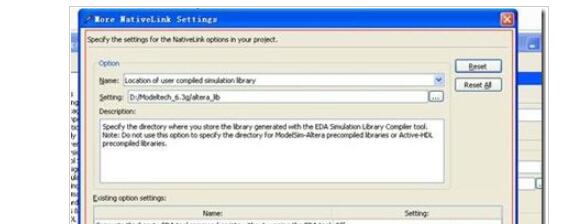

iii. 接下來我們需要在QII的仿真設定頁面做一些修改。

我們需要回到設定界面

Assignmentèsettingèsimulationèmore Nativelink setting

設定好相應的路徑。

好了,重新run仿真,就發現不會再編譯我們的庫文件了。

-

ModelSim

+關注

關注

5文章

174瀏覽量

47162 -

quartus

+關注

關注

16文章

171瀏覽量

74622

發布評論請先 登錄

相關推薦

關于調用modelsim

求助:關于quartus II 和 modelsim 聯合仿真設置問題

Quartus17.0調用Modelsim仿真PLL無輸出

quartus 17.1調用modelsim 出錯

FPGA視頻教程之Quartus.II調用ModelSim仿真實例詳細資料說明

Quartus.II調用ModelSim仿真實例

使用Vivado 2017調用Modelsim的詳細步驟

FPGA的視頻教程之modelsim和quartus的使用詳細資料說明

如何在Quartus13.0中調用Modelsim詳細的步驟說明

FPGA的Quartus ModelSim的安裝介紹和使用等基本操作資料免費下載

關于quartus如何調用modelsim詳細解說

關于quartus如何調用modelsim詳細解說

評論