摘要:成功開(kāi)發(fā)超厚介質(zhì)膜的淀積和刻蝕工藝、超厚金屬銅的電鍍和化學(xué)機(jī)械研磨等工藝,采用與 CMOS 完全兼容的銅互連單大馬士革工藝制作了超厚金屬銅集成電感。該超厚金屬銅電感在 1~3 GHz 頻率范圍內(nèi)的電感值均勻,在 2.5 GHz 頻率下的 Q 值達(dá)到 11。并且進(jìn)一步研究了線圈圈數(shù)、金屬線寬和金屬間距對(duì)電感值和 Q 值的影響。

在射頻集成電路(RFIC)工藝中,硅襯底螺旋電感(SIOS)是影響許多 RF 集成電路性能的關(guān)鍵部分,使用高 Q 值的片上集成電感,可以提高 RF 模塊電路的可靠性和電路設(shè)計(jì)效率。常用于提高電感 Q 值的一種方法是采用高阻襯底(2 kΩ?cm)來(lái)降低襯底的寄生效應(yīng),但這種方法與傳統(tǒng) CMOS 工藝不兼容。因?yàn)樵?CMOS 或者 BiCMOS 工藝中,襯底的電阻率一般不會(huì)超過(guò) 30 Ω?cm[1-3]。另一種提高集成電感 Q 值,且與 CMOS 兼容的方法是采用銅互連技術(shù)降低金屬線圈電阻。因?yàn)殡姼械?Q 值是與金屬線圈電阻成反比的,減小金屬線的電阻是增加 Q 值最有效的方法[4-5]。增加金屬線寬和厚度都可以降低電阻,但增加線寬會(huì)影響集成度,同時(shí)也會(huì)增加寄生電容,從而影響其工作頻率,增大電感和襯底的耦合。在工藝上,金屬的厚度也不能無(wú)限制的增加,當(dāng)鋁線的厚度超過(guò) 3 μm,線條很容易斷裂,同時(shí)會(huì)給刻蝕工藝帶來(lái)很大的挑戰(zhàn)。

銅由于具有較低的電阻率(1.7 μΩ?cm)在理論上可以替代鋁,作為電感,并且有效降低金屬線圈電阻。目前工業(yè)中,銅互連采用大馬士革結(jié)構(gòu)的鑲嵌工藝和化學(xué)機(jī)械拋光(CMP)平坦化代替了刻蝕工藝,因此銅線可以比鋁線做得更厚,金屬線圈電阻更小。本文對(duì)超厚金屬銅互連工藝進(jìn)行了研究,制備了一種與 CMOS 工藝完全兼容的超厚銅電感,并對(duì)其性能進(jìn)行了系統(tǒng)的測(cè)試研究。

1 工藝流程和工藝特性

1.1 工藝流程

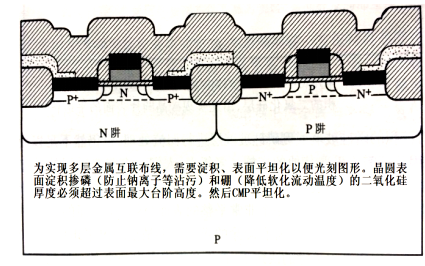

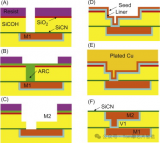

綜合考慮電感的大小、Q 值、可靠性、工藝的復(fù)雜性和兼容性等各方面的影響,我們采用厚絕緣襯底結(jié)構(gòu)。這種結(jié)構(gòu)的線圈雖然沒(méi)有犧牲層結(jié)構(gòu)的線圈性能突出,但由于厚絕緣層對(duì)襯底寄生效應(yīng)的削弱,同樣可以獲得性能較好的電感。采用離襯底較遠(yuǎn)的金屬層(Thick Top Metal,MTT)作電感,可以減少襯底和金屬層之間的電磁場(chǎng)耦合在襯底中引起的損耗。具體工藝方法是,采用銅單大馬士革工藝,按金屬層次劃分,主要包括 5 個(gè)工藝模塊:MTT、VT2、MT、VT1 和 Mx。

1.2 工藝特性

采用低電阻率且離襯底較遠(yuǎn)的厚銅金屬(Thick Top Metal,MTT)作電感。工藝上存在的技術(shù)難點(diǎn),主要包括超厚介質(zhì)膜的淀積和刻蝕、超厚銅的電鍍(ECP)和 CMP、抑制銅原子在硅和二氧化硅中的擴(kuò)散等問(wèn)題。本文采用 3.3 μm 的超厚金屬銅作片上螺旋電感,該超厚金屬 Cu 層設(shè)計(jì)規(guī)則最小金屬線寬/最小金屬間距為 2.5 μm /2 μm,最大金屬寬線寬 45 μm,其最為關(guān)鍵的工藝是超寬超厚線條的刻蝕和大面積銅的 CMP。

1.2.1 頂層金屬(MTT)刻蝕工藝

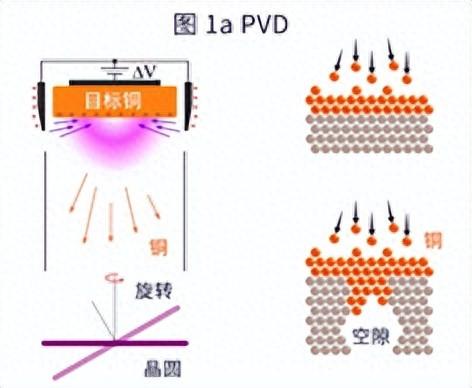

頂層金屬(MTT)的介質(zhì)膜采用等離子增強(qiáng)化學(xué)沉積(PECVD)TEOS 3.3 μm,光刻后采用 AMAT eMax 刻蝕設(shè)備刻蝕出不同線寬的圖形, 刻蝕氣體為C4F6。圖 1 是刻蝕后不同線寬的形貌圖,從圖中可以看出,刻蝕后線寬為 2.5 μm 和線寬為 15 μm 的 Trench 形貌完好,并且得到了均勻的 Trench 底部(Trench 底部過(guò)刻蝕量為 1 000 ~ 1 100 ?)。

1.2.2 頂層厚銅(MTT)的CMP工藝

由于不同的圖形(不同線寬及間距)在進(jìn)行 ECP工藝后的表面形貌不同,因此經(jīng)過(guò) CMP 后各圖形區(qū)域的金屬厚度和 Dishing 情況也存在不同,如表 1 所示。對(duì)于各種不同線寬的金屬厚度及 Dishing均在工藝規(guī)范內(nèi)。

圖 2 是經(jīng)過(guò) PVD、ECP 和 CMP 平坦化工藝后的 XSEM 圖。從圖可以看出,頂層金屬厚度大于 2.9 μm。同時(shí),設(shè)計(jì)值為 10 μm 的電感線圈,完成刻蝕以及 CMP 后頂部和底部線寬分別為 10.000 μm 和 9.743 μm。金屬線厚度和寬度均達(dá)到設(shè)計(jì)標(biāo)準(zhǔn)并且溝槽形貌良好,中心(a)和邊緣(b)差別不大,說(shuō)明刻蝕和 CMP 均勻性都很好。

2 電感性能結(jié)果與討論

2.1 WAT 測(cè)試

本文對(duì) 3.3 μm 金屬層 MTT(Thick Top Metal)Meander-Fork 結(jié)構(gòu)進(jìn)行了電學(xué)測(cè)試。線寬 2.5 μm、間距 2 μm、長(zhǎng) 0.2 m 的 Meander 方塊電阻如表 2 所示。

根據(jù)業(yè)內(nèi)標(biāo)準(zhǔn),金屬寬度/間距(W/S)為 2.5 μm / 2 μm 結(jié)構(gòu)的 Rs 為 5.21 mΩ/□,而本文 Rs 均值為5.6 mΩ/□,比業(yè)內(nèi)標(biāo)準(zhǔn)稍大,原因是 ECP 銅的晶粒較小,加上 ECP 后退火溫度較低,從而導(dǎo)致銅的電阻率稍微偏高。

圖 3 是 Meander-Fork 結(jié)構(gòu)(W/S=2.5 μm/2 μm,Length= 0.2 m)上的漏電測(cè)試結(jié)果,漏電流水平為 1×10-13 A 左右,在業(yè)內(nèi)標(biāo)準(zhǔn)規(guī)范內(nèi),工藝正常。

2.2 電感測(cè)試結(jié)果與分析

電感的測(cè)試系統(tǒng)由 E8363B 網(wǎng)絡(luò)分析儀和微波探針臺(tái)組成,該測(cè)試系統(tǒng)可以測(cè)試散射 S 參數(shù)。螺旋電感被安放在兩個(gè) GSG(ground-singal-ground)的探頭之間,測(cè)量時(shí)硅襯底通過(guò)測(cè)試夾從背面接地。利用公式將所測(cè)量的散射 S 參數(shù)轉(zhuǎn)化為導(dǎo)納 Y 參數(shù),再求得電感值和 Q 值。電感值主要受包括幾何參數(shù)(面積、形狀、寬度、間距、圈數(shù))和工藝參數(shù)(襯底電阻率、金屬電阻率、襯底和線圈距離)的影響。

本文通過(guò)對(duì) 2 層金屬進(jìn)行 RF 測(cè)試,對(duì)電感性能的 3 個(gè)主要參數(shù):品質(zhì)因子 Q、串聯(lián)電阻 Rs 以及串聯(lián)電感 L 進(jìn)行了初步的評(píng)估。對(duì)于單端電感的性能比較(頻率范圍 100 MHz~5 GHz),涉及的主要結(jié)構(gòu)參數(shù)有 Dout(電感外徑)、W(金屬寬度)、S(金屬間距)和 N(電感圈數(shù))。

2.2.1 不同電感圈數(shù)N的電感性能分析

圖4(a)是不同圈數(shù) N 的螺旋電感的 Q 值(Dout = 200 μm、W = 10 μm、S = 2 μm)。當(dāng)頻率 Freq 小于 1.0 GHz 時(shí),片上電感的輸入阻抗以感抗為主,6 條曲線 Q 值幾乎重合。此時(shí) N 增加對(duì) Q 值得影響可以忽略,且隨著頻率的升高,寄生電容的作用越來(lái)越大,Q 值漸漸增大。當(dāng)頻率 Freq 大于 1.5 GHz 時(shí) Q 值開(kāi)始下降,原因包括:(1)隨著圈數(shù) N 的增加,Din 變小,無(wú)論金屬線圈的損耗,還是襯底的損耗都增大[6]。(2)高頻時(shí),趨膚效應(yīng)變得顯著,圈數(shù)增加,導(dǎo)致串聯(lián)電阻 Rs 增加(如圖 4(b))。(3)圈數(shù)增加,也導(dǎo)致寄生電容的增加,從而引起電場(chǎng)能的峰值上升,導(dǎo)致 Q 值的減小。

圖 4(c)是不同線圈數(shù)下電感 L 值隨頻率變化趨勢(shì)圖,從圖中也可得知,電感圈數(shù)越大,其電感值 L 也相應(yīng)增大。

圖 4(d)是頻率在 1 GHz 時(shí),電感的品質(zhì)因子 Q 和電感值 L與圈數(shù) N 的關(guān)系曲線。當(dāng) N ≤ 4.5 時(shí),L 隨 N 增加而線性增大。N > 4.5 時(shí),L 變化趨緩,即增加 N,對(duì)電感值的影響變小。

綜上分析不同 N 對(duì) Q,L 的影響,可以得出當(dāng)芯片面積受限時(shí),電感圈數(shù)的增加對(duì)其低頻應(yīng)用影響不大。但頻率升高后,寄生電容的作用變大,且 N 增加對(duì) L 值貢獻(xiàn)越來(lái)越小,此時(shí)應(yīng)選用圈數(shù)較少的中空電感結(jié)構(gòu)。

2.2.2 不同金屬間距 S 的電感性能分析

圖 5 為不同電感間距 S 對(duì)傳統(tǒng)結(jié)構(gòu)電感值 L 和 Q 值的影響(Dout = 200 μm,W = 10 μm, N=3.5)。從圖 5 可以得知,從間距 2 μm 開(kāi)始,間距越小,其 Q 值越低,而電感值越大。這是由于減小間距,使得組成電感的金屬線圈間的寄生電容的增加,導(dǎo)致 Q 值的下降。間距的減小,導(dǎo)致組成電感的各部分線段互感增加,從而電感值增加。

2.2.3 不同金屬線寬 W 的電感性能分析

圖 6 為不同金屬線寬 W 對(duì)電感值 L 和 Q 值的影響(Dout = 200 μm,S = 2 μm,N = 3.5)。如圖 6(a)所示,當(dāng)金屬導(dǎo)體線寬變小時(shí),電感的品質(zhì)因子 Q 呈增大趨勢(shì)。Q 值在低頻段增加達(dá)到 11,隨即在高頻段降低,其原因是在外徑不變情況下,隨著寬度的增加,金屬橫截面積必然增大,從而使串聯(lián)電阻減小,Q 值增加。然而在較高頻段,由于趨膚效應(yīng)和鄰近效應(yīng),串聯(lián)電阻上升,從而導(dǎo)致 Q值下降。圖 6(b)中較窄線寬(W = 2 μm)的電感值較大,這是橫截面積較小的線圈產(chǎn)生較大的互感和外部磁通[7]。線寬的增加也會(huì)影響集成度,同時(shí)產(chǎn)生寄生電容,從而影響其工作頻率,增大電感和襯底耦合,導(dǎo)致 Q 值的下降。

3 結(jié)語(yǔ)

本文采用銅互連單大馬士革工藝,制備了超厚金屬銅集成電感。對(duì)超厚銅電感中關(guān)鍵工藝模塊進(jìn)行了開(kāi)發(fā),包括超厚介質(zhì)膜的淀積和刻蝕、超厚金屬 Cu 的電鍍和 CMP 工藝等,刻蝕后溝槽形貌良好,CMP 后金屬 Cu 的厚度和線寬均達(dá)到設(shè)計(jì)標(biāo)準(zhǔn)。對(duì)所制備的超厚金屬銅電感進(jìn)行電學(xué)測(cè)試結(jié)果表明:電感 Q 值最高可達(dá)到 11(頻率為 2.5 GHz)。在 1~3 GHz 范圍內(nèi),電感值較均勻。不同線圈圈數(shù),金屬線寬和金屬間距對(duì)超厚金屬 Cu 電感的電感值 L 和 Q 值均有不同影響。該方法研制的銅電感和 CMOS 集成電路工藝完全兼容,具有廣闊的應(yīng)用前景。

-

電鍍

+關(guān)注

關(guān)注

16文章

456瀏覽量

24126 -

RFIC

+關(guān)注

關(guān)注

1文章

60瀏覽量

24463 -

集成電路制造

+關(guān)注

關(guān)注

0文章

11瀏覽量

6938

原文標(biāo)題:一種單大馬士革結(jié)構(gòu)超厚銅集成電感

文章出處:【微信號(hào):appic-cn,微信公眾號(hào):集成電路應(yīng)用雜志】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

集成電路片內(nèi)銅互連技術(shù)的發(fā)展

12吋晶圓集成電路芯片制程工藝與工序后端BEOL的詳細(xì)資料說(shuō)明

實(shí)現(xiàn)3nm技術(shù)節(jié)點(diǎn)需要突破哪些半導(dǎo)體關(guān)鍵技術(shù)

提高銅互連優(yōu)勢(shì)的方法

什么是銅互連?為什么銅互連非要用雙大馬士革工藝?

半大馬士革集成中引入空氣間隙結(jié)構(gòu)面臨的挑戰(zhàn)

通過(guò)工藝建模進(jìn)行后段制程金屬方案分析

降低半導(dǎo)體金屬線電阻的沉積和刻蝕技術(shù)

半大馬士革工藝:利用空氣隙減少寄生電容

大馬士革銅互連工藝詳解

如何采用銅互連單大馬士革工藝制作超厚金屬銅集成電感的概述

如何采用銅互連單大馬士革工藝制作超厚金屬銅集成電感的概述

評(píng)論