聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603019 -

Xilinx

+關(guān)注

關(guān)注

71文章

2167瀏覽量

121313 -

PCIe

+關(guān)注

關(guān)注

15文章

1234瀏覽量

82590 -

ISE

+關(guān)注

關(guān)注

1文章

100瀏覽量

36524

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Verilog 測(cè)試平臺(tái)設(shè)計(jì)方法 Verilog FPGA開(kāi)發(fā)指南

Verilog測(cè)試平臺(tái)設(shè)計(jì)方法是Verilog FPGA開(kāi)發(fā)中的重要環(huán)節(jié),它用于驗(yàn)證Verilog設(shè)計(jì)的正確性和性能。以下是一個(gè)詳細(xì)的Verilog測(cè)試平臺(tái)設(shè)計(jì)方法及Verilog FPGA開(kāi)

【免費(fèi)分享】OpenHarmony鴻蒙物聯(lián)網(wǎng)開(kāi)發(fā)板資料包一網(wǎng)打盡,附教程/視頻/項(xiàng)目/源碼...

?想要深入學(xué)習(xí)鴻蒙設(shè)備開(kāi)發(fā)及鴻蒙物聯(lián)網(wǎng)開(kāi)發(fā)嗎?現(xiàn)在機(jī)會(huì)來(lái)了!我們?yōu)槌鯇W(xué)者們準(zhǔn)備了一份全面的資料包,包括原理圖、教程、視頻、項(xiàng)目、源碼等,所有資料全部免費(fèi)領(lǐng)取,課程

ALINX FPGA+GPU異架構(gòu)視頻圖像處理開(kāi)發(fā)平臺(tái)介紹

Alinx 最新發(fā)布的新品 Z19-M 是一款創(chuàng)新的 FPGA+GPU 異構(gòu)架構(gòu)視頻圖像處理開(kāi)發(fā)平臺(tái),它結(jié)合了 AMD Zynq UltraScale+ MPSoC(FPGA)與 NV

基于TI Sitara系列AM5728工業(yè)開(kāi)發(fā)板——FPGA視頻開(kāi)發(fā)案例分享

關(guān)鍵代碼(MicroBlaze) 11

1.4 Vivado工程說(shuō)明 16

1.5 模塊/IP核配置 20

前 言 本文主要介紹FPGA視頻開(kāi)發(fā)案例的使用說(shuō)明,適用開(kāi)發(fā)環(huán)境:W

發(fā)表于 07-12 17:24

FPGA | Xilinx ISE14.7 LVDS應(yīng)用

今天給大俠帶來(lái) Xilinx ISE14.7 LVDS應(yīng)用,話不多說(shuō),上貨。

最近項(xiàng)目需要用到差分信號(hào)傳輸,于是看了一下FPGA上差分信號(hào)的使用。Xilinx FPGA中,主要通過(guò)

發(fā)表于 06-13 16:28

fpga開(kāi)發(fā)是什么意思

FPGA開(kāi)發(fā)是指利用現(xiàn)場(chǎng)可編程邏輯門陣列(Field Programmable Gate Array,簡(jiǎn)稱FPGA)進(jìn)行硬件設(shè)計(jì)和實(shí)現(xiàn)的過(guò)程。FPGA是一種可編程的邏輯器件,它允許用戶

fpga仿真軟件有哪些

此外,還有一些其他的FPGA仿真軟件,如Gvim和ISE等,可以根據(jù)具體需求和開(kāi)發(fā)環(huán)境進(jìn)行選擇。需要注意的是,不同的FPGA仿真軟件可能具有不同的特點(diǎn)和優(yōu)勢(shì),

fpga開(kāi)發(fā)板是什么?fpga開(kāi)發(fā)板有哪些?

FPGA開(kāi)發(fā)板是一種基于FPGA(現(xiàn)場(chǎng)可編程門陣列)技術(shù)的開(kāi)發(fā)平臺(tái),它允許工程師通過(guò)編程來(lái)定義和配置FPGA芯片上的邏輯電路,以實(shí)現(xiàn)各種數(shù)字

項(xiàng)目分享|基于ELF 1開(kāi)發(fā)板的遠(yuǎn)程監(jiān)測(cè)及人臉識(shí)別項(xiàng)目

今天非常榮幸地向各位小伙伴分享一個(gè)由共創(chuàng)社成員完成的遠(yuǎn)程監(jiān)測(cè)及人臉識(shí)別項(xiàng)目,該項(xiàng)目依托ELF1開(kāi)發(fā)板為核心硬件平臺(tái),構(gòu)建了一套完整的視頻監(jiān)控

【youyeetoo X1 windows 開(kāi)發(fā)板體驗(yàn)】基于ROS開(kāi)發(fā)的LIO系統(tǒng)——項(xiàng)目計(jì)劃+前言開(kāi)箱

其后方應(yīng)用以及算法的輸出是不會(huì)受任何影響的;

接下來(lái),閱讀官方文檔,以及提供的教程,來(lái)快速熟悉開(kāi)發(fā)板,期待這塊開(kāi)發(fā)板后面的表現(xiàn),也期待后面的項(xiàng)目的展示;

項(xiàng)目相關(guān)

避免廣告嫌疑,

發(fā)表于 01-26 17:58

在ELF 1 開(kāi)發(fā)板上實(shí)現(xiàn)讀取攝像頭視頻進(jìn)行目標(biāo)檢測(cè)

深度學(xué)習(xí)模型的項(xiàng)目,該項(xiàng)目能夠?qū)崟r(shí)讀取攝像頭視頻流并實(shí)現(xiàn)對(duì)畫面中的物體進(jìn)行精準(zhǔn)的目標(biāo)檢測(cè)。項(xiàng)目所需的硬件設(shè)備:1、基于NXP(恩智浦)i.M

AMD亮相ISE 2024:推進(jìn)沉浸式、自適應(yīng)與智能音視頻

在 ISE 2024 上,AMD 與我們的合作伙伴將展示了前沿的音頻和視頻處理、領(lǐng)先的 AV-over-IP 標(biāo)準(zhǔn)(IPMX、NDI 和 Dante AV Ultra)、機(jī)器學(xué)習(xí)應(yīng)用以及基于 FPGA 的先進(jìn) SoC 平臺(tái)上的全

FPGA? 開(kāi)搞!

。

該工具鏈?zhǔn)褂?Yosys 和 OpenFPGALoader 等開(kāi)源工具,并與 Cologne Chip 合作開(kāi)發(fā)實(shí)施和比特流生成工具。在設(shè)計(jì)輸入方面,工程師可以使用 Verilog、VHDL(通過(guò)

發(fā)表于 01-11 00:52

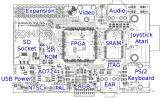

關(guān)于FPGA的開(kāi)源項(xiàng)目介紹

Hello,大家好,之前給大家分享了大約一百多個(gè)關(guān)于FPGA的開(kāi)源項(xiàng)目,涉及PCIe、網(wǎng)絡(luò)、RISC-V、視頻編碼等等,這次給大家?guī)?lái)的是不枯燥的娛樂(lè)項(xiàng)目,主要偏向老的游戲內(nèi)核使用

高速視頻采集卡設(shè)計(jì)方案:620-基于PCIe的高速視頻采集卡

實(shí)驗(yàn)室數(shù)據(jù)采集 , FPGA邏輯視頻采集 , 高速視頻采集卡 , PCIe視頻采集卡 , 視頻程序開(kāi)發(fā)

演示如何使用ISE開(kāi)發(fā)FPGA項(xiàng)目(1)視頻教程

演示如何使用ISE開(kāi)發(fā)FPGA項(xiàng)目(1)視頻教程

評(píng)論