眾籌首發(fā)|龍哥手把手教你從零入門LabVIEW機(jī)器視覺!

日前,在NIWEEK2018上,NI共同創(chuàng)始人、Fellow、有著LabVIEW之父稱號(hào)的Jeff Kodosky做了主題演講,他暢談了未來LabVIEW的軟件架構(gòu)。

未來,LabVIEW將可通過更高級(jí)的抽象,實(shí)現(xiàn)在一個(gè)程序框架中對(duì)上位機(jī)和FPGA同時(shí)編程,雙方的數(shù)據(jù)交互在統(tǒng)一平臺(tái)下執(zhí)行,而不像過去通過隊(duì)列形式實(shí)現(xiàn)。這會(huì)給編程帶來更大的便利性,尤其是面對(duì)復(fù)雜系統(tǒng),采用更高級(jí)的編程語言可加速用戶的開發(fā)周期。

“就好像開車一樣,如果你需要加速,采用自動(dòng)變速箱直接踩油門的方式比手動(dòng)換擋便捷很多,這就是通過提高抽象級(jí)別讓軟件變得更加簡(jiǎn)單高效。”Jeff說道。

NI共同創(chuàng)始人、Fellow、LabVIEW之父Jeff Kodosky

以下是其演講內(nèi)容。

LabVIEW設(shè)計(jì)初衷只是為科學(xué)家和工程師可以快速完成他們的測(cè)試測(cè)量系統(tǒng),而無需專門的程序員團(tuán)隊(duì)。

正如Dr.T說過的,像電子表格程序可幫助金融分析師編程一樣,我們給工程師和科學(xué)家開發(fā)一套屬于他們自己的加速編程工具。

目前來看,LabVIEW已經(jīng)成功地完成了這一任務(wù)。

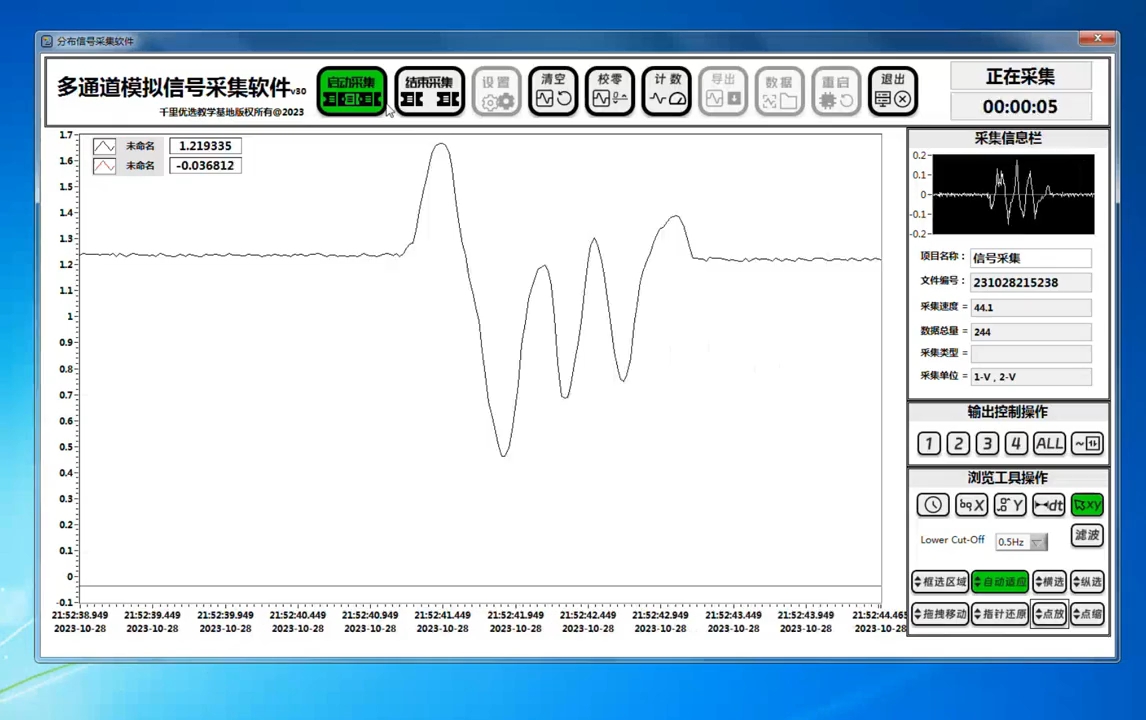

通過LabVIEW,數(shù)以萬計(jì)的工程師、科學(xué)家、測(cè)試人員甚至醫(yī)學(xué)研究員等各行業(yè)專家成功完成了他們的自動(dòng)測(cè)試系統(tǒng)。LabVIEW加速了研究開發(fā),減少了測(cè)試時(shí)間和成本,同時(shí)就減少了產(chǎn)品開發(fā)周期。

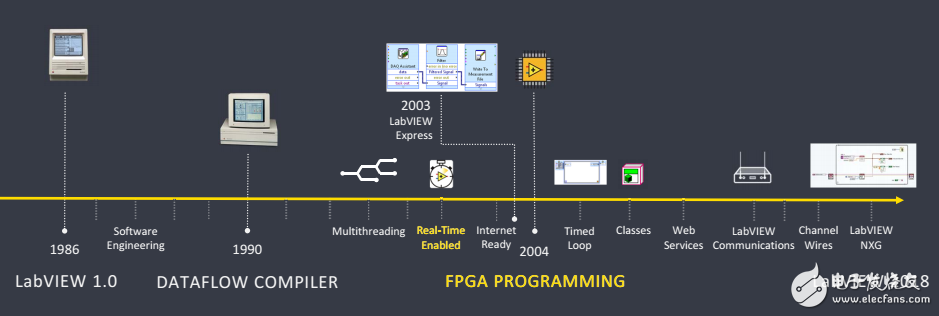

LabVIEW在持續(xù)改進(jìn)和創(chuàng)新上有著悠久歷史,每個(gè)版本既保持向后兼容性,同時(shí)也在不斷引入新功能。

LabVIEW最顯著的進(jìn)展是引入對(duì)實(shí)時(shí)系統(tǒng)和FPGA支持。用戶無需成為VHDL專家,便可通過構(gòu)建在FPGA上運(yùn)行的圖形化程序來滿足性能要求。今天,隨著系統(tǒng)的復(fù)雜性不斷增加,需要更多的并行處理,更多的物理I/O,更緊密的時(shí)序和同步以及更多的分布式組件。

LabVIEW演進(jìn)歷史

所以,我們將如何繼續(xù)應(yīng)對(duì)未來的復(fù)雜性呢?

一種方法是建立良好的策略和流程,保持測(cè)試套件和文檔的全流程管理。現(xiàn)有的軟件工程方式已成功構(gòu)建了大型測(cè)試系統(tǒng)。

另外軟件架構(gòu)同樣可以通過組織和限制設(shè)計(jì)遵循幫助認(rèn)證過的Patterns,例如,LabVIEW中的Project templates和Actor Framework就是這種方法。

當(dāng)然,工具和開發(fā)環(huán)境的改進(jìn)也有幫助。例如,通過LabVIEW NXG與DAQmx驅(qū)動(dòng)程序和DAQ硬件的集成更加緊密,使交互式探索和自動(dòng)化測(cè)量變得更加容易。

此外,專用工具可以通過減少定制開發(fā)的需求來處理整體流程的復(fù)雜性。像TestStand這樣的專用工具可以處理應(yīng)用程序的標(biāo)準(zhǔn)部分,而只開發(fā)您需要的自定義測(cè)試步驟。

通過NI提供的專用工具,加速軟件開發(fā)和實(shí)施周期

第二種方法則是提高我們用于設(shè)計(jì)系統(tǒng)的抽象級(jí)別。對(duì)于目前復(fù)雜的系統(tǒng),我們可以利用人工智能等方式提高抽象級(jí)別,可以減少人為的復(fù)雜性。想象一下你的車,如果您想要加速,使用自動(dòng)變速箱等更高級(jí)別的抽象比標(biāo)準(zhǔn)變速箱更簡(jiǎn)單,因?yàn)闃?biāo)準(zhǔn)變速箱還需要額外的手腳配合進(jìn)行離合換擋。

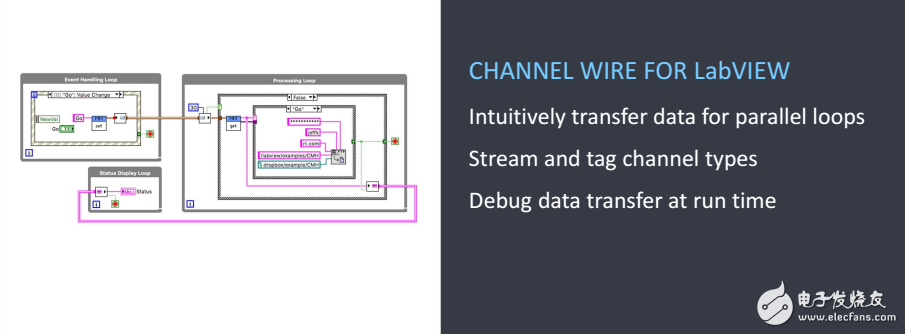

兩年前,我們?cè)贚abVIEW中引入了Channel Wire,提高了通信并行處理設(shè)計(jì)的抽象級(jí)別。相比低級(jí)語言設(shè)計(jì)起來更容易,更明顯也更易于理解。實(shí)際上還有更多的工作可以進(jìn)一步提高LabVIEW的抽象級(jí)別。

采用Channel Wire,上位機(jī)與FPGA之間的通信只需要簡(jiǎn)單的連線即可實(shí)現(xiàn)

從歷史上看,我們的開發(fā)理念都是首先著眼于使難題成為可能,然后再讓它們變得更容易。

NI已經(jīng)創(chuàng)建了跨越處理器和FPGA的測(cè)量應(yīng)用程序,現(xiàn)在是時(shí)候考慮提高抽象級(jí)別以增加便捷性了。

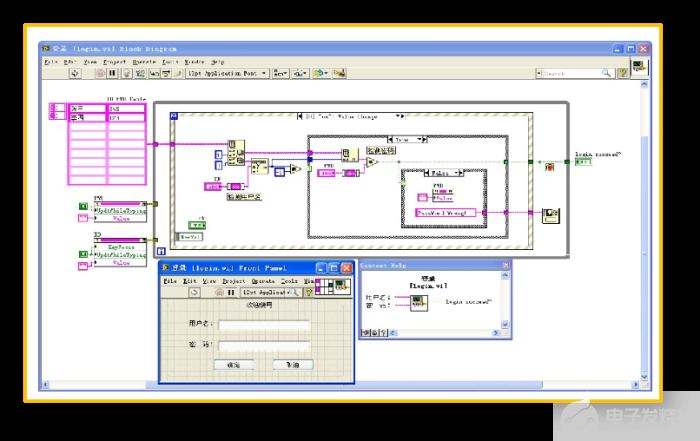

假設(shè)我們可以在LabVIEW中將FPGA表示為一個(gè)盒子。內(nèi)部的圖表代表部署到FPGA中,外部的圖表表示在處理器上運(yùn)行。它們之間的通道表示通信路徑,編譯器使用底層的FIFO和DMA資源來實(shí)現(xiàn)連接。

Target軟件體系結(jié)構(gòu)對(duì)于簡(jiǎn)化cRIO應(yīng)用和FlexRIO點(diǎn)對(duì)點(diǎn)通信應(yīng)用程序,甚至對(duì)于分布式應(yīng)用程序來說顯示出巨大的前景。

這是我們?yōu)樘岣叱橄蠹?jí)別而進(jìn)行的一個(gè)例子,如果我們能夠真正實(shí)現(xiàn)它,它將成為最先進(jìn)的技術(shù)進(jìn)步。

如圖所示,未來可在一個(gè)軟件系統(tǒng)開發(fā)框架內(nèi),實(shí)現(xiàn)上位機(jī)與FPGA的共同開發(fā)

讓我來嘗試描述我們一項(xiàng)正在進(jìn)行的研究工作,它可以通過更加模糊且更高級(jí)的處理方式加速我們的設(shè)計(jì)流程。以一個(gè)麥克風(fēng)測(cè)量系統(tǒng)來舉例。

最開始,我們勾勒出設(shè)計(jì)理念,包括展示要測(cè)試的麥克風(fēng),提供激勵(lì)信號(hào)的揚(yáng)聲器,驅(qū)動(dòng)揚(yáng)聲器的波形發(fā)生器,測(cè)量響應(yīng)信號(hào)的數(shù)字化儀器以及設(shè)置增益與頻率。

這種草圖經(jīng)常需要改進(jìn),例如,當(dāng)我們?yōu)榱双@得更高的精準(zhǔn)性,需要測(cè)量激勵(lì)信號(hào)。

如果我們可以在LabVIEW中放置一個(gè)抽象設(shè)計(jì)節(jié)點(diǎn)并編輯它的圖標(biāo)來表示麥克風(fēng),用另一個(gè)圖標(biāo)來表示揚(yáng)聲器,為聲波添加一些剪貼畫,我們可以快速生成一個(gè)草圖。

作為項(xiàng)目的一部分,它需要一些文檔,但同樣提高系統(tǒng)層級(jí)的話,我們就可以把它當(dāng)做實(shí)施整個(gè)系統(tǒng)的啟動(dòng)點(diǎn)。

如果我們可以注釋導(dǎo)線以顯示激勵(lì)信號(hào),作為連續(xù)步進(jìn)頻率波形,并且對(duì)采集輸出進(jìn)行注釋以顯示要分析的波形流,這將使抽象算法更為清晰。

我們還可以顯示將采集到的信號(hào)流分成時(shí)間間隔信息。

我們可以標(biāo)記這個(gè)抽象級(jí)別,并通過將生成節(jié)點(diǎn)擴(kuò)展為波形計(jì)算和波形輸出來繼續(xù)改進(jìn)設(shè)計(jì)。

并將采集節(jié)點(diǎn)擴(kuò)展為模擬輸入,將節(jié)點(diǎn)分割成塊。

現(xiàn)在我們意識(shí)到,只有當(dāng)我們有相同的時(shí)間參考時(shí),這才會(huì)起作用,因此我們引入了一個(gè)開始時(shí)間,于是開始生成和采集同步。

在這一點(diǎn)上,我們發(fā)現(xiàn)我們忽略了一個(gè)重要問題。由于聲傳播,來自麥克風(fēng)的信號(hào)將比刺激信號(hào)顯著延遲。于是我們決定通過在波形的開始處生成一個(gè)特殊的脈沖并使用它來同步采集的信號(hào)來解決這個(gè)問題。

當(dāng)我們語義縮放到更高級(jí)別的抽象添加測(cè)試項(xiàng)時(shí),我們看到一條線,顯示共同開始時(shí)間。

我們認(rèn)為它足夠重要,可以在此級(jí)別展示,因此我們可以實(shí)現(xiàn)這一目標(biāo)。然后,我們添加連接以傳遞同步脈沖,并設(shè)置為在波形開始處顯示。這時(shí)又會(huì)看到需要實(shí)施的新連接。

我們繼續(xù)完善波形輸出節(jié)點(diǎn),并展示如何將同步脈沖發(fā)送到采集點(diǎn)上。

接下來可以改進(jìn)該節(jié)點(diǎn)以顯示同步脈沖被重新采樣并用于匹配采集的信號(hào)的同步。我們繼續(xù)以這種方式工作,一直到一個(gè)工作應(yīng)用程序完成,不斷進(jìn)行縮放,在一個(gè)層面上編輯并在其他層面上進(jìn)行配合修正,以符合一致性。

最終只通過一個(gè)開發(fā)軟件,便可實(shí)現(xiàn)測(cè)試系統(tǒng)的搭建

這種豐富的設(shè)計(jì)環(huán)境將使用戶能夠創(chuàng)建易于理解和維護(hù)的系統(tǒng)。

在多個(gè)抽象層次上工作是解決復(fù)雜性的最有效方法,它可以逐步公開和抽象語義細(xì)節(jié),以便您可以更好地設(shè)計(jì)測(cè)量系統(tǒng),并根據(jù)需求不斷演變。

正如Alan Kay所說,“預(yù)測(cè)未來的最好方法就是創(chuàng)造未來。”

我們構(gòu)建的環(huán)境變得越來越復(fù)雜,這需要更復(fù)雜的測(cè)試和測(cè)量系統(tǒng)與之匹配。需要更復(fù)雜的工具來減少人為造成的復(fù)雜性并可提供更高級(jí)的抽象層設(shè)計(jì)。通過我們對(duì)產(chǎn)品的不斷改進(jìn),將進(jìn)一步實(shí)現(xiàn)這一愿景。

我們希望提供不斷創(chuàng)新的工具,構(gòu)建未來所需的系統(tǒng),NI的愿景一直都是如此。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603012 -

LabVIEW

+關(guān)注

關(guān)注

1970文章

3654瀏覽量

323331

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

LabVIEW下CASSY軟件的實(shí)現(xiàn).

基于LabVIEW_DSC的監(jiān)控軟件通用架構(gòu)_于獻(xiàn)榕

一文詳解LabVIEW RIO架構(gòu)

LabVIEW之父歷史回顧編程理念,這將對(duì)未來造成怎樣的影響

LABVIEW軟件應(yīng)用與前景介紹

看LabVIEW之父談?wù)撐磥鞮abVIEW的軟件架構(gòu)

看LabVIEW之父談?wù)撐磥鞮abVIEW的軟件架構(gòu)

評(píng)論