MCU工程師須知的FPGA硬件屬性

簡單的FPGA構(gòu)造

在集成電路領(lǐng)域人們經(jīng)常會聽到構(gòu)造(fabric)這個術(shù)語,它指的是FPGA器件的底層基礎(chǔ)結(jié)構(gòu)。(作為一個興趣點,單詞“構(gòu)造”來自中世紀英語fabryke,意思是“建造的某些東西”)。下面讓我們從FPGA中的內(nèi)核可編程構(gòu)造開始吧……

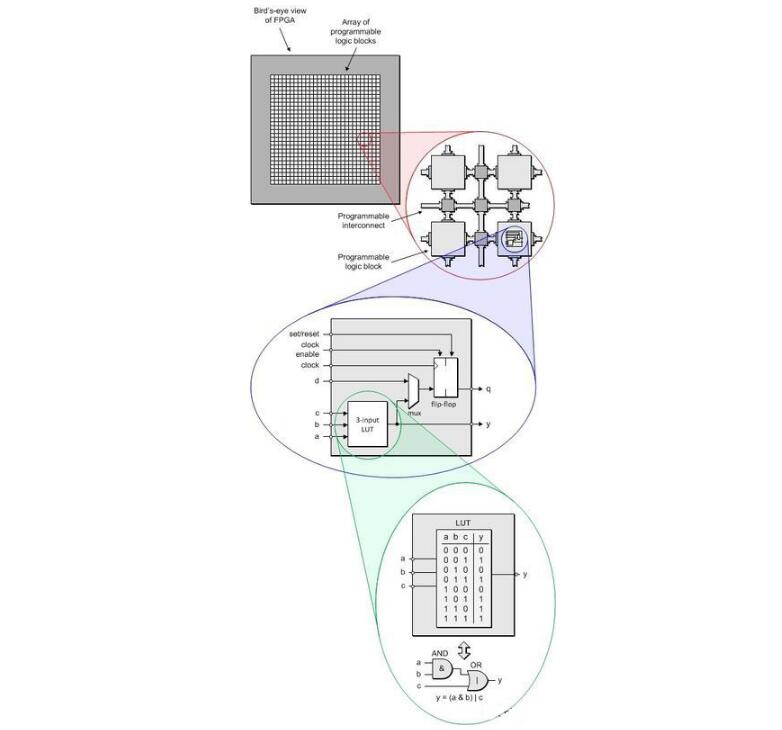

如果我們仔細觀察FPGA封裝的內(nèi)部,我們將看到硅片(技術(shù)術(shù)語裸片)。可編程構(gòu)造表現(xiàn)為可編程邏輯塊陣列,如下圖所示。如果我們用放大鏡“放大查看”,我們可以看到這種構(gòu)造由沉浸于可編程互連“海洋”中的許多邏輯“島”(可編程邏輯塊)組成。

圖1:簡單的FPGA構(gòu)造

基本FPGA可編程構(gòu)造的一般性表示。是啊,我確實是用自己的雙手親自創(chuàng)作的這幅圖片,我因此感到非常自豪呢,非常感謝你加以關(guān)注。如果我們進一步放大,我們可以看到,每個可編程模塊都包含有許多數(shù)字功能。在這個例子中,我們可以見到一個三輸入的查找表(LUT)、一個復(fù)用器和一個觸發(fā)器,但重要的是我們要認識到,這些功能的數(shù)量和類型對不同系列的FPGA來說是會變化的。

觸發(fā)器可以被配置(編程)為寄存器或鎖存器;復(fù)用器可以被配置為選擇一個到邏輯塊的輸入或LUT的輸出;LUT可以被配置為代表任何所要求的邏輯功能。

更詳細地了解LUT:

上面所示的簡單例子包含一個三輸入的查找表(LUT)。在實際應(yīng)用中,即使最簡單的FPGA都會使用四輸入LUT,而一些更大更復(fù)雜的器件甚至會宣稱使用六、七或八輸入的LUT,但為了簡單起見,我們還是討論三輸入版本。

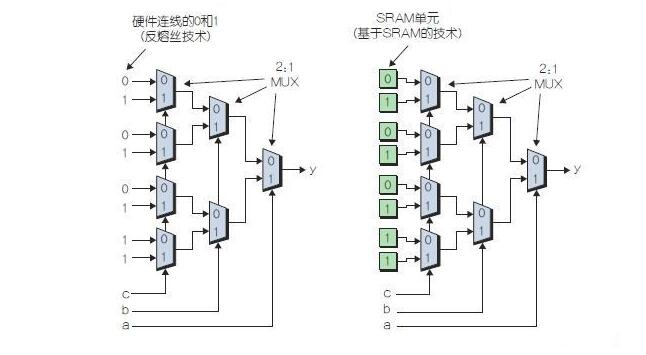

我們會在以后的文章中討論各種類型的FPGA實現(xiàn)技術(shù)。現(xiàn)在我們只需要知道,F(xiàn)PGA內(nèi)部的可編程單元可以用反熔絲、閃存單元或SRAM內(nèi)存單元來實現(xiàn)。先讓我們看一個用反熔絲技術(shù)創(chuàng)建的FPGA吧。這是一種一次性可編程(OTP)技術(shù),這意味著一旦你編程了這個FPGA,它將永遠保持這個狀態(tài)而不再改變。

形象化介紹這種技術(shù)的最簡單方法是用下圖所示級聯(lián)的2:1復(fù)用器(MUX)。對基于反熔絲技術(shù)的FPGA來說,編程器件相當于通過“硬件連線”將第一組復(fù)用器的輸入連接到實現(xiàn)目標邏輯功能所需的正確0或1值。下圖中所示的值反映的實際結(jié)果是,我們使用這個LUT實現(xiàn)了前面那張圖隱含的公式y(tǒng)=(a & b)|c。在實際應(yīng)用中,復(fù)用器可以用場效應(yīng)管的分支“樹”來實現(xiàn),但我們在這里真的不用擔心最底層的實現(xiàn)細節(jié)。

圖2:輸入值經(jīng)“硬件連接的”反熔絲型LUT(左),輸入從SRAM單元饋入的SRAM型LUT(右)

另外一種非常常見的FPGA實現(xiàn)技術(shù)是使用SRAM配置單元。同樣,我們會在以后的文章中討論更多的細節(jié)。這里我們所要知道的僅是當電路板第一次上電時,基于SRAM的FPGA會加載配置信息(我們可以把這個過程想像為器件的編程)。作為這種配置的一部分,用作LUT復(fù)用器輸入的SRAM單元會被加載進上圖所示的目標0或1值。

我沒有顯示0和1被加載進SRAM單元的那種機制,因為我不想讓問題變得復(fù)雜。出于這次討論的目的,我們真的無需擔心這種“魔術(shù)”是如何發(fā)生的。我在這里唯一要提的事(給你考慮的空間)是—使用一種被稱為部分再配置的技術(shù)—FPGA的一部分可以發(fā)起對另一部分進行再配置(當然反過來也行)。對于具有微控制器和/或軟件背景的讀者來說,我們可以將這種技術(shù)想象為相當于自我修改代碼的硬件。這意味著這種技術(shù)是非常非常強大的,但也會帶來很難隔離和調(diào)試的問題。

通用的輸入和輸出

FPGA器件還包含有通用的輸入/輸出(GPIO)引腳和焊盤(圖1中沒有顯示)。通過配置單元,F(xiàn)PGA器件內(nèi)的互連部分可以被編程為這樣:將器件的主輸入連接到一個或多個可編程邏輯塊的輸入。任何邏輯塊的輸出也可以用來驅(qū)動任何其它邏輯塊的輸入和/或FPGA器件的主輸出。另外,GPIO引腳可以被配置為支持種類廣泛的I/O標準,包括電壓、終端阻抗、擺率等。

世界上第一塊FPGA與本文中討論的架構(gòu)非常類似。這塊FPGA就是賽靈思公司在1985年推出的XC2064(是用2um工藝節(jié)點制造的),它包含有8×8=64的邏輯塊陣列,每個邏輯塊包含一個四輸入LUT和其它一些簡單功能。從那以后,F(xiàn)PGA發(fā)展勢不可擋,正像我們看到的那樣……

復(fù)雜的FPGA架構(gòu)

正如我們在前面說的那樣,賽靈思公司在1985年推出的第一塊FPGA—XC2064包含8×8=64的邏輯塊陣列,每個邏輯塊包含一個四輸入查找表及其它一些簡單功能。由于它們的容量非常有限,因此早期的FPGA只用來執(zhí)行一些相對簡單的任務(wù),比如集中一些膠合邏輯,或?qū)崿F(xiàn)基本的狀態(tài)機。然而隨著時間的推移,事情開始改變……

隨著時間的推移和工藝節(jié)點的進步,F(xiàn)PGA的容量和性能不斷得到提高,功耗卻不斷的下降。直到大約2006年以前廣泛使用的一直是四輸入查找表。事實上,在寫這篇文章之時,較小的FPGA系列器件仍在使用四輸入的查找表,但一些高端器件可能使用六、七或八輸入的查找表。這些大家伙可能被用作一個大的查找表,或分裂成許多更小的功能,比如兩個四輸入的查找表或一個三輸入一個五輸入的查找表。在實際的高端器件中,這種可編程構(gòu)造可以描述相當于百萬級(有時甚至千萬級)的原始邏輯門。

如果某個邏輯功能(比方說計數(shù)器)是用FPGA的可編程構(gòu)造實現(xiàn)的,那么這個功能可以被說成“軟功能”。相比之下,如果某個功能是直接用芯片實現(xiàn)的,則被說成“硬功能”。(隨著這些功能變得越來越大越來越復(fù)雜,我們一般稱它們?yōu)閮?nèi)核)。軟內(nèi)核的優(yōu)勢在于,你可以讓它們做你想讓它們做的任何事。硬內(nèi)核的優(yōu)勢是它們占用較少的硅片面積,具有較高的性能,并且功耗較低。最優(yōu)的解決方案是混合使用軟內(nèi)核(用可編程構(gòu)造實現(xiàn))和硬內(nèi)核(直接用硅片實現(xiàn))。這樣,除了基于查找表的可編程構(gòu)造外,今天的FPGA可以利用以下介紹的各種硬內(nèi)核進行性能增強:

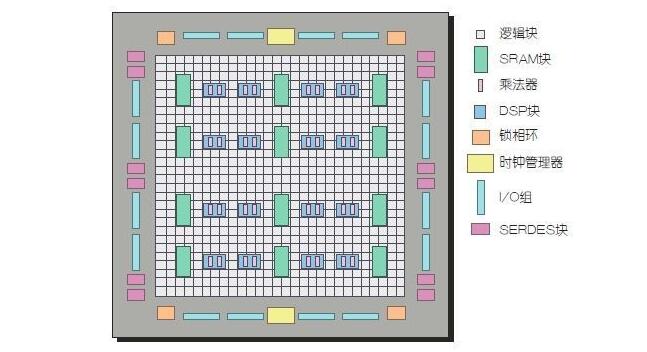

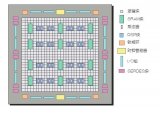

圖3:更復(fù)雜的FPGA架構(gòu)

舉例來說,該器件可能包含數(shù)千個加法器、乘法器和數(shù)字信號處理(DSP)功能;數(shù)兆位的片上內(nèi)存,大量的高速串行互連(SERDES)收發(fā)器模塊,以及眾多的其它功能。

帶嵌入式處理器的FPGA

這是真正讓人興奮的事情……你可以用FPGA中的普通可編程構(gòu)造做的事情之一是,使用其中的一部分實現(xiàn)一個或多個軟處理器內(nèi)核。當然,你可以實現(xiàn)不同規(guī)模的處理器。舉例來說,你可以創(chuàng)建一個或多個8位的處理器,加上一個或多個16位或32位的軟處理器—所有處理器都在同一器件中。

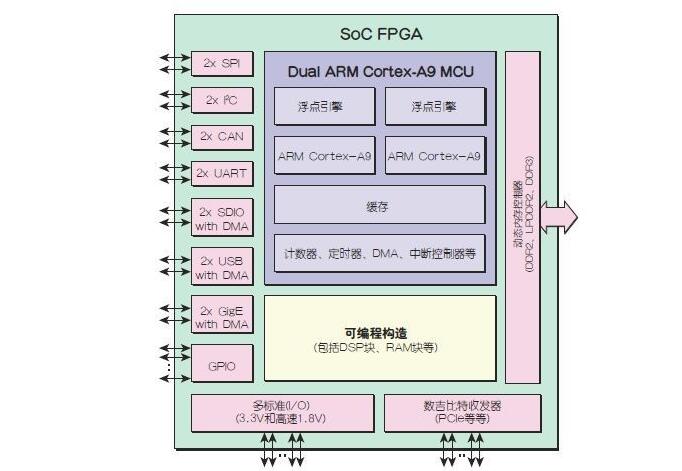

如果FPGA供應(yīng)商希望提供一個占用較少硅片面積、消耗較低功率但性能更高的處理器,解決方案是將它實現(xiàn)為硬內(nèi)核。一個非常令人興奮的開發(fā)成果是Altera和賽靈思等公司最近推出的SoC FPGA。考慮下面所示這個例子:

圖4:一種新的SoC FPGA

這個漂亮的小東西整合了一個完全以硬內(nèi)核方式實現(xiàn)的雙路ARM Cortex-A9微控制器子系統(tǒng)(運行時鐘高達1GHz,包含浮點引擎,片上緩存,計數(shù)器,定時器等),以及種類廣泛的硬內(nèi)核接口功能(SPI,I2C,CAN等),還有一個硬內(nèi)核的動態(tài)內(nèi)存控制器,所有這些組件都利用大量傳統(tǒng)的可編程構(gòu)造和大量的通用輸入輸出(GPIO)引腳進行了性能增強。(即將在16nm節(jié)點推出的一款SoC FPGA據(jù)稱包含四內(nèi)核的64位ARM Cortex-A53處理器,雙內(nèi)核32位ARM Cortex-R5實時處理器,以及一個ARM Mali-400MP圖形處理器。這些可不是你祖母時候的FPGA哦!)

傳統(tǒng)的嵌入式系統(tǒng)架構(gòu)師可能將其中一個器件放置在電路板上,并將它用作傳統(tǒng)的高性能雙內(nèi)核ARM Cortex-A9微控制器。當電路板上電時,硬微控制器內(nèi)核立即啟動,并在任何可編程構(gòu)造完成配置之前就可用了。這樣可以節(jié)省時間和精力,并讓軟件開發(fā)人員和硬件設(shè)計師同時開始開發(fā)。

一種情形是軟件開發(fā)人員捕獲他們的代碼,在SoC FPGA的Cortex-A9處理器上運行這些代碼,然后通過分析識別任何可能嚴重影響性能并成為瓶頸的功能。這些功能隨后可能就轉(zhuǎn)交給硬件設(shè)計工程師用可編程構(gòu)造來實現(xiàn),它們(這些功能,不是設(shè)計工程師)將使用較低的時鐘頻率提供明顯更高的性能,而且功耗更低。

前面我們說過,硬內(nèi)核實現(xiàn)的功能(圖4所示的ARM Cortex-A9就是一種硬內(nèi)核)與等效的軟內(nèi)核相比具有更高的性能和更低的功耗。但現(xiàn)在我們又說如果在硬內(nèi)核處理器上運行的軟件功能是個瓶頸,我們可以用可編程構(gòu)造來實現(xiàn),這樣它就能……你理解的沒錯,提供更高的性能和更低的功耗。

FPGA開發(fā)流程

原理圖和HDL(Hardwaredescriptionlanguage,硬件描述語言)是兩種最常用的數(shù)字硬件電路描述方法,其中HDL設(shè)計法具有更好的可移植性、通用性和模塊劃分與重用性的特點,在目前的工程設(shè)計中被廣泛使用,下面對FPGA設(shè)計熟悉電路時的開發(fā)流程是基于HDL的。

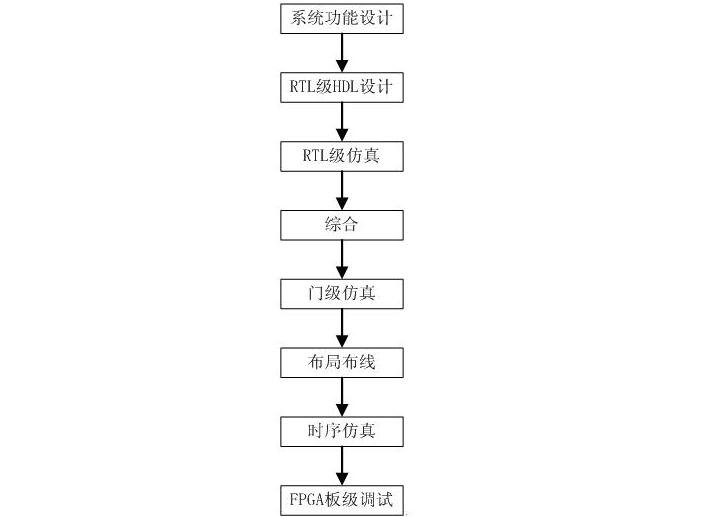

圖6FPGA的開發(fā)流程

1)系統(tǒng)功能設(shè)計

在系統(tǒng)設(shè)計之前,首先要進行的是方案論證、系統(tǒng)設(shè)計和FPGA芯片選擇等準備工作。系統(tǒng)工程師根據(jù)任務(wù)要求,如系統(tǒng)的指標和復(fù)雜度,對工作速度和芯片本身的各種資源、成本等方面進行權(quán)衡,選擇合理的設(shè)計方案和合適的器件類型。一般都采用自頂向下的設(shè)計方法,把系統(tǒng)分成若干個基本單元,然后再把每個基本單元劃分為下一層次的基本單元,一直這樣做下去,直到可以直接使用EDA元件庫為止。

2)RTL級HDL設(shè)計

RTL級(RegisterTransferLevel,寄存器傳輸級)指不關(guān)注寄存器和組合邏輯的細節(jié)(如使用了多少個邏輯門、邏輯門的連接拓撲結(jié)構(gòu)等),通過描述數(shù)據(jù)在寄存器之間的流動和如何處理、控制這些數(shù)據(jù)流動的模型的HDL設(shè)計方法。RTL級比門級更抽象,同時也更簡單和高效。RTL級的最大特點是可以直接用綜合工具將其綜合成為門級網(wǎng)表,其中RTL級設(shè)計直接決定著系統(tǒng)的功能和效率。

3)RTL級仿真

也稱為功能(行為)仿真,或是綜合前仿真,是在編譯之前對用戶所設(shè)計的電路進行邏輯功能驗證,此時的仿真沒有延遲信息,僅對初步的功能進行檢測。仿真前,要先利用波形編輯器和HDL等建立波形文件和測試向量(即將所關(guān)心的輸入信號組合成序列),仿真結(jié)果將會生成報告文件和輸出信號波形,從中便可以觀察各個節(jié)點信號的變化。如果發(fā)現(xiàn)錯誤,則返回設(shè)計修改邏輯設(shè)計。常用的工具有ModelTech公司的ModelSim、Sysnopsys公司的VCS和Cadence公司的NC-Verilog以及NC-VHDL等軟件。雖然功能仿真不是FPGA開發(fā)過程中的必需步驟,但卻是系統(tǒng)設(shè)計中最關(guān)鍵的一步。

為了提高功能仿真的效率,需要建立測試平臺testbench,其測試激勵一般使用行為級HDL語言描述,其中RTL級模塊是可綜合的,它是行為級模塊的一個子集合。

4)綜合

所謂綜合就是將較高級抽象層次的描述轉(zhuǎn)化成較低層次的描述。綜合優(yōu)化根據(jù)目標與要求優(yōu)化所生成的邏輯連接,使層次設(shè)計平面化,供FPGA布局布線軟件進行實現(xiàn)。就目前的層次來看,綜合優(yōu)化(Synthesis)是指將設(shè)計輸入編譯成由與門、或門、非門、RAM、觸發(fā)器等基本邏輯單元組成的邏輯連接網(wǎng)表,而并非真實的門級電路。真實具體的門級電路需要利用FPGA制造商的布局布線功能,根據(jù)綜合后生成的標準門級結(jié)構(gòu)網(wǎng)表來產(chǎn)生。為了能轉(zhuǎn)換成標準的門級結(jié)構(gòu)網(wǎng)表,HDL程序的編寫必須符合特定綜合器所要求的風格。由于門級結(jié)構(gòu)、RTL級的HDL程序的綜合是很成熟的技術(shù),所有的綜合器都可以支持到這一級別的綜合。常用的綜合工具有Synplicity公司的Synplify/SynplifyPro軟件以及各個FPGA廠家自己推出的綜合開發(fā)工具。

5)門級仿真

也稱為綜合后仿真,綜合后仿真檢查綜合結(jié)果是否和原設(shè)計一致。在仿真時,把綜合生成的標準延時文件反標注到綜合仿真模型中去,可估計門延時帶來的影響。但這一步驟不能估計線延時,因此和布線后的實際情況還有一定的差距,并不十分準確。目前的綜合工具較為成熟,對于一般的設(shè)計可以省略這一步,但如果在布局布線后發(fā)現(xiàn)電路結(jié)構(gòu)和設(shè)計意圖不符,則需要回溯到綜合后仿真來確認問題之所在。在功能仿真中介紹的軟件工具一般都支持綜合后仿真。

6)布局布線

實現(xiàn)是將綜合生成的邏輯網(wǎng)表配置到具體的FPGA芯片上,將工程的邏輯和時序與器件的可用資源匹配。布局布線是其中最重要的過程,布局將邏輯網(wǎng)表中的硬件原語和底層單元合理地配置到芯片內(nèi)部的固有硬件結(jié)構(gòu)上,并且往往需要在速度最優(yōu)和面積最優(yōu)之間作出選擇。布線根據(jù)布局的拓撲結(jié)構(gòu),利用芯片內(nèi)部的各種連線資源,合理正確地連接各個元件。也可以簡單地將布局布線理解為對FPGA內(nèi)部查找表和寄存器資源的合理配置,布局可以被理解挑選可實現(xiàn)設(shè)計網(wǎng)表的最優(yōu)的資源組合,而布線就是將這些查找表和寄存器資源以最優(yōu)方式連接起來。

目前,F(xiàn)PGA的結(jié)構(gòu)非常復(fù)雜,特別是在有時序約束條件時,需要利用時序驅(qū)動的引擎進行布局布線。布線結(jié)束后,軟件工具會自動生成報告,提供有關(guān)設(shè)計中各部分資源的使用情況。由于只有FPGA芯片生產(chǎn)商對芯片結(jié)構(gòu)最為了解,所以布局布線必須選擇芯片開發(fā)商提供的工具。

7)時序仿真

是指將布局布線的延時信息反標注到設(shè)計網(wǎng)表中來檢測有無時序違規(guī)(即不滿足時序約束條件或器件固有的時序規(guī)則,如建立時間、保持時間等)現(xiàn)象。時序仿真包含的延遲信息最全,也最精確,能較好地反映芯片的實際工作情況。由于不同芯片的內(nèi)部延時不一樣,不同的布局布線方案也給延時帶來不同的影響。因此在布局布線后,通過對系統(tǒng)和各個模塊進行時序仿真,分析其時序關(guān)系,估計系統(tǒng)性能,以及檢查和消除競爭冒險是非常有必要的。

8)FPGA板級調(diào)試

通過編程器將布局布線后的配置文件下載至FPGA中,對其硬件進行編程。配置文件一般為.pof或.sof文件格式,下載的方式包括AS(主動)、PS(被動)、JTAG(邊界掃描)等方式。

邏輯分析儀(LogicAnalyzer,LA)是FPGA設(shè)計的主要調(diào)試工具,但需要引出大量的測試管腳,且LA價格昂貴。目前,主流的FPGA芯片生產(chǎn)商都提供了內(nèi)嵌的在線邏輯分析儀(如XilinxISE中的ChipScope、AlteraQuartusII中的SignalTapII以及SignalProb)來解決上述矛盾,它們只需要占用芯片少量的邏輯資源,具有很高的實用價值。

FPGA總體設(shè)計的硬件考慮

FPGA在項目開始階段需要考慮的設(shè)計主要有3大方面:一個是硬件做板相關(guān)的FPGA升級電路的設(shè)計以及外圍IO設(shè)計;一個是與軟件配合相關(guān)的軟硬件接口設(shè)計;一個是FPGA內(nèi)部的邏輯功能規(guī)劃。本文先針對硬件設(shè)計相關(guān)進行闡述:

升級電路的設(shè)計:FPGA的好處就是產(chǎn)品發(fā)布后還能進行功能升級以及功能修改,但在客戶那里應(yīng)該沒有人會愿意打開機箱進行升級,這時就要設(shè)計可靠的升級通路。

1)板上有配置器件:如果上電后FPGA需要快速配置,這時一般會采用SPIFLASH的配置方式,這時我們就要設(shè)計一個電路如何更新SPIFLASH,如果板上有CPU,可以直接寫SPIFLASH,這種一般即使寫錯了,校驗后重新寫就好了。如果板上沒有CPU,那FPGA內(nèi)部或者配套的CPLD就要預(yù)留寫FLASH的通路。這個通路實際上就是設(shè)計一個用戶接口到SPI接口的橋接器,xilinx7系列以后的器件官方都提供了參考設(shè)計,而且支持SPIFlash中存入2個映像,其中一個是升級失敗后起機的golden映像(否則升級文件寫錯,板就變成磚頭了),雖然xilinx提供參考設(shè)計,但那只是針對SPIFLASH的操作,用戶還要設(shè)計預(yù)留通道與這個控制器對接,比如以太、SPI之類。這時配合的軟件就要考慮丟包、錯包這些影響,要保證文件都正確寫入FLASH。Altera公司應(yīng)該也是提供類似東西,原理上總是相通的。但quartus能寫入的一般都是自己的FLASH,否則就需要外接一個CPLD做配置電路,注意這個CPLD必須Altera自己的,否則不能用他的配置IP。

2)板上如果沒有配置器件,那CPU直接通過被動配置方式進行配置,就是控制programe、status、DIN那幾根線,CPU照時序做就好,缺點是CPU必須起來后才能進行配置。

3)目前還有一種配置就是通過PCIE接口,這個設(shè)計在電路上有一定要求,F(xiàn)PGA只需要掛接一個很小的SPIFLASH保存PCIE硬核的設(shè)置就好,起機后再把其他的功能映像從CPU端載入,這種一般再新的器件會支持,需要查看手冊詳細說明,不同器件再PCIE的復(fù)位以及其他引腳設(shè)計上還有要求。

這種配置一般用在PCIE的加速卡中,因為上電后系統(tǒng)會對PCIE設(shè)備進行掃描,一種好的做法就是通過SPIFLASH快速載入PCIE相關(guān)的映像,讓枚舉軟件看到FPGA,CPU完全起機后,再把需要的功能配置進去。

硬件相關(guān)的第2個設(shè)計是外圍IO的設(shè)計,包括VCCIO的電源連接、IO位置的分配、serdes的連接等。

雖然FPGA號稱IO可以支持多種標準電平,但也不是可以隨心所欲,特別是用到DDR3這些接口時。一種就是使勁看DS,但個人覺得太慢。好的做法是,建立一個demo工程,例化那些可能用到的外圍IOIP,比如DDR,PCIE,以太接口等,把這些examle放在一個代碼中不被優(yōu)化掉,編譯通過的話,一般IO分配就沒問題了,有問題再看文檔修改。編譯通過后從工程導(dǎo)出IO配置的CSV文件,xilinx的會比較詳細說明每個引腳的連接方式,包括端接等。Altera在工程目錄下有個.pin文件,似乎也有類似說明。有了這個文件基本上可以保證做板不會范大錯了。

-

FPGA

+關(guān)注

關(guān)注

1636文章

21841瀏覽量

608504 -

硬件

+關(guān)注

關(guān)注

11文章

3419瀏覽量

66703

發(fā)布評論請先 登錄

相關(guān)推薦

電子工程師必須知道的幾個技術(shù)問題

誠招FPGA、硬件、模擬電路工程師

誠聘FPGA、硬件與模擬電路工程師

招聘:軟件工程師(數(shù)字信號處理方向-FPGA)、硬件工程師

誠聘硬件研發(fā)工程師(FPGA)

誠聘FPGA軟件工程師

給MCU工程師詳解FPGA硬件屬性

給MCU工程師詳解FPGA硬件屬性

如何給MCU工程師詳解FPGA硬件屬性?

求FPGA開發(fā)工程師、硬件開發(fā)工程師各一名

FPGA工程師需要具備哪些技能?

電子工程師須知

給MCU工程師詳解FPGA硬件屬性

MCU工程師需要了解的FPGA硬件屬性

MCU工程師須知的FPGA硬件屬性

MCU工程師須知的FPGA硬件屬性

評論