聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

dsp

+關注

關注

553文章

7987瀏覽量

348760 -

ti

+關注

關注

112文章

8064瀏覽量

212365 -

協處理器

+關注

關注

0文章

75瀏覽量

18172

發布評論請先 登錄

相關推薦

【6670】BCP協處理器的加擾

A、芯片:DSP6670

B、硬件環境:TMDXEVM6670L開發板,仿真器是560v2?

C、軟件環境:CCS 5.3

D、調試目標:BCP協處

發表于 06-21 12:21

請教關于C6670 VCP2 測試例程

你好, 我要使用C6670的VCP2 。但在MCSDK 2.0.x中未找到相關的測試例程,TCP2的測試例程倒是都全。 請問是否有C6670的VCP2測試程序便于驗證其功能?為了驗證其

發表于 07-24 07:44

請問tms320c6670集成的通信協處理器是否需要額外收費?(TCP3d,TCP3e,VCP2,BCP,FFTC,RAC,TAC,RSA等)

請教一下,tms320c6670集成的通信協處理器(TCP3d,TCP3e,VCP2,BCP,FFTC,RAC,TAC,RSA等)是否需要額

發表于 07-25 06:14

請教關于C6455 VCP2問題

各位TI工程師你們好,我的程序在VCP2例程改的,但在單步調試時CSL_FINST (((CSL_DevRegs*)CSL_DEV_REGS)->PERLOCK

發表于 07-25 08:44

基于VCP的DSP維特比譯碼器的設計與實現

介紹了 TI 的TMS320C6416 DSP 片上Viterbi 譯碼協處理器(VCP)的結構與原理。給出了一種使用鏈式EDMA 結構和“乒乓”緩沖技術提高

發表于 12-23 15:19

?19次下載

調諧VCP2,TCP2的誤比特率性能

本應用筆記介紹了策略和編程方法優化VCP2和TI DSP TCP2誤碼性能。它假定讀者熟悉的卷積碼和Turbo編碼理論。

發表于 04-17 09:42

?5次下載

調整VCP2和TCP2位錯誤率性能的策略和編程方法

在大多數客戶應用中,高解碼比特錯誤率(BER)。性能是必需的。由于卷積碼和Turbo碼被廣泛使用在無線通信系統中,TI DSP集成了兩個高性能。嵌入式

發表于 04-25 09:05

?4次下載

使用GNU調試器在英特爾至強融核協處理器上調試(2-2)

第2部分,共2部分 - 在英特爾?至強融核?協處理器上進行調試:使用GNU項目調試器(GBD)

使用TMS320C6416協處理器:Viterbi協處理器(VCP)

電子發燒友網站提供《使用TMS320C6416協處理器:Viterbi協處理器(VCP).pdf》資料免費下載

發表于 10-21 09:36

?0次下載

使用TMS320C6416協處理器:Turbo協處理器(TCP)

電子發燒友網站提供《使用TMS320C6416協處理器:Turbo協處理器(TCP).pdf》資料免費下載

發表于 10-23 10:16

?0次下載

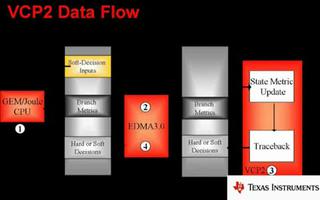

了解 TCP2/VCP2 協處理器在DSP中的應用

了解 TCP2/VCP2 協處理器在DSP中的應用

評論