聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

SDRAM

+關注

關注

7文章

423瀏覽量

55205 -

Altera

+關注

關注

37文章

781瀏覽量

153920 -

HSP

+關注

關注

0文章

13瀏覽量

14575

發布評論請先 登錄

相關推薦

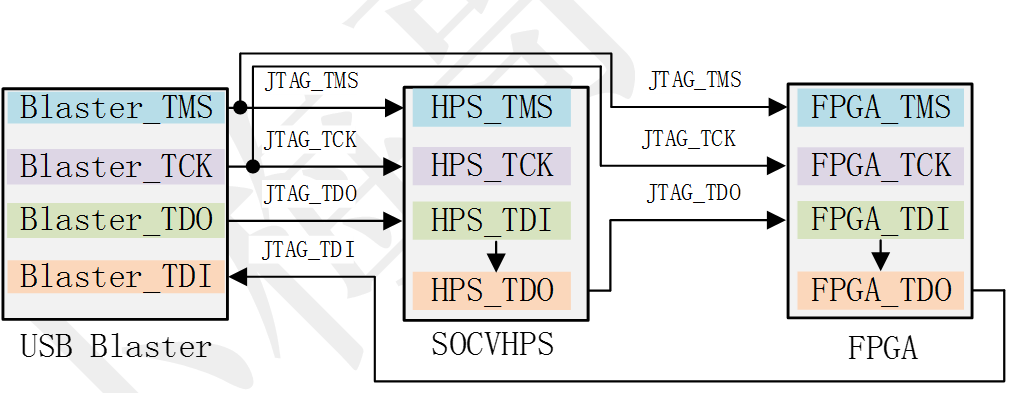

JTAG鏈路同時調試FPGA和HPS電路設計

SoC FPGA作為在同一芯片上同時集成了FPGA和HPS的芯片,其JTAG下載和調試電路相較于單獨的FPGA或ARM處理器都有一些差異,但是同時兩者又有緊密的聯系。

發表于 08-08 10:08

?1892次閱讀

ARM JTAG仿真器調試方法之SDRAM篇

要把映像文件加載到SDRAM中,除了要正確設置好映像文件的RO段基地址外(對于一個加載時域和運行時域相同的映像文件來說,RO段基地址實際上就是該映像文件

發表于 03-11 10:07

de1-soc FPGA(Quartus工程含Qsys系統) + HPS 操作步驟

原諒我記憶力不好。。。花了好久弄明白的東西才十個小時不到就忘記了,所以趁現在記得趕緊記錄下來。本文內容:重建de1-soc中HPS-FPGA工程。 PS:原工程在http

發表于 07-03 08:10

請問rtt目前在rt1052的板子上不支持從flash加載到sdram中運行嗎

project.uvprojx工程,編譯后下載程序總是在燒寫的時候出錯,無法完成下載驗證。另外從分散加載文件中也沒有找到程序加載到sdram

發表于 09-20 14:34

請問rtt目前在rt1052的板子上不支持從flash加載到sdram中運行嗎?

project.uvprojx工程,編譯后下載程序總是在燒寫的時候出錯,無法完成下載驗證。另外從分散加載文件中也沒有找到程序加載到sdram

發表于 10-12 15:10

如何使用SDRAM bank1從引導加載程序加載QSP應用程序呢?

你好 ,我正在使用引導加載程序使用 QSPI 跳轉應用程序。它在 QSPI 加載程序中正確跳轉。我在 QSPI 中遇到了一些計時問題。我計劃使用 S

發表于 12-20 07:15

使用HAL庫禁用定時器的ARR預加載功能的正確方法是什么?

我想知道使用 HAL 庫禁用定時器的 ARR 預加載功能的正確方法是什么?一旦完成,ARPE 位是否在整個運行時保持低電平,還是必須定期或在

發表于 01-31 06:35

LPC54S018和BOARD_SDRAM內存區的使用

?

然后我嘗試將可執行代碼移動到 SRAMX 內存區域。當我這樣做時,軟件加載和啟動過程在 Main() 啟動之前失敗。調試器似乎在 Res

發表于 02-28 07:39

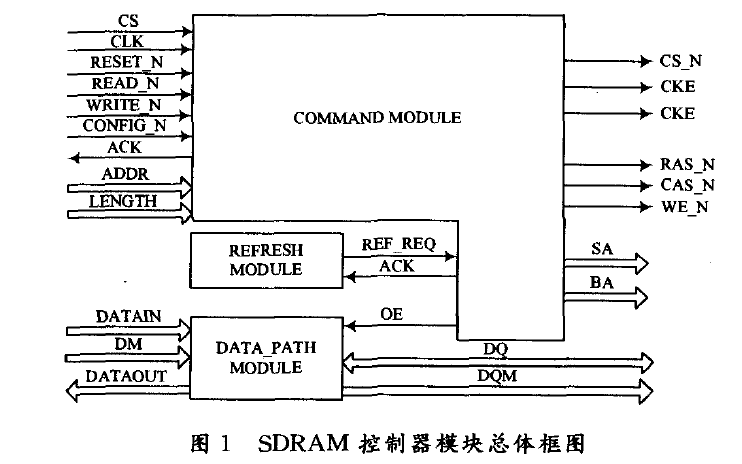

如何使用FPGA設計SDRAM控制器

針對SDRAM 操作繁瑣的問題,在對SDRAM 存儲器和全頁突發式操作進行研究的基礎上,提出一種簡易SDRAM 控制器的設計

發表于 12-18 16:13

?6次下載

在預加載器中調試HPS SDRAM的方法過程

在預加載器中調試HPS SDRAM的方法過程

評論