聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1629文章

21748瀏覽量

603866 -

IO

+關(guān)注

關(guān)注

0文章

448瀏覽量

39180 -

Altera

+關(guān)注

關(guān)注

37文章

783瀏覽量

153962

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA的IO約束如何使用

??set_input_delay屬于時(shí)序約束中的IO約束,我之前的時(shí)序約束教程中,有一篇關(guān)于s

發(fā)表于 09-06 09:22

?1982次閱讀

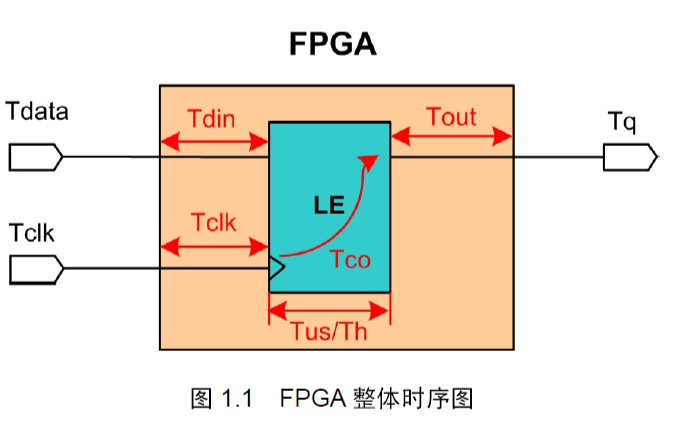

FPGA的IO口時(shí)序約束分析

在高速系統(tǒng)中FPGA時(shí)序約束不止包括內(nèi)部時(shí)鐘約束,還應(yīng)包括完整的IO時(shí)序約束和時(shí)序例外約束才

發(fā)表于 09-27 09:56

?1757次閱讀

FPGA 高級(jí)設(shè)計(jì):時(shí)序分析和收斂

今天給大俠帶來FPGA 高級(jí)設(shè)計(jì):時(shí)序分析和收斂,話不多說,上貨。

這里超鏈接一篇之前的STA的文章,僅供各位大俠參考。

FPGA STA(靜態(tài)

發(fā)表于 06-17 17:07

FPGA靜態(tài)時(shí)序分析——IO口時(shí)序(Input Delay /output Delay)

FPGA靜態(tài)時(shí)序分析——IO口時(shí)序(Input Delay /output Delay)1.1概述 在高速系統(tǒng)中

發(fā)表于 04-25 15:42

FPGA高級(jí)時(shí)序綜合教程

FPGA高級(jí)時(shí)序綜合教程The UCF FileUCF =用戶約束文件( User Constraints File )可以用文本編輯器和XilinxConstraints Editor (GUI

發(fā)表于 08-11 11:28

FPGA高級(jí)時(shí)序綜合教程

fpga高手經(jīng)驗(yàn)談doc文檔在數(shù)字電路的設(shè)計(jì)中,時(shí)序設(shè)計(jì)是一個(gè)系統(tǒng)性能的主要標(biāo)志,在高層次設(shè)計(jì)方法中,對(duì)時(shí)序控制的抽象度也相應(yīng)提高,因此在設(shè)

發(fā)表于 08-11 11:30

FPGA的時(shí)序優(yōu)化高級(jí)研修班

FPGA的時(shí)序優(yōu)化高級(jí)研修班通知通過設(shè)立四大專題,幫助工程師更加深入理解FPGA時(shí)序,并掌握時(shí)序

發(fā)表于 03-27 15:20

如何有效的管理FPGA設(shè)計(jì)中的時(shí)序問題

如何有效的管理FPGA設(shè)計(jì)中的時(shí)序問題

當(dāng)FPGA設(shè)計(jì)面臨到高級(jí)接口的設(shè)計(jì)問題時(shí),EMA的TimingDesigner可以簡(jiǎn)化這些設(shè)計(jì)問題

發(fā)表于 04-15 14:19

?718次閱讀

FPGA中的時(shí)序約束設(shè)計(jì)

一個(gè)好的FPGA設(shè)計(jì)一定是包含兩個(gè)層面:良好的代碼風(fēng)格和合理的約束。時(shí)序約束作為FPGA設(shè)計(jì)中不可或缺的一部分,已發(fā)揮著越來越重要的作用。毋庸置疑,

發(fā)表于 11-17 07:54

?2575次閱讀

FPGA中IO口的時(shí)序分析詳細(xì)說明

在高速系統(tǒng)中FPGA時(shí)序約束不止包括內(nèi)部時(shí)鐘約束,還應(yīng)包括完整的IO時(shí)序約束利序例外約束才能實(shí)現(xiàn)PCB板級(jí)的

發(fā)表于 01-13 17:13

?11次下載

FPGA設(shè)計(jì)中時(shí)序分析的基本概念

時(shí)序分析時(shí)FPGA設(shè)計(jì)中永恒的話題,也是FPGA開發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來,先介紹時(shí)序分析中

關(guān)于 FPGA 中的高級(jí) IO 時(shí)序

關(guān)于 FPGA 中的高級(jí) IO 時(shí)序

評(píng)論