元件充電模式(CDM) ESD被認為是代表ESD充電和快速放電的首要實際ESD模型,能夠恰如其分地表示當今集成電路(IC)制造和裝配中使用的自動處理設備所發生的情況。到目前為止,在制造環境下的器件處理過程中,IC的ESD損害的最大原因是來自充電器事件,這一點已廣為人知。(注1)

充電器件模型路線圖

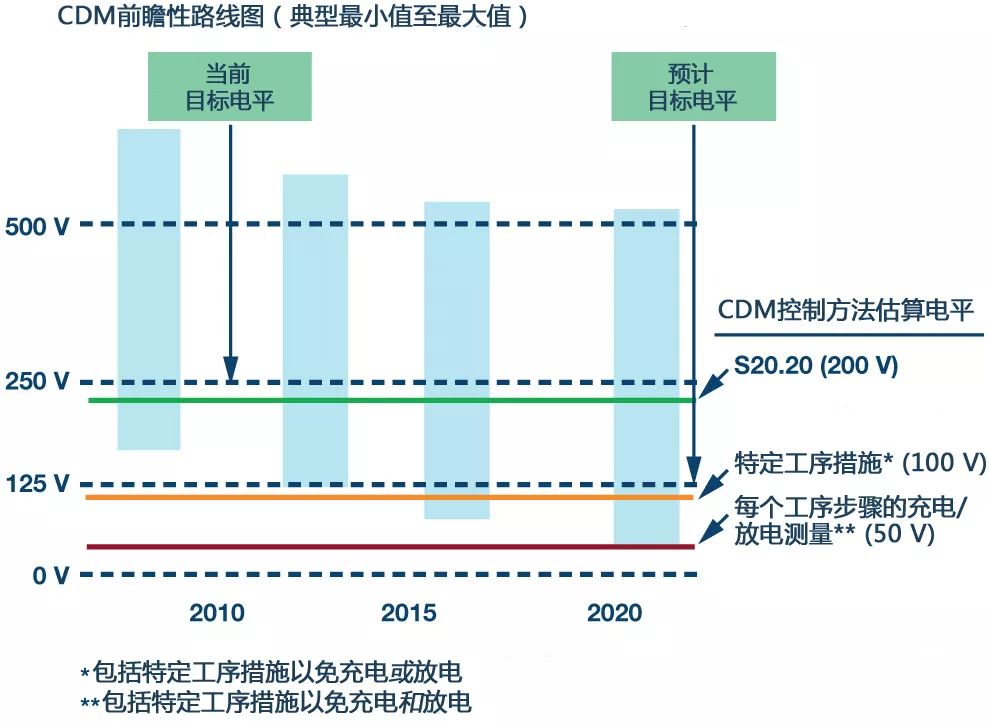

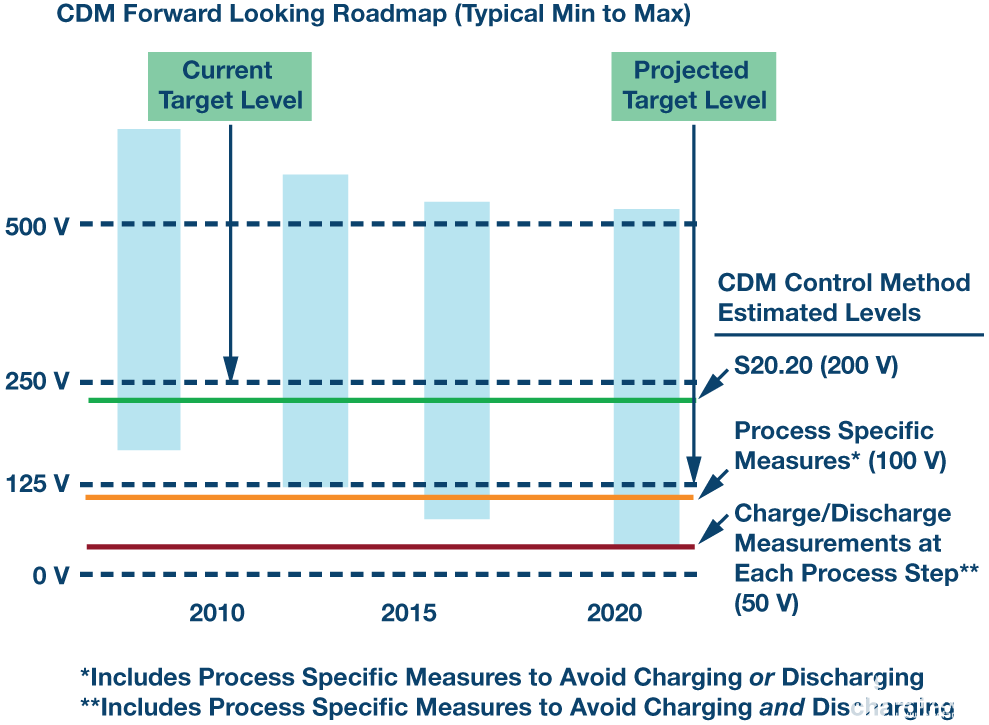

對IC中更高速IO的不斷增長的需求,以及單個封裝中集成更多功能的需要,推動封裝尺寸變大,因而維持JEP157(注2、3)中討論的推薦目標CDM級別將是一個挑戰。還應注意,雖然技術擴展對目標級別可能沒有直接影響(至少低至14 nm),但這些高級技術改進了晶體管性能,進而也能支持更高IO性能(傳輸速率),因此對IO設計人員而言,實現當前目標級別同樣變得很困難。由于不同測試儀的充電電阻不一致,已公布的ESD協會(ESDA)截止2020(注4)年路線圖建議,CDM目標級別將需要再次降低,如圖1所示。

圖1.2010年及以后的充電器件模型靈敏度限值預測(版權所有?2016 EOS/ESD協會)

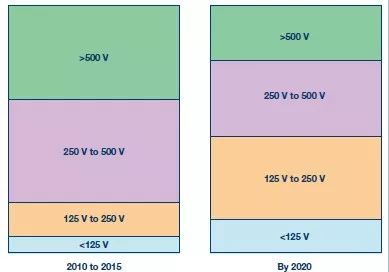

快速瀏覽圖1不會發現CDM目標級別有明顯變化,但進一步查閱ESDA提供的數據(如圖2所示)可知,CDM ESD目標級別的分布預期會有重大變化。

圖2.充電器件模型靈敏度分布組別前瞻(版權所有?2016 EOS/ESD協會)

為何討論此變化很重要?它指出了需要采用一致的方法來測試整個電子行業的CDM,應排除多種測試標準所帶來的一些不一致性。現在,確保制造業針對ESDA討論的CDM路線圖做好適當準備比以往任何時候都更重要。這種準備的一個關鍵方面是確保制造業從各半導體制造商收到的關于器件CDM魯棒性水平的數據是一致的。對一個協調一致的CDM標準的需求從來沒有像現在這樣強烈。再加上持續不斷的技術進步,IO性能也會得到提高。這種對更高IO性能的需要(以及降低引腳電容的需要),迫使IC設計人員別無選擇,只能降低目標級別,進而需要更精密的測量(在ANSI/ESDA/JEDEC JS-002中有說明)。

新聯合標準

在ANSI/ESDA/JEDEC JS-002之前有四種現存標準:傳統的JEDEC (JESD22-C101)(注5)、ESDA S5.3.1(注6)、AEC Q100-011(注7)和EIAJ ED-4701/300-2標準(注8)。ANSI/ESDA/JEDEC JS-002(充電器件模型、器件級別)(注9)代表了將這四種現有標準統一為單一標準的一次重大努力。雖然所有這些標準都產生了有價值的信息,但多種標準的存在對行業不是好事。不同方法常常產生不同的通過級別,多種標準的存在要求制造商支持不同的測試方法,而有意義的信息并無增加。因此,以下兩點非常重要:IC充電器件抑制能力的單一測量水平是廣為人知的,以確保CDM ESD設計策略得到正確實施;IC的充電器件抑制能力同它將接觸到的制造環境中的ESD控制水平一致。

為了解決這個問題,2009年成立的ESDA和JEDEC CDM聯合工作小組(JWG)開發了JS-002。此外,JWG希望根據引入場感應CDM (FICDM)以來所獲得的經驗教訓對FICDM進行技術改進10。最后,JWG希望盡量減少對電子行業的沖擊。為了減少行業沖擊,工作小組決定,聯合標準不應要求購買全新場感應CDM測試儀,并且通過/失敗水平應盡可能與JEDEC CDM標準一致。JEDEC標準是使用最廣泛的CDM標準,因此JS-002與當前制造業對CDM的理解保持一致。

雖然JEDEC和ESDA的測試方法非常相似,但兩種標準之間有一些不同之處需要化解。JS-002還試圖解決一些技術問題。一些最重要問題列示如下。

標準之間的差異

? 場板電介質厚度

? 用于驗證系統的驗證模塊

? 示波器帶寬要求

? 波形驗證參數

標準的技術問題

? 測量帶寬要求對CDM而言太慢

? 人為地讓JEDEC標準中的脈沖寬度很寬

為了達成目標并實現統一,作出了如下硬件和測量選擇。在為期五年的文件編制過程中,工作小組進行了大量測量才作出這些決定。

硬件選擇

? 使用JEDEC電介質厚度

? 使用JEDEC“硬幣”進行波形驗證

? 禁止在放電路徑中使用鐵氧體

測量選擇

? 系統驗證/驗收需要最低6 GHz帶寬的示波器

? 例行系統驗證允許使用1 GHz示波器

**盡量減少數據損壞并討論隱藏電壓調整 **

? 讓目標峰值電流與現有JEDEC標準一致

? 指定與JEDEC壓力級別匹配的測試條件;對于JS-002測試結果,指的是測試條件(TC);對于JEDEC和AEC,指的是伏特(V)

? 對于JS-002,調整場板電壓以提供與傳統JEDEC峰值電流要求對應的正確峰值電流

確保較大封裝完全充電

? 為確保較大封裝完全充電,引入了一個新的程序

下面說明這些改進。

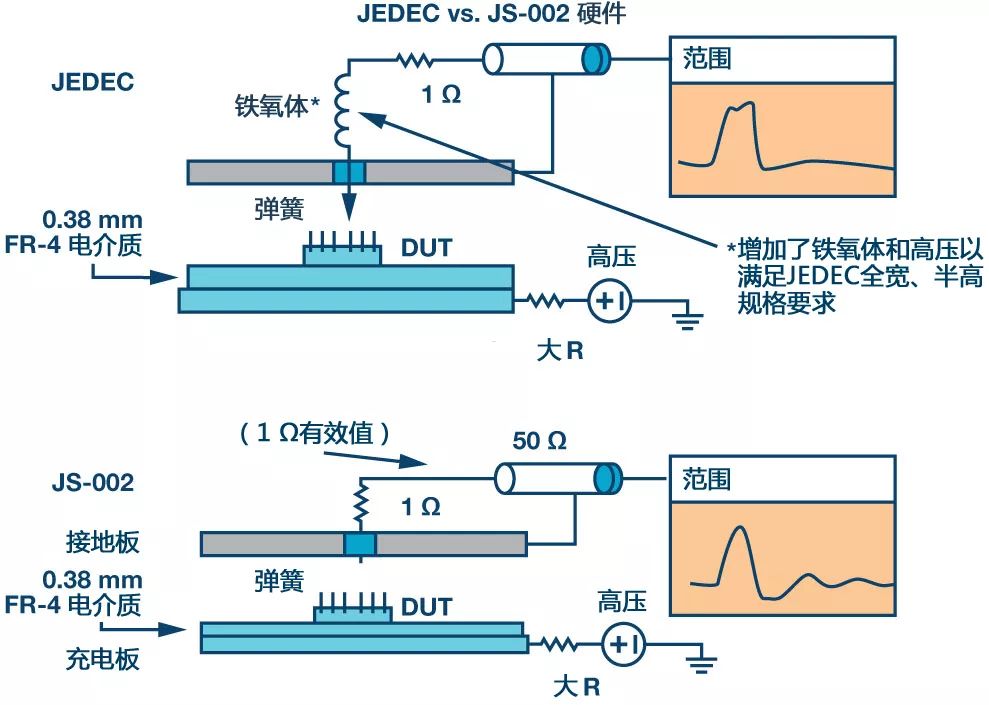

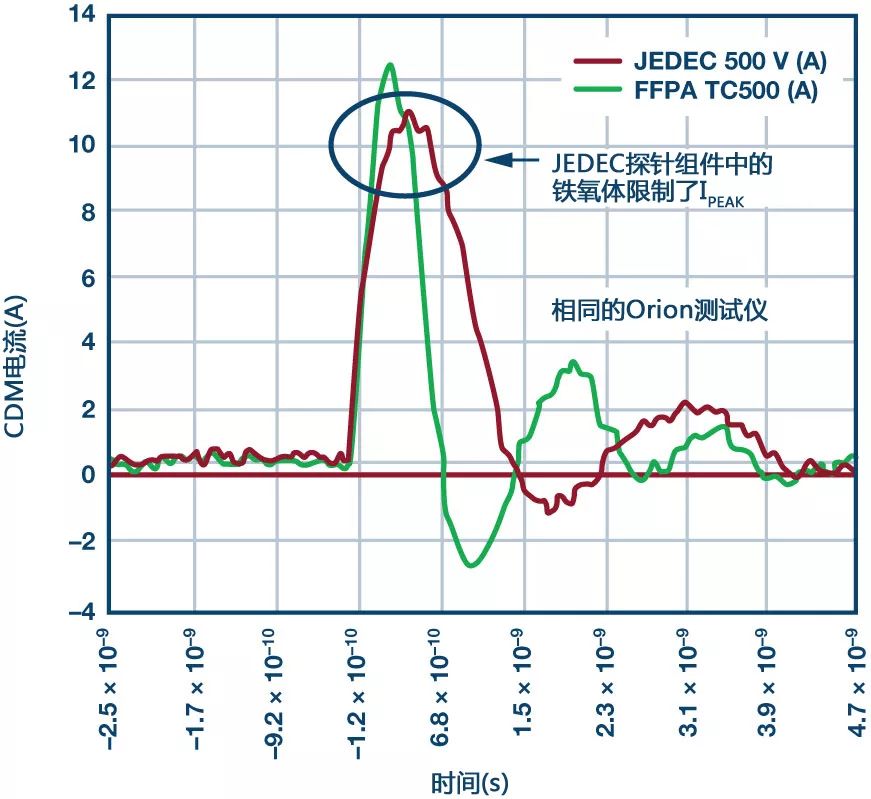

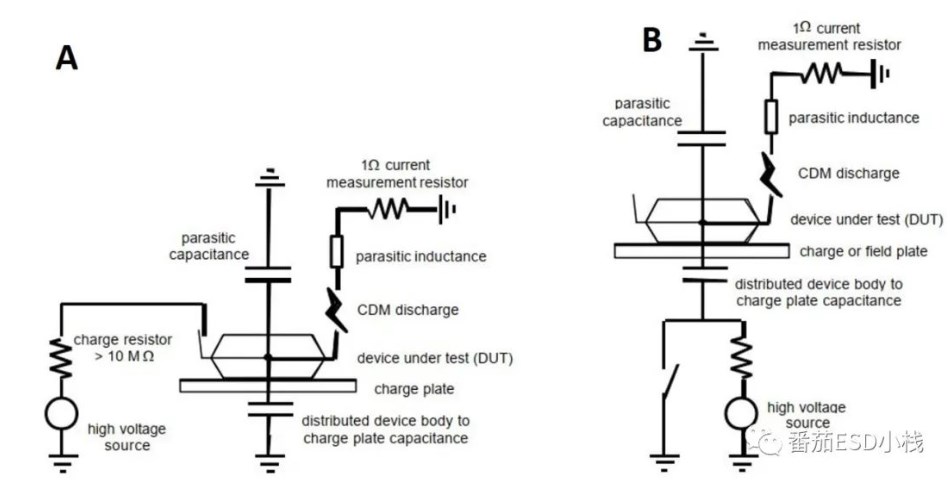

JS-002硬件選擇

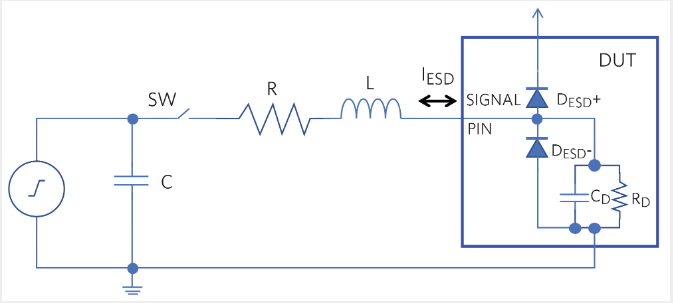

JS-002 CDM硬件平臺代表了ESDA S5.3.1探針組件或測試頭放電探針同JEDEC JESD22-C101驗證模塊和場板電介質的結合。圖3所示為硬件對比。ESDA探針組件的放電路徑中沒有特定鐵氧體。FICDM測試儀制造商認為,鐵氧體是必要的,增加鐵氧體可提高500 ps的半峰全寬(FWHH)額定最小值,并將Ip2(第二波峰)降至第一波峰Ip1的50%以下,從而滿足傳統JEDEC要求。JS-002去掉了此鐵氧體,從而消除了放電中的這種限制因素,使得放電波形更準確,高帶寬示波器在Ip1時看到的振鈴現象不再存在。

圖3.JEDEC和JS-002平臺硬件原理圖

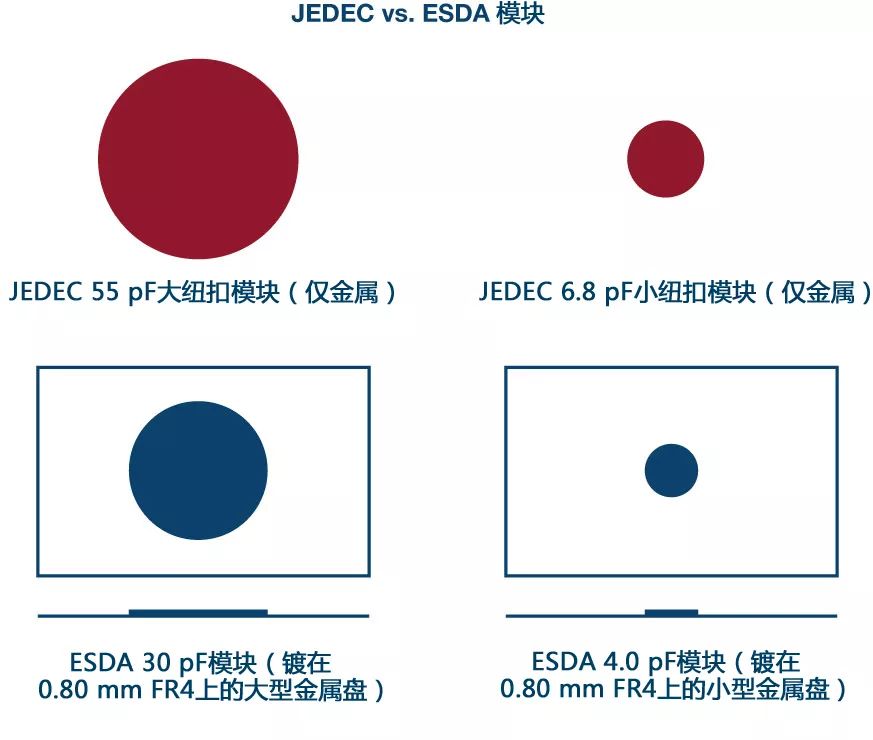

圖4顯示了ESDA和JEDEC CDM標準驗證模塊的區別。ESDA標準提供兩個電介質厚度選項,并結合驗證模塊(第二個選項是模塊和場板之間有一層最多130 μm的額外塑料薄膜,用于測試帶金屬封裝蓋的器件)。JEDEC驗證模塊/FR4電介質代表一個單一小/大驗證模塊和電介質選項,支持它的JEDEC標準用戶要多得多。

圖4.ESDA和JEDEC驗證模塊比較JS-002使用JEDEC模塊。

JS-002測量選擇

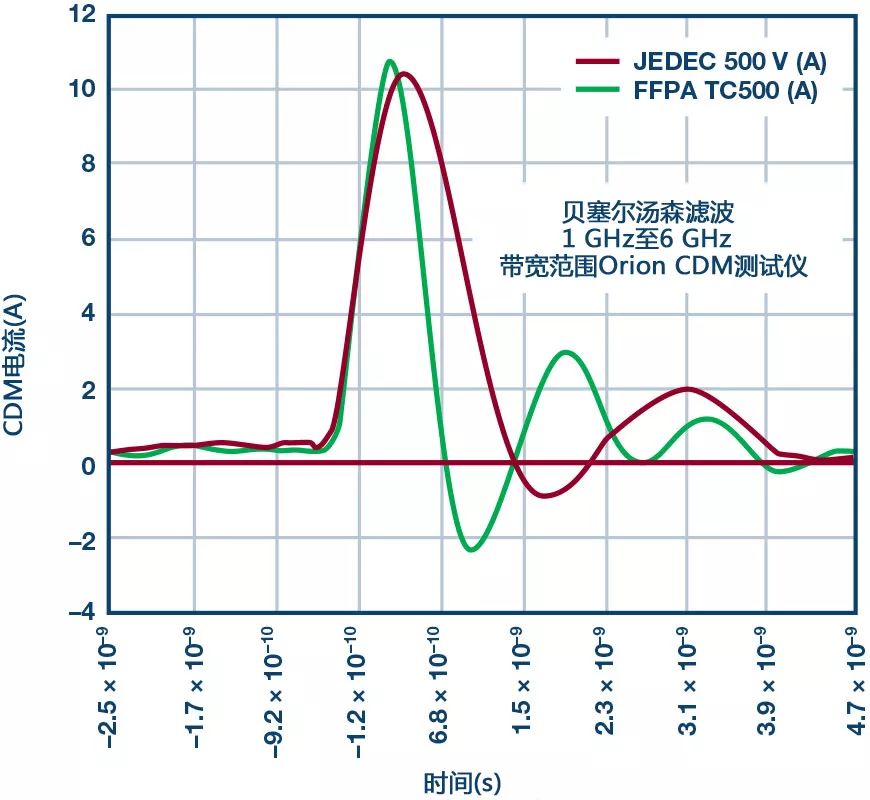

在JS-002標準制定的數據收集階段,CDM JWG發現需要更高帶寬的示波器才能精確測量CDM波形。1 GHz帶寬示波器未能捕捉到真正的第一峰值。圖5和圖6說明了這一點。

圖5.大JEDEC驗證模塊在500 V JEDEC時與JS-002 TC500在1 GHz時的CDM波形

圖6.大JEDEC驗證模塊在500 V JEDEC時與JS-002 TC500在6 GHz時的CDM波形

例行波形檢查,例如每日或每周的檢查,仍可利用1 GHz帶寬示波器進行。然而,對不同實驗室測試站點的分析表明,高帶寬示波器能提供更好的站點間相關性。(注11)例行檢查和季度檢查推薦使用高帶寬示波器。年度驗證或更換/修理測試儀硬件之后的驗證需要高帶寬示波器。

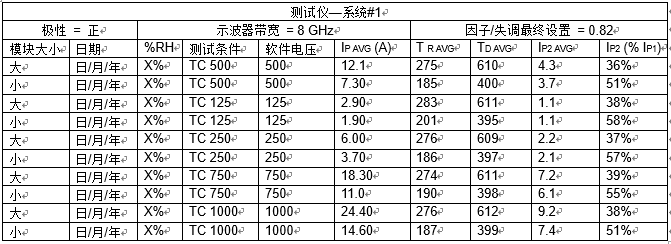

表1.JS-002波形數據記錄表示例,顯示了造成TC(測試條件)電壓的因素9

測試儀CDM電壓設置

CDM JWG同時發現,對于不同測試儀平臺,為了獲得符合先前ESDA和JEDEC標準的標準測試波形,實際板電壓設置需要有相當大的差異(例如,特定電壓設置為100 V或更大)。這在任何標準中都沒有說明。JS-002唯一地確定了將第一峰值電流(以及測試條件所代表的電壓)縮放到JEDEC峰值電流水平所需的偏移或因數。JS-002附錄G對此有詳細說明。表1顯示了一個包含此特性的驗證數據實例。

在設定測試條件下確保超大器件完全充電

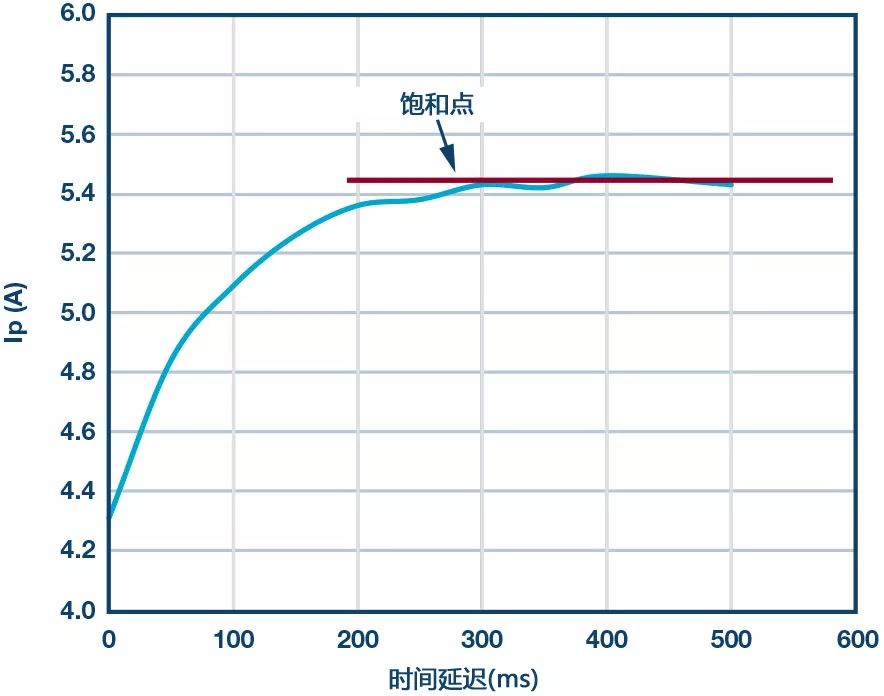

在JS-002開發的數據收集階段還發現了一個與測試儀相關的問題:放電之前,某些測試系統未將大驗證模塊或器件完全充電到設定電壓。不同測試系統的大值場板充電電阻(位于充電電源和場板之間的串聯電阻)不一致,影響到場板電壓完全充電所需的延遲時間。結果,不同測試儀的第一峰值放電電流可能不同,影響CDM的通過/失敗分類,尤其是大器件。

因此,工作小組撰寫了詳實的附錄H(“確定適當的充電延遲時間以確保大模塊或器件完全充電”),描述了用于確定器件完全充電所需延遲時間的程序。當出現峰值電流飽和點(Ip基本保持穩定,設置更長的延遲時間也不會使它改變)時,說明達到了適當的充電延遲時間,如圖7所示。確定此延遲時間,確保放電之前,超大器件能夠完全充電到設定的測試條件。

圖7.峰值電流與充電時間延遲關系圖示例,顯示了飽和點/充電時間延遲9

電子行業逐步采用JS-002

對于采用ESDA S5.3.1 CDM標準的公司,JS-002標準取代了S5.3.1,應將S5.3.1廢棄。對于先前使用JESD22-C101的公司,JEDEC可靠性測試規范文件JESD47(規定JEDEC電子元件的所有可靠性測試方法)最近進行了更新,要求用JS-002代替JESD22-C101(2016年末)。JEDEC會員公司轉換到JS-002的過渡時期現已開始。很多公司(包括ADI和Intel)已經對所有新產品利用JS-002標準進行測試。

國際電工委員會(IEC)最近批準并更新了其CDM測試標準IS 60749-28(注12)。此標準全盤納入JS-002作為其指定測試標準。

汽車電子理事會(AEC)目前有一個CDM小組委員會,其正在更新Q100-011(集成電路)和Q101-005(無源器件)車用器件CDM標準文件以納入JS-002,并結合AEC規定的測試使用條件。這些工作預計會在2017年底完成并獲批準。

結語

觀察ESDA提供的CDM ESD路線圖,可知在更高IO性能的驅動下,CDM目標級別會繼續降低。制造業對器件級CDM ESD耐受電壓的認知比以往任何時候都更重要,而來自不同CDM ESD標準的不一致產品CDM結果是無法傳達這一訊息的。ANSI/ESDA/JEDEC JS-002有機會成為第一個真正的適用于全行業的CDM測試標準。消除CDM測試頭放電路徑中的電容,可顯著改善放電波形的質量。引入高帶寬示波器用于驗證,提高到五個測試條件波形驗證級別,以及保證適當的充電延遲時間——所有這些措施顯著降低了不同實驗室的測試結果差異,改善了站點間的可重復性。這對確保向制造業提供一致的數據至關重要。電子行業接受JS-002標準之后,將有能力更好地應對前方的ESD控制挑戰。

-

集成電路

+關注

關注

5387文章

11530瀏覽量

361636 -

ESD

+關注

關注

48文章

2029瀏覽量

172929 -

ADI

+關注

關注

146文章

45819瀏覽量

249758

原文標題:新ANSI/ESDA/JEDEC JS-002 CDM測試標準概覽

文章出處:【微信號:eet-china,微信公眾號:電子工程專輯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ANSI、ESDA、JEDEC JS-002 CDM測試概覽 IC的ESD損害最大原因來自充電器

ANSI、ESDA、JEDEC JS-002 CDM測試概覽 IC的ESD損害最大原因來自充電器

評論