模擬設(shè)計從來都不容易。工程師們可以把整個職業(yè)生涯都花在鎖相環(huán)(PLL)上,因為要讓它們正確,就需要深入了解電路的功能,包括它們在不同的制程邊界和不同的制造工藝中的響應(yīng)。

在FinFET時代,這些挑戰(zhàn)在模擬電路中愈演愈烈。例如,重用在數(shù)字設(shè)計中是很常見的做法,但是它并沒有應(yīng)用到模擬設(shè)計的多個節(jié)點中,因為模擬電路的微縮不能超過某個特定的界限。

從技術(shù)上講,這種情況有幾個原因。西門子Mentor公司模擬/混合信號驗證部門產(chǎn)品營銷與管理總監(jiān)Mick Tegethoff表示:“高精度模擬設(shè)計人員不會對重用和遷移感到滿意,因為舉例來說,模擬技術(shù)中沒有任何工具可以保證時序收斂。我們看到傳統(tǒng)的模擬設(shè)計師花了很多時間去真正理解設(shè)計的功能。”

在FinFET節(jié)點中出現(xiàn)的越來越多的物理和靜電效應(yīng)迫使工程團(tuán)隊將遷移作為一種選擇,并重新考慮架構(gòu)、設(shè)計電路,同時進(jìn)行更多的驗證。

Tegethoff表示:“推動這一切的是更小的幾何圖案,它實際上包含一些有助于模擬設(shè)計的特性。從某種意義上說,模擬器件的微縮會使漏電流之類效應(yīng)得到改善,但它的微縮并不像數(shù)字器件。這不是那種只要微縮就能完成的事情。有些事情確實使它變得更加困難。對于高精度ADC、PLL和精密模擬電路,當(dāng)你遷移到越來越高級的節(jié)點時,器件本身的隨機(jī)噪聲就會成為不可忽視的主要因素,這需要在仿真中加以考慮。”

For the two types of noise that are on transistors — thermal noise and flicker noise — transient noise analysis can be run within SPICEsimulation. “This is a time-domain analysis, but at every time step it inserts the random noise for each of the devices,” Tegethoff said. “And while it does make stimulation take longer, design teams can simulate complex PLLs or high precision ADCs in the time domain to see it locking, see its stability.

對于晶體管上的兩種噪聲類型——熱噪聲(thermal noise)和閃爍噪聲(flicker noise),可以在SPICE仿真中運行瞬態(tài)噪聲分析。Tegethoff說:“這是一種時域分析,但每一步都為每個器件插入隨機(jī)噪聲。雖然它確實能使仿真花費更長的時間,但設(shè)計團(tuán)隊可以在時域仿真復(fù)雜的PLL或高精度ADC,以觀察它的鎖定或穩(wěn)定性。”

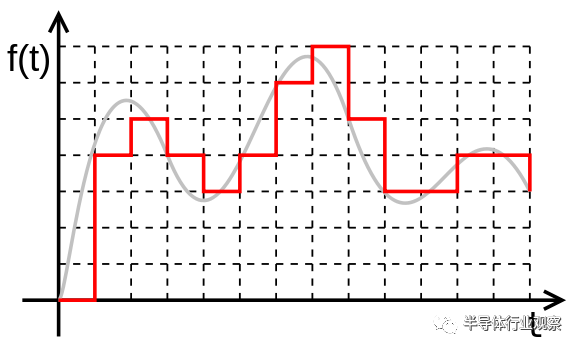

圖1:數(shù)字與模擬信號。(來源:維基百科)

另一個越來越大的挑戰(zhàn)涉及互連電阻,這個問題在每個新節(jié)點上都日益嚴(yán)重。對于互連,互連本身的電阻和電容必須在電路的仿真中進(jìn)行考慮。否則它就會不準(zhǔn)確。導(dǎo)體越薄,電阻越大。

Tegethoff說:“如果晶體管的輸出與另一個晶體管連接在一起,那么在以前,你可以把它看成是零電阻的理想導(dǎo)線。現(xiàn)在它有了一定的電阻,這就意味著在電路layout之后,必須提取layout寄生參數(shù)。這些必須反饋到原理圖中,并在包含所有內(nèi)容的情況下再次進(jìn)行模擬。這將導(dǎo)致電路上的元件數(shù)量增加100,000倍,從而仿真時間要長得多。如果你使用電阻進(jìn)行仿真,發(fā)現(xiàn)它不符合規(guī)范,那么你必須返回,更改內(nèi)容并再次進(jìn)行模擬——更不用說需要進(jìn)行額外的驗證。”

在模擬IP中,驅(qū)動復(fù)雜性的其他因素包括器件本身的可變性,這需要蒙特卡羅類型的分析來確保可變性是可控的。器件的行為特性依賴于layout內(nèi)容和環(huán)境,而這通常是由layout依賴效應(yīng)(LDE)所導(dǎo)致的。Cadence設(shè)計IP高級產(chǎn)品營銷經(jīng)理Muthu Vairavan表示,這些效應(yīng)顯著增加了設(shè)計和layout之間的迭代。

Vairavan說:“此外,由于復(fù)雜的設(shè)計規(guī)則,使用多重曝光印制這些低級幾何圖案增加了通常的layout周期。模擬設(shè)計人員還需要考慮與線邊緣粗糙度相關(guān)的不匹配效應(yīng)和這些低級特征尺寸的互連變化。FinFET的出現(xiàn)給模擬設(shè)計帶來了額外的限制,因為器件寬度現(xiàn)在必須是鰭片的離散倍數(shù)(與平面晶體管不同)。這些器件還容易受到鰭片寬度和高度制造變化的影響,以及通孔和互連電阻的影響,這使得模擬匹配變得復(fù)雜。”

盡管模擬設(shè)計人員和工具供應(yīng)商已采用新的設(shè)計方法和工具流程來適應(yīng)這些變化,但每個節(jié)點都帶來了新的復(fù)雜性,導(dǎo)致成本和上市時間的挑戰(zhàn)。Vairavan指出:“在高性能企業(yè)應(yīng)用中看到的一個日益增長的趨勢是,從SoC轉(zhuǎn)向系統(tǒng)級封裝(SiP)設(shè)計,其中多個模擬和數(shù)字芯片集成在封裝內(nèi)。這使得數(shù)字設(shè)計能夠轉(zhuǎn)移到高級節(jié)點以實現(xiàn)產(chǎn)品差異化,但仍然使用來自舊節(jié)點的經(jīng)過驗證的模擬IP。這得益于多芯片模塊和2.5D集成技術(shù)的進(jìn)步,以及高帶寬、低功耗封裝內(nèi)互聯(lián)的可用性的提升。”

但是,對于低成本的系統(tǒng)應(yīng)用來說,挑戰(zhàn)仍然存在,封裝級集成的成本增加是不合理的。Vairavan補(bǔ)充說:“即使在高性能數(shù)據(jù)中心和云應(yīng)用中,關(guān)鍵的混合信號設(shè)計,比如非常高速的基于DSP的SerDes,也將受益于更高密度和更低功率的高級節(jié)點。因此,模擬設(shè)計人員需要繼續(xù)創(chuàng)新,代工廠商和工具供應(yīng)商需要在模擬設(shè)計早期的工藝和工具開發(fā)周期中加入模擬設(shè)計反饋,以緩解這些挑戰(zhàn)。模擬IP是許多SoC設(shè)計中的關(guān)鍵區(qū)別,它們的性能和質(zhì)量對于這些產(chǎn)品的成功至關(guān)重要。”

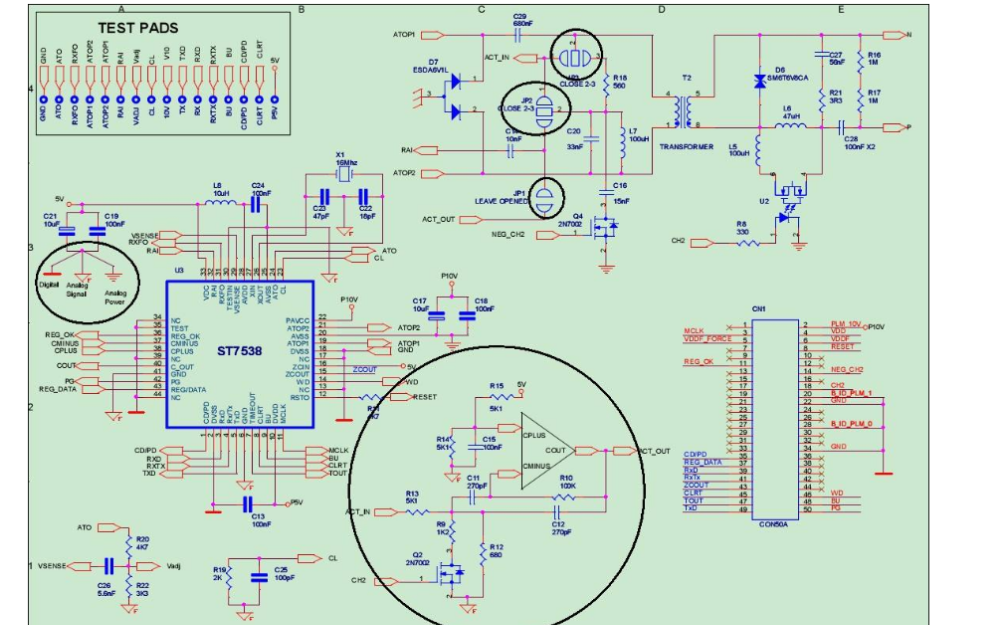

圖2:并非所有東西都可以數(shù)字化(來源:Center Point Audio)

節(jié)點和代工挑戰(zhàn)

模擬電路的工藝遷移一直都很棘手,但在FinFET領(lǐng)域,它已經(jīng)成為一個更大的問題。

ArterisIP技術(shù)顧問Ed Petrus解釋說:“因為先進(jìn)節(jié)點面臨的挑戰(zhàn),人們稱之為遷移的舊技術(shù)或多或少與壓縮有些相似,例如,在現(xiàn)有l(wèi)ayout中,350nm等較舊節(jié)點的PLL會增加一個0.X的乘數(shù)因子。對于模擬電路而言,這一直是個問題,因為模擬電路對于匹配這樣的設(shè)計技術(shù)提出了非常嚴(yán)格的要求,當(dāng)有兩根導(dǎo)線進(jìn)出某種差分電路時,這兩根導(dǎo)線的電流必須匹配。這是通過在該電路中非常嚴(yán)格地放置器件來實現(xiàn)的。舊式的壓縮的問題在于,因為它是一種算法,它不理解這些嚴(yán)格的要求。在模擬世界中,這些稱之為約束。這些匹配的要求最終會通過壓縮在不知不覺中被破壞。因此,最終的電路將無法正常工作。”

這個問題從180nm開始就存在。在此之下,一切都需要重新設(shè)計。

Petrus表示:“器件的特性發(fā)生了很大的變化,設(shè)計人員必須重新審視電路,并確定電路的現(xiàn)有類型是否真的適用于新節(jié)點。如果它可以工作,那么topology將得以保持,器件尺寸也會得到調(diào)整,這通常足夠了。但對于高級節(jié)點來說,這是不太可能的,所以設(shè)計團(tuán)隊最終會回到電路并重新設(shè)計大部分內(nèi)容。”

高級工藝節(jié)點根本不是在考慮模擬特性的情況下創(chuàng)建的。它們是為了數(shù)字電路的面積微縮而開發(fā)的。

Synopsys的產(chǎn)品營銷經(jīng)理Manuel Mota表示:“實際情況是,模擬電路和模擬接口最終需要集成到數(shù)字模塊中,當(dāng)然,設(shè)計這些模塊的人和想要集成它們的人確實面臨著挑戰(zhàn),這是可以解決的。”

這些挑戰(zhàn)源自工藝的內(nèi)在特性。Mota說:“其中的一些效應(yīng)甚至開始出現(xiàn)在大批量工藝中,使用FinFET影響會更明顯。而且,這些器件本身要復(fù)雜得多,而且它們的建模也變得更加復(fù)雜,并且更難以使用。特征不再依賴于內(nèi)在器件的直接鄰近。現(xiàn)在,鄰近效應(yīng)(proximity effects)已經(jīng)遠(yuǎn)遠(yuǎn)超出了通常的效應(yīng),設(shè)計師們再也不能假設(shè)晶體管的某些特性來設(shè)計了。必須假設(shè)它是在一個大回路中,并且必須考慮周圍產(chǎn)生的所有這些影響。這不僅適用于器件,也適用于器件周圍的連接。所以把一個器件和另一個器件連起來同樣相當(dāng)復(fù)雜。”

即使使用金屬疊層,過去也可以認(rèn)為它們幾乎是理想的,但是現(xiàn)在的電阻、電容和寄生效應(yīng)在整個電路設(shè)計的特性中都扮演著重要角色。此外,還有與FinFET相關(guān)的效應(yīng)。

Mota說:“你不能再任意設(shè)計你想要的柵寬度和柵長度,在過去這是可能的。這對于模擬設(shè)計的意義是,首先,該工藝通常對模擬設(shè)計的特征較少,因此對電路的電氣特性有更多的不確定性。你必須遵守和驗證的規(guī)則要復(fù)雜得多,驗證設(shè)計也變得更加耗時,在高級節(jié)點中可以輕而易舉地增加3、4倍。”

此外,過去在非常保守的電模擬節(jié)點(如老化和可靠性)中,一些設(shè)計不敏感的東西現(xiàn)在卻至關(guān)重要,尤其是在汽車、醫(yī)療和工業(yè)應(yīng)用領(lǐng)域。

Mota說:“你需要對它們進(jìn)行設(shè)計并驗證一切。這再次延長了設(shè)計周期。而在模擬方面,在仿真過程中,如果你正在處理電壓和電流的精細(xì)演變,這可能意味著非常長的驗證周期。這是主要的挑戰(zhàn)之一。然后,當(dāng)談到工藝和器件的特性時,它們并不一定是模擬設(shè)計的理想選擇,假設(shè)你有一個以數(shù)字為中心的設(shè)備,它的模擬特性很差。也許它們從模擬的角度進(jìn)行了很差的建模,而這些通常不會被現(xiàn)代模擬設(shè)計所解決,傳統(tǒng)技術(shù)無法解決您想要創(chuàng)建線性設(shè)計的問題。在某種程度上,你做的恰恰相反。你得承認(rèn)這個工藝并不好,得接受這個工藝的特點和你正在設(shè)計的晶體管的特性不是很好。你所做的就是利用這個工藝中的優(yōu)點,比如器件豐富。在這個工藝中,你可以有幾百萬個門,基本是免費的,而且可以進(jìn)行校準(zhǔn)。”

Tegethoff說:“鑒于所有這些,權(quán)衡是一個微妙的平衡。如果你有關(guān)于電路的知識并且確實遷移,那么有時必須調(diào)整電路。你運行的驗證越多,運行的仿真越多,運行的變異性感知仿真(variability-aware simulation)越多,那么你擁有的裕度就越小,異常現(xiàn)象就不會發(fā)生。不幸的是,在模擬方面,很大一部分裕度是面積或功率。為了減少噪音的影響,你需要提高功率一類的東西。最后,器件本身的模型更加復(fù)雜。FinFET器件模型的方程會多出3、4倍。”

高級節(jié)點中模擬IP的問題最終歸結(jié)為一切都變得越來越復(fù)雜,三階效應(yīng)成為一階效應(yīng)。Tegethoff說:“最終的結(jié)果是,我們不斷要求在這些節(jié)點上進(jìn)行SPICE精確仿真,包括更長時間的仿真、更多的仿真、智能環(huán)境的需要,例如蒙特卡洛模擬持續(xù)要求電路仿真準(zhǔn)確,但需要變得更快,處理更大規(guī)模的電路,以便它們能夠在合理的時間內(nèi)完成工作。”

結(jié)論

展望未來,考慮到支持諸如5G之類的技術(shù)的頻率和帶寬所需要的東西,設(shè)計師仍然需要全力以赴來解決這一切。這是極其復(fù)雜的,而且會變得更加復(fù)雜。

Tegethoff 表示:“模擬內(nèi)容正變得越來越重要,因為它們都處于邊界。無論是物聯(lián)網(wǎng)、通信還是汽車,你都必須應(yīng)對模擬世界。這些接口需要更快,他們需要保持準(zhǔn)確,并且需要低功耗。”

曾經(jīng)有點孤立的模擬設(shè)計藝術(shù)現(xiàn)在不得不處理許多與先進(jìn)的數(shù)字設(shè)計相同的問題,而且還有模擬電路的一些特有難題。

-

模擬電路

+關(guān)注

關(guān)注

125文章

1561瀏覽量

102796 -

FinFET

+關(guān)注

關(guān)注

12文章

248瀏覽量

90267

原文標(biāo)題:模擬電路設(shè)計面對的新挑戰(zhàn)

文章出處:【微信號:WW_CGQJS,微信公眾號:傳感器技術(shù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

想學(xué)模擬電路設(shè)計的可以看看 《模擬Cmos集成電路設(shè)計》畢查德.拉扎維著

【下載】《實用模擬電路設(shè)計》--湯普森

模擬電源電路設(shè)計資料(經(jīng)典)

智能節(jié)點模板電路設(shè)計

實用模擬電路設(shè)計PDF電子書免費下載

實用模擬電路設(shè)計電子書教材免費下載

實用模擬電路設(shè)計的PDF電子書免費下載

模擬電路設(shè)計面對的節(jié)點和代工挑戰(zhàn)

模擬電路設(shè)計面對的節(jié)點和代工挑戰(zhàn)

評論