在過去幾十年里,摩爾定律指引著集成電路產(chǎn)業(yè)的發(fā)展,芯片制造工藝也在按部就班地推進。但進入了最近幾年,芯片的微縮周期因受到硅材料本身特性和設(shè)備的限制而逐漸變慢。換句話說,摩爾定律失效了。

全球半導(dǎo)體行業(yè)研發(fā)規(guī)劃藍圖協(xié)會主席Paolo Gargini在早年也曾表示,按照最快的發(fā)展速度看,到2020年,我們的芯片線路可以達到2-3納米級別,然而在這個級別上只能容納10個原子。這時候芯片的電子將受限于量子的不確定性,晶體管變得不可靠,尋找硅以外的替代材料和新技術(shù)就成為工程師們的工作重點。

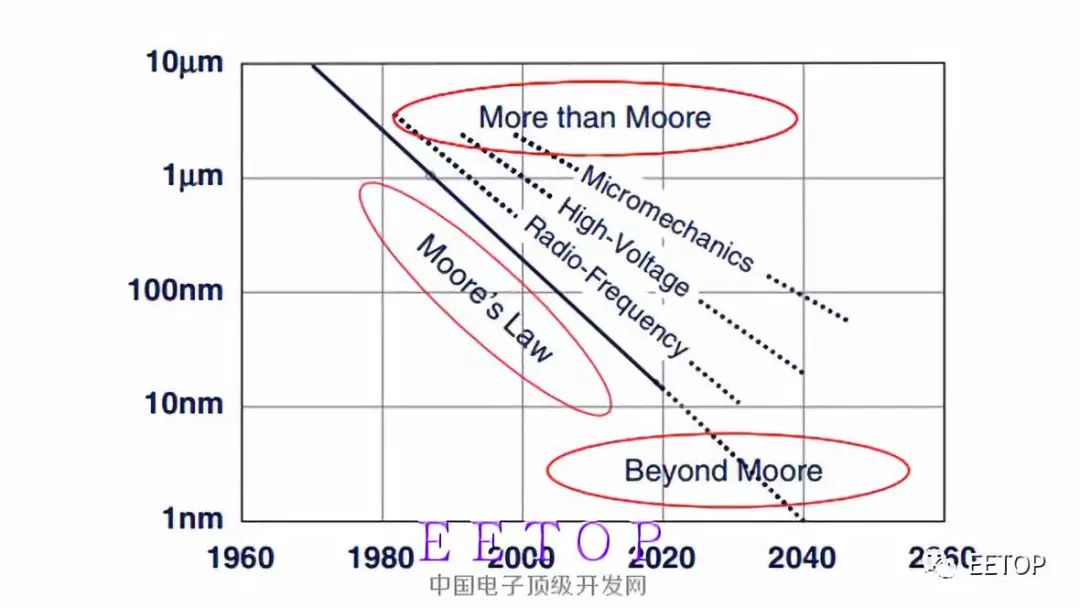

為了延續(xù)之前的芯片前進步伐,產(chǎn)業(yè)研正在材料等方面探索芯片演進的新解決辦法:More Moore、More than Moore和Beyond CMOS就成為了其中的選擇。其中More Moore和More than Moore被稱為非硅微電子學(xué)。

集成電路產(chǎn)業(yè)發(fā)展的三個方向

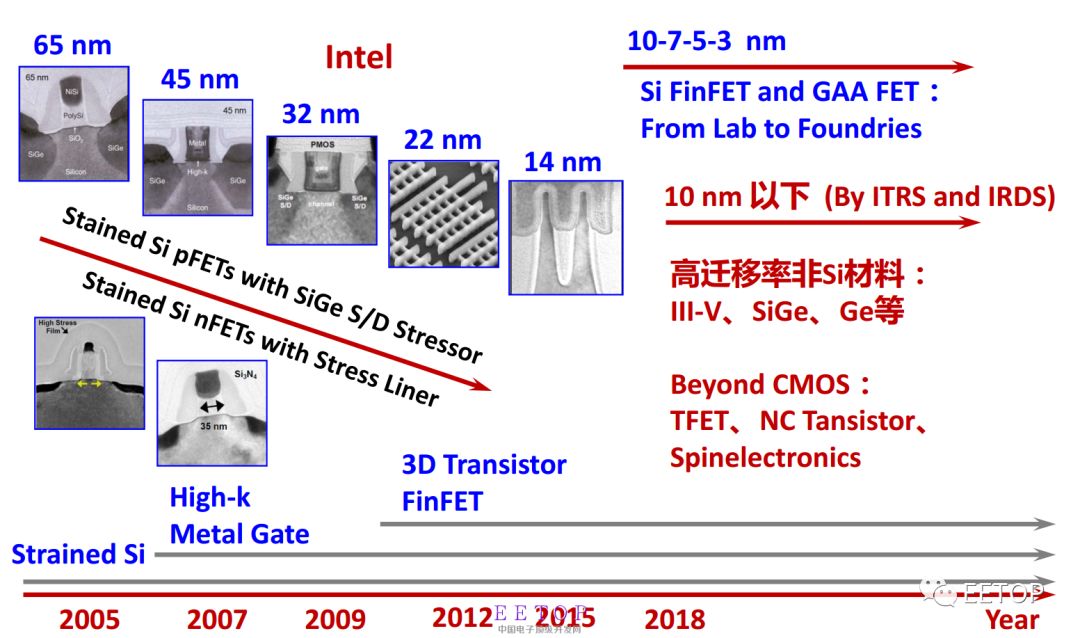

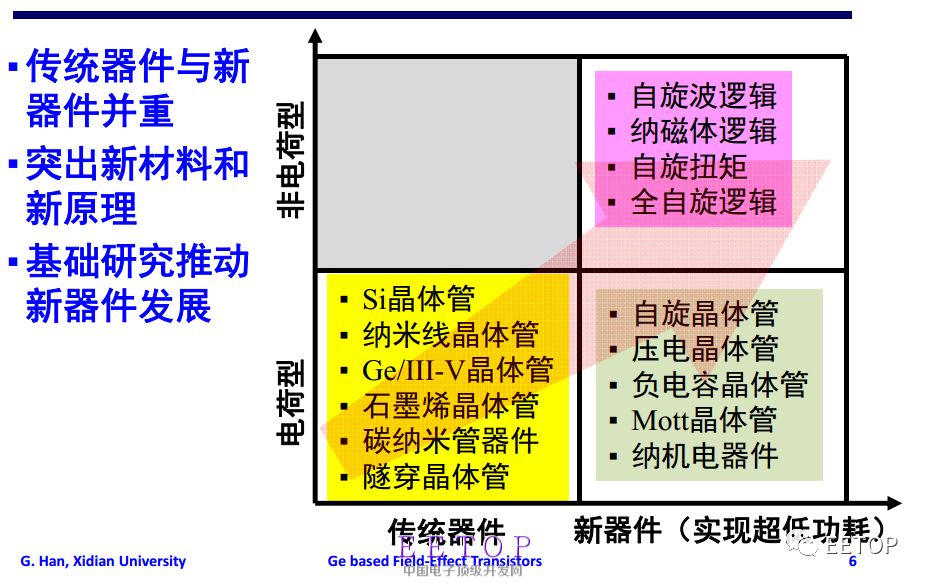

根據(jù)定義,所謂More Moore是想辦法沿著摩爾定律的道路繼續(xù)前進;More than Moore做的是發(fā)展在之前摩爾定律演進過程中所謂開發(fā)的部分;Beyond CMOS做的是發(fā)明在硅基CMOS遇到物理極限時所能倚重的新型器件。如下圖所示,根據(jù)ITRS和IRDS的規(guī)劃,到10nm之后,三五族半導(dǎo)體、SiGe和Ge等高遷移非硅材料;TFET、NC警惕光和自旋電子等Beyond CMOS選擇將會成為產(chǎn)業(yè)追尋的新方向。

CMOS設(shè)備的進化

但我們也應(yīng)該看到,在這些新方法后面,存在更多的問題。例如More Moore的漏電問題,More than moore的多模塊封裝,還有Beyond CMOS面臨的功耗瓶頸問題。

Beyond CMOS的功耗瓶頸

圍繞著這些新技術(shù)和新材料的電子遷移率、空穴遷移率、靜待遷移率,還有材料本身的各種表征特性,都是大家非常關(guān)注的。

為此,西安電子科技大學(xué)的韓根全教授作了一個題為《Ge based Tunneling and Negative Capacitance FETs: Devices andCharacterization》的演講,為大家解析芯片新思路背后的門道和解決方法。

-

芯片

+關(guān)注

關(guān)注

455文章

50732瀏覽量

423260 -

集成電路

+關(guān)注

關(guān)注

5387文章

11536瀏覽量

361664 -

摩爾定律

+關(guān)注

關(guān)注

4文章

634瀏覽量

79003

原文標(biāo)題:PPT|摩爾定律失效后的芯片該怎么發(fā)展?

文章出處:【微信號:eetop-1,微信公眾號:EETOP】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

上海集成電路產(chǎn)業(yè)迎來發(fā)展機遇

[轉(zhuǎn)帖]集成電路產(chǎn)業(yè)將迎來發(fā)展高潮 IC設(shè)計是亮點

中國集成電路發(fā)展探秘

微電子的三個發(fā)展方向—縮小器件尺寸、soc、產(chǎn)業(yè)增長點

2016我國集成電路產(chǎn)業(yè)發(fā)展現(xiàn)狀及前景

集成電路市場的產(chǎn)業(yè)格局與產(chǎn)業(yè)結(jié)構(gòu)

世界集成電路發(fā)展歷程及產(chǎn)業(yè)結(jié)構(gòu)的變化

集成電路可測性設(shè)計方法

我國將繼續(xù)鼓勵集成電路產(chǎn)業(yè)發(fā)展

IC觀察:集成電路產(chǎn)業(yè)發(fā)展再思考

全球集成電路產(chǎn)業(yè)的發(fā)展特點是什么?

國內(nèi)集成電路產(chǎn)業(yè)的發(fā)展現(xiàn)狀

集成電路IP產(chǎn)業(yè)發(fā)展的現(xiàn)狀和問題分析

后摩爾時代集成電路產(chǎn)業(yè)特性及發(fā)展趨勢

集成電路產(chǎn)業(yè)發(fā)展的三個方向

集成電路產(chǎn)業(yè)發(fā)展的三個方向

評論