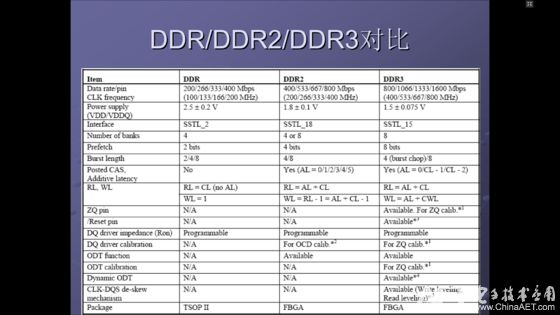

DDR2與DDR的區(qū)別

1、速率與預取量

DDR2的實際工作頻率是DDR的兩倍,DDR2內(nèi)存擁有兩倍于標準DDR內(nèi)存的4bit預期能力。

2、封裝與電壓

DDR封裝為TSOPII,DDR2封裝為FBGA;

DDR的標準電壓為2.5V,DDR2的標準電壓為1.8V。

3、bit pre-fetch

DDR為2bit pre-fetch,DDR2為4bit pre-fetch。

4、新技術(shù)的引進

DDR2引入了OCD、ODT和POST

(1)ODT:ODT是內(nèi)建核心的終結(jié)電阻,它的功能是讓DQS、RDQS、DQ和DM信號在終結(jié)電阻處消耗完,防止這些信號在電路上形成反射;

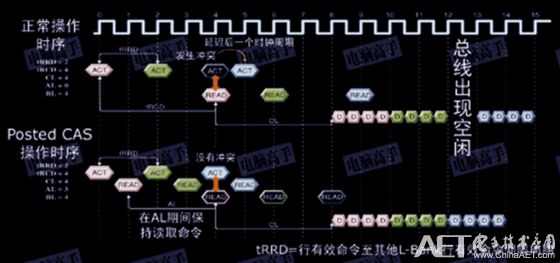

(2)Post CAS:它是為了提高DDR2內(nèi)存的利用效率而設(shè)定的;

在沒有前置CAS功能時,對其他L-Bank的尋址操作可能會因當前行的CAS命令占用地址線而延后,并使數(shù)據(jù)I/O總線出現(xiàn)空閑,當使用前置CAS后,消除了命令沖突并使數(shù)據(jù)I/O總線的利率提高。

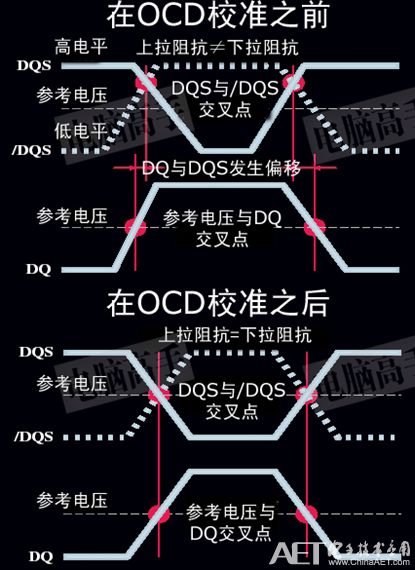

(3)OCD(Off-Chip Driver):離線驅(qū)動調(diào)整,DDR2通過OCD可以提高信號的完整性

OCD的作用在于調(diào)整DQS與DQ之間的同步,以確保信號的完整與可靠性,OCD的主要用意在于調(diào)整I/O接口端的電壓,來補償上拉與下拉電阻值,目的是讓DQS與DQ數(shù)據(jù)信號間的偏差降低到最小。調(diào)校期間,分別測試DQS高電平和DQ高電平,與DQS低電平和DQ高電平時的同步情況,如果不滿足要求,則通過設(shè)定突發(fā)長度的地址線來傳送上拉/下拉電阻等級,直到測試合格才退出OCD操作。

DDR3與DDR2的區(qū)別

1、DDR2為1.8V,DDR3為1.5V;

2、DDR3采用CSP和FBGA封裝,8bit芯片采用78球FBGA封裝,16bit芯片采用96球FBGA封裝,而DDR2則有60/68/84球FBGA封裝三種規(guī)格;

3、邏輯Bank數(shù)量,DDR2有4Bank和8Bank,而DDR3的起始Bank8個;

4、突發(fā)長度,由于DDR3的預期為8bit,所以突發(fā)傳輸周期(BL,Burst Length)也固定位8,而對于DDR2和早期的DDR架構(gòu)的系統(tǒng),BL=4也是常用的,DDR3為此增加了一個4-bitBurst Chop(突發(fā)突變)模式,即由一個BL=4的讀取操作加上一個BL=4的寫入操作來合成一個BL=8的數(shù)據(jù)突發(fā)傳輸,屆時可通過A112位地址線來控制這一突發(fā)模式;

5、尋址時序(Timing),DDR2的AL為0~4,DDR3為0、CL-1和CL-2,另外DDR3還增加了一個時序參數(shù)——寫入延遲(CWD);

6、bit pre-fetch:DDR2為4bit pre-fetch,DDR3為8bit pre-fetch;

7、新增功能,ZQ是一個新增的引腳,在這個引腳上接有240歐姆的低公差參考電阻,新增裸露SRT(Self-Reflash Temperature)可編程化溫度控制存儲器時鐘頻率功能,新增PASR(PartialArray Self-Refresh)局部Bank刷新的功能,可以說針對整個存儲器Bank做更有效的數(shù)據(jù)讀寫以達到省電功效;

8、DDR3的參考電壓分成兩個,即為命令與地址信號服務(wù)的VREFCA和為數(shù)據(jù)總線服務(wù)的VREFDQ,這將有效低提高系統(tǒng)數(shù)據(jù)總線的信噪等級;

9、點對點連接(point-to-point,p2p),這是為了提高系統(tǒng)性能而進行的重要改動。

總體比較

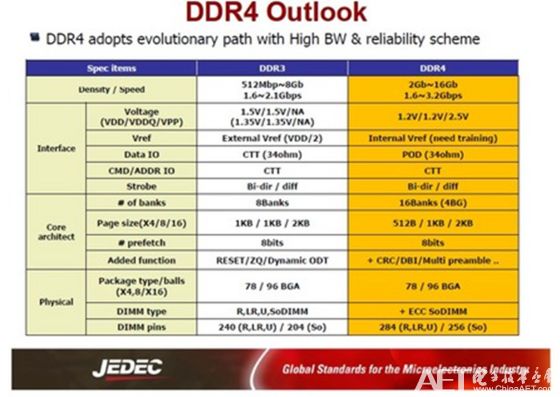

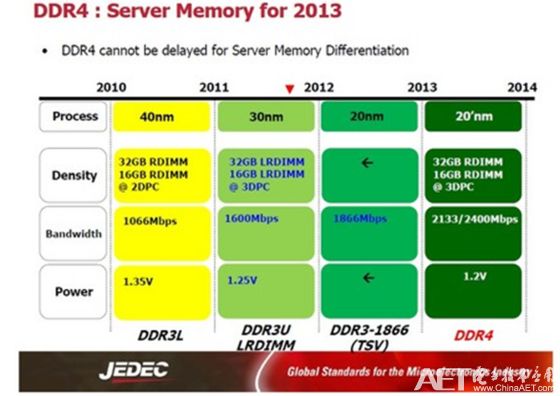

DDR4展望

-

芯片

+關(guān)注

關(guān)注

459文章

52414瀏覽量

439431 -

DDR

+關(guān)注

關(guān)注

11文章

732瀏覽量

66673

原文標題:【博文連載】DDR掃盲——DDR與DDR2、DDR3的區(qū)別

文章出處:【微信號:ChinaAET,微信公眾號:電子技術(shù)應(yīng)用ChinaAET】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

你知道DDR2和DDR3的區(qū)別嗎?

【小知識分享】SDR/DDR1/DDR2/DDR3的接口區(qū)別

【小知識分享】SDR/DDR1/DDR2/DDR3的接口區(qū)別

淺析DDR,DDR2,DDR3,DDR4,LPDDR區(qū)別

DDR2乏人問津 DRAM廠搶轉(zhuǎn)產(chǎn)能

DDR2,DDR2是什么意思

金士頓:DDR2/DDR3價格可能會繼續(xù)上漲

DDR2和DDR3內(nèi)存的創(chuàng)新電源方案

DDR2 Layout指導手冊

SDRAM,DDR3,DDR2,DDR4,DDR1的區(qū)別對比及其特點分析

DDR和DDR2與DDR3的設(shè)計資料總結(jié)

DDR,DDR2,DDR3,DDR4,LPDDR區(qū)別

評論