0 引言

基于光電掃描的坐標定位系統是近年來新興的一種坐標測量方法,具有精確度高、不易受周圍環境干擾等優點,因此在日本尼康公司生產的室內GPS(indoor GPS,iGPS)設備、天津大學精密測試技術及儀器實驗室研發的工作空間測量定位系統(workspace Measuring and Positioning System,wMPS)中都得到了廣泛的應用[1]。然而,基于光電掃描的定位系統對光脈沖信息處理要求的實時性極高,如何迅速并準確地將光脈沖信息轉變為電脈沖信息,并從中獲得相應光平面的信息,對保證系統的定位精度有著極為重要的意義。

本文基于Xilinx公司推出的Zynq-7000系列全可編程片上系統,采用ARM+FPGA架構的Zynq芯片,提出了一種新型的將光平面信息檢測與區分的方法,在FPGA中設計邏輯電路來實現對光平面的電脈沖信息捕獲與鎖存,并設計基于AXI總線協議的IP核,以此來對光平面信息進行高效的識別、處理與傳輸。

1 wMPS基本原理及信號采集模塊架構

1.1 wMPS工作基本原理

wMPS是一種新型的基于光電掃描的測量系統,其組成如圖1所示。

發射站向四周發射兩束掃描光以及一束同步光,接收器接收到光脈沖的信息并將其轉變為電脈沖,前端處理器接收電脈沖后將其按照周期進行區分,獲得其角度信息,并上傳給計算機最終完成坐標解算[2]。

當系統由兩臺及以上的發射站組成時,則可以使用類似經緯儀的測量原理來測量接收器在全局坐標系下的坐標[3]。其測量原理如圖3所示。

當空間內某一處的接收器Rx:(x,y,z)能同時接收到兩發射站Tx1以及Tx2的光信息時,在計算出接收器在每個發射站坐標系下的水平角α1、α2與垂直角β1、β2后,假設已知發射站的坐標為Tx1:(0,0,0)與Tx2:(x,0,0),則可通過如下公式計算接收器的坐標:

在大型測量網絡中,接收器常常會同時接收多個發射站的光信息,其光脈沖示意圖如圖4所示。為了利用光平面的信息解算出接收器的全局坐標,前端處理器需要記錄每一個電脈沖上升沿和下降沿到來的時間,以脈沖寬度來區分出同步光信號與掃描光信號[4],最終精確求解接收器的全局坐標。

1.2 前端處理器總體架構

前端處理器是wMPS測量系統的最重要的組成部分,它是系統安全、穩定、準確運轉的重要保證。如何將來自大尺寸空間中發射站的光信息如實地記錄與準確地區分,同時具有一定的擴容能力,對于整個wMPS系統是至關重要的。

基于Zynq芯片的wMPS前端處理器主要由兩部分組成:可編程邏輯(Programmable Logic,PL)部分和作為ARM控制的處理系統(Processing System,PS)部分。它們之間通過AXI總線進行通信,PL部分擅長做邏輯運算以及并行性強的任務,而PS部分擅長做串行以及控制偏多的任務[5]。因此在PL中設計邏輯電路來實現信號的采集與存儲,而PS 部分則負責后續對光平面脈沖的分類與處理,使得整個前端處理器的運算效率達到最大。基于Zynq的前端處理器架構如圖5所示。

2 信號采集模塊邏輯設計

在PL部分中的信號采集模塊劃分如下:

(1)光平面信息檢測與存儲部分。當光電接收單元接收到發射站的同步光信號和掃描光信號時,將轉化為相應的電脈沖傳遞給PL部分,PL部分通過3個狀態機將相應脈沖的上升沿、下降沿以及對應的時間記錄,并傳給FIFO進行保存。

(2)光平面信息傳輸接口部分。光平面的信息存儲在FIFO邏輯電路中,而PL部分與PS部分的通信基于AXI總線協議,因此需要設計相應的邏輯電路來實現信息的讀取與傳輸。

IP核是具有知識產權的集成電路芯核,是經過反復驗證的具有特定功能的模塊,與芯片制造工藝無關,可移植到不同的半導體工藝中。Xilinx公司提供了許多免費且功能強大的IP核給開發人員使用。在wMPS前端處理的PL部分設計中,也采用了許多Xilinx提供的IP核,這使得開發流程簡潔許多,并且正確性與可靠性得到了保證。其中測量同步控制模塊采用Xilinx提供的基于AXI總線的GPIO模塊,計數器采用Xilinx的二進制模塊,以及與上位機交互的通信模塊。因此關于這些部分本文不再進行討論,主要討論信號捕捉與計時存儲模塊以及基于AXI總線的FIFO接口模塊的IP核設計。

2.1 信號捕捉與計時存儲模塊

wMPS前端處理器PL部分最核心的工作就是對來自接收器的電脈沖進行捕捉以及鎖存時間值,其主要邏輯結構如圖6所示。通過3個協同工作的狀態機來分別完成捕捉邊沿信號、產生標志位以及鎖存時間值3個任務。

圖7所示為捕捉邊沿信號的狀態機狀態轉換圖。狀態機緩沖來自接收器的電脈沖信號,輸出Trig與Trig_n。Trig_En初始時為0,進入IDLE狀態。當開始測量時,Trig_En被置1,此時若輸入為0(IN=0),則進入REDY狀態。當IN為1時,進入上升沿狀態(POSEDGE_IN),Trig置1。一個時鐘周期后將Trig信號再拉低,進入等待(DELAY)狀態。等到IN為0時,再進入下降沿狀態(NEGEDGE_IN),此時將Trig_n拉高一個周期。再根據輸入IN的狀態進行判斷進入空閑狀態(IDLE)還是上升沿狀態(POSEDGE_IN)。

圖8所示為脈沖捕捉計時狀態機轉換圖,包含空閑(IDLE)、等待(WAIT)、捕捉(CAPT)3種狀態。當脈沖捕捉狀態機沒有接收到PS部分指令時,處于空閑狀態;當收到來自PS部分指令后,且脈沖捕捉狀態機處于非復位狀態時,跳轉至等待狀態;當Trig或者Trig_n輸出有一個為1時,進行信號捕捉,將FIFO寫使能信號置1,同時將30位計數器的時間值記錄下來,TP_Capt為計數器捕捉瞬間的時間值,將其寫入FIFO存儲。在工作狀態下(Trig_En=1&&Rst_n=1),每次時鐘上升沿到來時,若是Trig或Trig_n中有一個信號有輸入,則捕獲信號觸發的時間值(30位),并寫入FIFO,否則處于等待期間。

圖9為事件捕捉狀態機轉換圖,包含空閑(IDLE)、等待(WAIT)、上升沿(RIS)、延遲(DELAY)、下降沿(FAL)沿5種狀態。當接收到PS指令后,從空閑狀態跳轉至等待狀態,TP_Type保持上一狀態的信號。當來自邊沿信號捕捉狀態機的輸出Trig為1時,進入RIS狀態,TP_Type被標記為上升沿(01)。下一時鐘周期到來時對Trig_n的信號進行判斷,若為1,則TP_Type被標記為下降沿(10);否則TP_Type保持住,直到Trig_n信號為1時再標記為下降沿。而當狀態機位于下降沿狀態時,若下個周期Trig信號為1,則跳轉回上升沿狀態,TP_Type改變相應標記;否則狀態機跳轉回等待狀態,TP_Type繼續保持上一狀態。

2.2 基于AXI總線的FIFO接口模塊設計

為提高wMPS前端處理器的工作效率,本文基于AXI總線通信協議,定制FIFO的接口模塊,利用硬件邏輯控制讀取工作,縮短讀取時間來提高系統的工作效率。

圖10為FIFO接口模塊的內部結構,它包括以下幾部分:FIFO讀取邏輯、AXI總線接口以及多個控制寄存器。其中AXI總線接口是Xilinx公司提供的標準通信協議,該模塊在AXI總線與用戶邏輯之間提供雙向的接口[6]。模塊中有3個寄存器,其中寄存器0用來從AXI總線上接收指令,寄存器1與寄存器2分別用來存儲FIFO存儲的數據與FIFO的標志位數據。使用這樣的方式讀取FIFO中的數據,僅需2個時鐘周期即可完成,極大地提高了前端處理器的工作效率。

3 wMPS前端處理器PL部分邏輯仿真

為了驗證前端處理器PL部分的邏輯功能的完整性與可靠性,分別對設計的信號捕捉與計時存儲模塊以及基于AXI總線的FIFO接口模塊進行仿真驗證。

3.1 信號捕捉與計時存儲模塊仿真

使用Vivado提供的仿真器,輸入信號為隨機產生的寬度隨機的脈沖信號,觀察dout中讀出的數據以及相應的FIFO標志位,驗證設計的正確性。仿真波形如圖11所示。

由圖11可以清晰地觀察到,輸出的數據dout以及FIFO的標志位FIFO_Flag均在兩個時鐘周期后跳轉,即系統的延遲僅僅為兩個時鐘周期,滿足設計需求。

3.2 FIFO接口模塊仿真

由于FIFO接口模塊為基于AXI總線定制,若是直接仿真,不易滿足時序要求,因此使用Xilinx的ISE,利用總線仿真模型(Bus Function Model,BFM)對FIFO接口模塊進行仿真,通過FIFO端口寫入數據, 并從寄存器中讀取并觀察輸出信號。基于BFM的FIFO接口模塊仿真如圖12所示,可以觀察到,用戶IP可以正確輸出讀FIFO時序,兩個周期就可以讀出FIFO中的內容。因此從接收器檢測到脈沖信號到PS部分讀取電脈沖信息,僅需4個時鐘周期,延遲極小,滿足系統應用要求。

4 結論

本文提出了一種新型的將電脈沖信息檢測并區分的方法,基于Zynq芯片解決了室內定位系統中光脈沖信號難以區分的難題。仿真驗證表明,該設計的時鐘延遲極小,具有很高的精度,可以滿足現有wMPS系統對測量精度的要求,同時在其余基于光電掃描的室內定位系統中應用前景極高。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603024 -

ARM

+關注

關注

134文章

9087瀏覽量

367400 -

信號采集模塊

+關注

關注

0文章

6瀏覽量

7201

發布評論請先 登錄

相關推薦

關于OCT(光學相干斷層掃描)的Libview掃描控制和數據采集

激光掃描車身坐標測量數據采集系統的設計

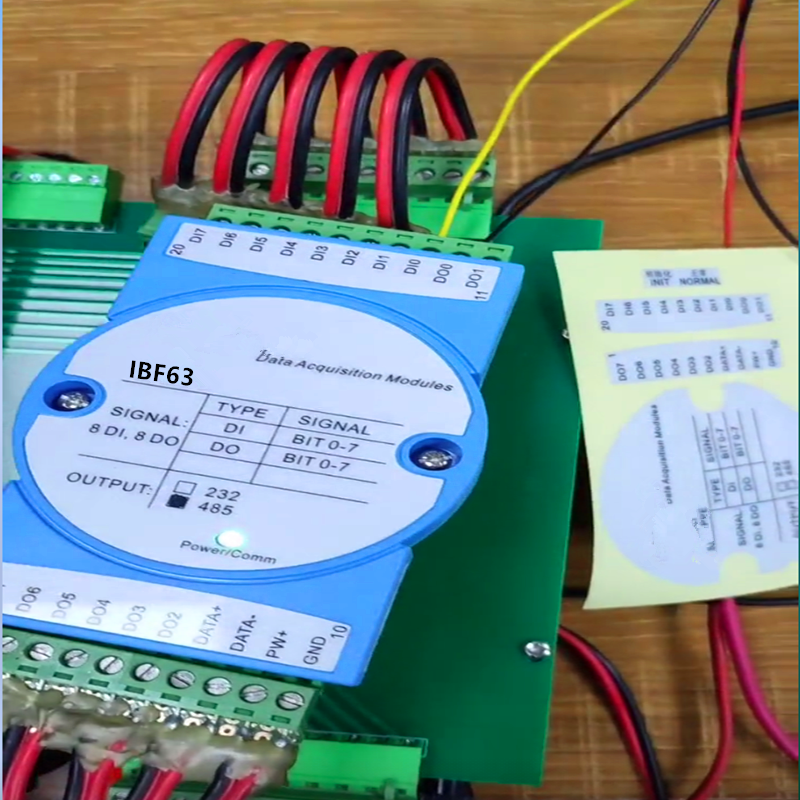

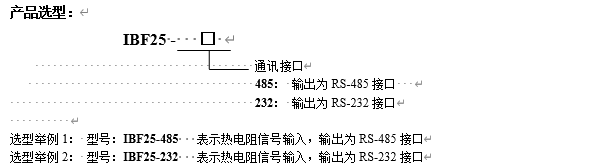

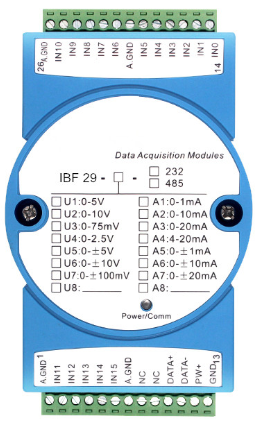

關于電壓模擬量的多類型信號采集模塊

振弦采集模塊主動上傳測量數據( UART)

脈沖計數電表、水表、煤氣表、光電開關采集模塊

關于光電掃描測量網絡信號采集模塊的設計

關于光電掃描測量網絡信號采集模塊的設計

評論