0 引言

高性能的模數(shù)轉(zhuǎn)換器(Analog Digital Converter,ADC)被廣泛應(yīng)用于通信、儀器儀表、計算機(jī)和醫(yī)療設(shè)備等領(lǐng)域,對國民經(jīng)濟(jì)、國防建設(shè)以及科學(xué)研究具有重要意義。單采樣單元的ADC芯片由于存在內(nèi)部熱噪聲、孔徑抖動和渡越時間不確定性等因素,面臨采樣速度和精度相互制約的影響,出現(xiàn)了瓶頸。而由多通道時間交織ADC(Time-Interleaved ADC,TIADC)采用M個相同型號的ADC單元依次交替完成采樣。理論上,TIADC的采樣率可以到達(dá)單ADC的M倍,同時保持采樣精度基本不變[1]。但是由于ADC采樣單元與外圍電路的個體差異,導(dǎo)致的采樣通道間不一致性會引起失配失真,如偏置誤差、增益誤差以及時間相位誤差將嚴(yán)重降低數(shù)據(jù)采集系統(tǒng)性能[2]。基于數(shù)字信號處理方法的數(shù)字后端修正技術(shù)可有效抑制以上失配造成的失真。近年來,已有文獻(xiàn)應(yīng)用FPGA實現(xiàn)數(shù)字后端修正技術(shù)。文獻(xiàn)[3]采用DSP與FPGA實現(xiàn)了4通道交織采樣速率達(dá)1G的采樣系統(tǒng),并對誤差進(jìn)行了補(bǔ)償。文獻(xiàn)[4]則設(shè)計了400 MS/s的2通道交織采樣系統(tǒng)。

本文提出并設(shè)計了一套4通道時間交織FPGA高速模擬信號采樣系統(tǒng)。系統(tǒng)的數(shù)據(jù)流控制、失配誤差數(shù)字修正等功能均在1片F(xiàn)PGA中實現(xiàn),無需額外采用DSP處理器,降低了系統(tǒng)的結(jié)構(gòu)復(fù)雜度。

1 TIADC系統(tǒng)方案

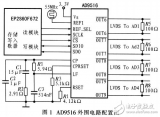

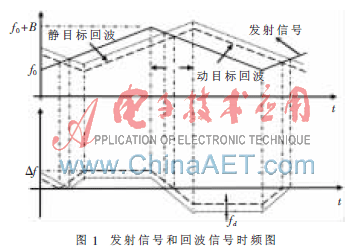

系統(tǒng)采用4塊8 bit、具有250 MS/s的AD9481模數(shù)轉(zhuǎn)換器通過時間交織采樣實現(xiàn)1 GS/s、8 bit的采樣系統(tǒng)。系統(tǒng)由功率分配與差分傳輸電路、ADC陣列、多相時鐘電路以及FPGA等構(gòu)成(如圖1所示)。模擬前端信號經(jīng)等功率拆分并轉(zhuǎn)換為差分信號傳輸至ADC陣列,4路ADC在多相時鐘驅(qū)動下對輸入信號并行交織模數(shù)轉(zhuǎn)換,產(chǎn)生的高速數(shù)據(jù)流交由FPGA實現(xiàn)緩存、修正并上傳到PC,完成顯示與性能評估。

1.1 ADC模擬前端信號處理

模擬輸入信號通過信號調(diào)理電路到達(dá)ADC采樣前端時,由于物理器件及結(jié)構(gòu)的不一致性帶來通道間的偏置誤差及增益誤差,將分別在頻域±kfs/M、±fin+kfs/M產(chǎn)生峰值雜散譜,其中k=1,2,…,M-1,導(dǎo)致信噪比降低[5]。采取對同一模擬信號進(jìn)行等功率拆分與差分傳輸方式進(jìn)行模擬前端信號處理。首先,選用SCP-4-1+功分器進(jìn)行輸入信號1:4拆分,在輸入信號帶寬為1~400 MHz情況下,功率拆分輸出4路信號相位失配最大僅為0.58°,并保證最大幅度失配小于0.15 dB。然后采用射頻變壓器ADT4-1WT+,設(shè)計了差分傳輸電路,其輸入輸出繞線比為4:1,具有一定的升壓作用。電路如圖2所示。

1.2 高精度多相時鐘設(shè)計

基于AD9516-3的時鐘合成方案可以實現(xiàn)高穩(wěn)定度的頻率合成與分頻,如圖3所示。由于時鐘產(chǎn)生單元的LVPECL通道分頻系數(shù)僅支持由1~32整數(shù)倍調(diào)節(jié),且信號延時的粗調(diào)Δt1~Δt4與PLL倍頻頻周期的最小單位有關(guān),為方便相位調(diào)節(jié),通過FPGA的控制邏輯SPI配置時鐘芯片的功能寄存器,對VCO分頻器進(jìn)行2分頻得到1 GHz信號,然后通道分頻器對該信號進(jìn)行4分頻,產(chǎn)生4路250 MHz相位不定的LVPECL時鐘信號。應(yīng)用由LC電路組成的可編程延遲線,通過控制延遲模塊電路中的DAC調(diào)節(jié)電容C以實現(xiàn)時鐘信號延遲控制得到4路時鐘信號的相位差分別為0°、90°、180°以及270°。

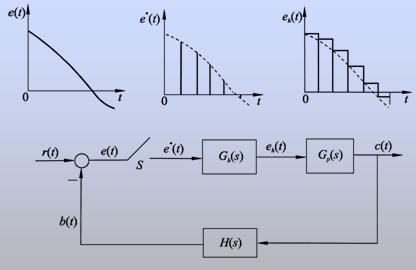

2 高速數(shù)據(jù)流緩存與處理

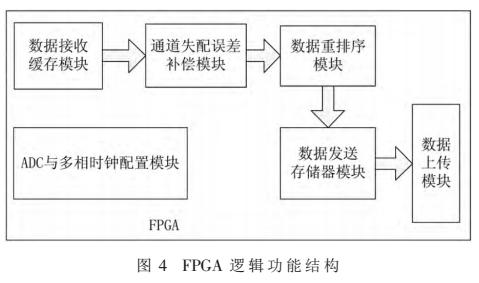

系統(tǒng)采用EP3C25Q240C6作為數(shù)據(jù)流處理單元,其邏輯功能包括由片內(nèi)RAM組成的異步FIFO緩沖模塊,以及對各通道ADC數(shù)據(jù)進(jìn)行失配誤差處理的修正模塊等。由于系統(tǒng)的輸入數(shù)據(jù)帶寬大于輸出數(shù)據(jù)帶寬,設(shè)計了數(shù)據(jù)發(fā)送緩沖存儲器實現(xiàn)數(shù)據(jù)上傳,最后利用剩余的邏輯資源例化一個邏輯分析儀模塊。邏輯功能結(jié)構(gòu)如圖4所示。

2.1 數(shù)據(jù)接收緩存與重排序

為實現(xiàn)異步時鐘域的數(shù)據(jù)接收,系統(tǒng)的接收模塊采用異步FIFO,采用ADC輸出的隨路時鐘DCO作為FIFO的寫時鐘。由于DCO輸出的相位與驅(qū)動ADC的多相輸入時鐘有關(guān),輸出的等相位差、多路隨路時鐘DCO_1+、DCO_2+、DCO_3+、DCO_4+、DCO_1-、DCO_2-、DCO_3-、DCO_4-按相位要求依次向FIFOA/B/C/D_P及FIFOA/B/C/D_N中寫入采樣數(shù)據(jù),其中寫請求在隨路時鐘上升沿觸發(fā)。為防止FIFO讀空或者寫滿,經(jīng)DCO_4-同步并發(fā)出寫請求后,等待FIFO半滿,發(fā)出FIFO讀請求,保證FIFO的容量始終保持在FIFO的中間狀態(tài),提高緩存的安全度,保證了重排序與聯(lián)合模塊輸出與采樣順序同步。

2.2 誤差修正

通道間的電路特性差異導(dǎo)致失配誤差,降低了無偽譜動態(tài)范圍等性能。選用第1通道為另外3條通道的參考通道。直流偏置誤差與增益誤差可以通過在需要修正的每條通道上增加一個加法器與乘法器進(jìn)行補(bǔ)償。補(bǔ)償前需要失配參數(shù)的測定。此模塊應(yīng)用文獻(xiàn)[6]提出的FFT方法消除以上3種誤差。剩下的時間失配誤差則應(yīng)用文獻(xiàn)[7]的頻率稀疏性方法進(jìn)行修正。由于修正補(bǔ)償方法不是本文的設(shè)計重點,更豐富的修正方法可以參考文獻(xiàn)[8]等。

2.3 采樣數(shù)據(jù)存儲與上傳

采用SignalTap II實現(xiàn)采樣信號重現(xiàn),并上傳PC。通過例化一個雙端口RAM作為發(fā)送數(shù)據(jù)存儲器,其深度為256,對應(yīng)于系統(tǒng)測試時每次獲取32 Kbit數(shù)據(jù)。數(shù)據(jù)發(fā)送存儲器通過判斷雙口RAM地址的大小來決定系統(tǒng)數(shù)據(jù)的發(fā)送或接收。發(fā)送存儲器初始化狀態(tài)時默認(rèn)為接收狀態(tài),地址為0,允許采樣處理后的數(shù)據(jù)寫入發(fā)送存儲器,同時禁能存儲器讀和數(shù)據(jù)上傳命令,當(dāng)發(fā)送存儲器滿,即地址為255時,禁能發(fā)送存儲器寫,同時使能存儲器讀和數(shù)據(jù)上傳命令。系統(tǒng)數(shù)據(jù)上傳流程如圖5所示。

3 TIADC系統(tǒng)實驗與測試

3.1 實驗測試條件與環(huán)境

實驗評測包括信噪比以及有效位分析等,方案如圖6所示。硬件測試用到信號發(fā)生器、示波器、信號源分析儀、穩(wěn)壓電源等設(shè)備。

3.2 性能測試評估

首先對單通道ADC性能測試,4路ADC分別對一個幅度為1 Vp-p、頻率為17 MHz的正弦波信號在250 MS/s采樣率下進(jìn)行采樣,分析得到4個單通道ADC的性能結(jié)果如圖7所示。測試的平均SNR達(dá)到44.93 dB,較AD9481官方參數(shù)降低1.07 dB;平均有效位達(dá)到7.17 bit,較官方參數(shù)降低0.33 bit,誤差控制在較低水平。

對輸入信號幅度1 Vp-p、頻率70 MHz的正弦波信號進(jìn)行1 GS/s的交織采樣,得到未進(jìn)行數(shù)字補(bǔ)償?shù)妮敵觥D8是SignalTap II抓取的時域波形,其對應(yīng)的頻譜圖如圖9所示。

顯然在位于頻率點250 MHz以及±70 MHz+250 MHz處出現(xiàn)峰值誤差雜散譜,與前面描述相吻合。通過在FPGA中應(yīng)用文獻(xiàn)[6,7]的誤差修正方法,得到輸出信號頻譜如圖10所示。修正使得信號的信噪比提高了18.7 dB,達(dá)到44.3 dB,有效位提高3.11 bit,達(dá)到7.06 bit。硬件引起的通道失配誤差保持在一個較低水平且是可控的。

為驗證系統(tǒng)工作的有效性,分別對0~250 MHz內(nèi)的正弦信號進(jìn)行采樣與數(shù)字后端通道失配誤差補(bǔ)償。系統(tǒng)采樣的性能參數(shù)如表1所示。隨著采樣信號頻率的升高,系統(tǒng)受信號抖動、時延以及ADC芯片本身存在的頻率特性等不確定因素影響增多,SNR與ENOB呈現(xiàn)下降趨勢,但保持在誤差可控范圍之內(nèi)。

4 結(jié)論

本文設(shè)計了一套FPGA處理交織采樣重構(gòu)與通道失配修正的高速采樣系統(tǒng)。通過失配誤差的數(shù)字后端補(bǔ)償,系統(tǒng)性能得到明顯提高。該系統(tǒng)能穩(wěn)定工作在1 GS/s采樣率下,平均信噪比達(dá)到44.1 dB,有效位達(dá)到7.03 bit。由系統(tǒng)硬件引起的通道失配誤差得到有效控制, 適用于數(shù)字失配修正補(bǔ)償方法的驗證與評估。

-

dsp

+關(guān)注

關(guān)注

553文章

7987瀏覽量

348757 -

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603009 -

adc

+關(guān)注

關(guān)注

98文章

6495瀏覽量

544467 -

信號采樣

+關(guān)注

關(guān)注

0文章

13瀏覽量

7125

發(fā)布評論請先 登錄

相關(guān)推薦

使用ADC12DJ3200做采樣系統(tǒng)時,發(fā)現(xiàn)SFDR受限于交織雜散,有什么方法降低Fs/2-Fin處的雜散?

設(shè)計時鐘采樣系統(tǒng)時有沒有最大限度減少抖動的辦法?

請問怎樣去設(shè)計時間交叉采樣系統(tǒng)?

高性能中頻采樣系統(tǒng)的設(shè)計與實現(xiàn)

USB接口技術(shù)在外置式采樣系統(tǒng)中的應(yīng)用

基于FPGA多通道采樣系統(tǒng)設(shè)計資料

基于FPGA的高速多通道AD采樣系統(tǒng)的設(shè)計與實現(xiàn)_徐加彥

AD9516高速四通道時間交叉采樣時鐘設(shè)計方案分析

基于4通道時間交織的FPGA高速模數(shù)轉(zhuǎn)換采樣系統(tǒng)

基于dsp防撞雷達(dá)信號采樣系統(tǒng)設(shè)計

AD7864:4通道、同步采樣、高速、12位ADC數(shù)據(jù)表

CN0157 24位、4通道、高動態(tài)范圍、每通道156 kSPS同步采樣數(shù)據(jù)采集系統(tǒng)

ADS8588S 16位、高速4通道、同步采樣ADC數(shù)據(jù)表

關(guān)于基于4通道時間交織的FPGA高速采樣系統(tǒng)的設(shè)計

關(guān)于基于4通道時間交織的FPGA高速采樣系統(tǒng)的設(shè)計

評論