首先舉一個例子:

早期的DDR(注:DDR2開始支持ODT功能),當向內存寫入數據時,如果只有一條內存,那么這條內存就自己進行信號的終結,終結電阻等效為150Ω。如果為兩條內存,那么他們會交錯的進行信號的 終結。第一個模組工作時,第二個模組進行終結操作,等第二個模組工作時,第一個模組進行終結操作,但等效電阻為75Ω。當有三條內存的時候,三條會交替進 行信號終結,但等效電阻為50Ω。對于省略終端電阻的DIMM(因為支持ODT,所以可以省略),也是同樣的道理。假設使用同步模式ODT,且終結電阻被設置為150Ω,當向內存寫入數據時,如果只有一個內存顆粒,那么這條內存就自己進行信號的終結,終結電阻等效為150Ω。

如果為兩個內存顆粒,那么他們會交錯的進行信號的 終結。第一個內存顆粒工作時,第二個內存顆粒進行終結操作,等第二個內存顆粒工作時,第一個內存顆粒進行終結操作,但等效電阻為75Ω。當有三個內存顆粒的時候,三個會交替進行信號終結,但等效電阻為50Ω。

這樣一來,信號完整性就會受到不同程度的影響,為了能夠保持等效電阻一致,我們希望ODT的RTT(終結電阻)是可以動態修改的,而不需要每次都要通過MRS Command進行修改。這就是接下來要介紹的動態ODT模式。

當MR2寄存器中的A9和A10位被置位為1,動態ODT模式將會被啟用。具體的功能描述如下:

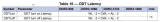

? Two RTT values are available: RTT_Nom and RTT_WR.– The value for RTT_Nom is preselected via bits A[9,6,2] in MR1.– The value for RTT_WR is preselected via bits A[10,9] in MR2.? During operation without write commands, the termination is controlled as follows:– Nominal termination strength RTT_Nom is selected.– Termination on/off timing is controlled via ODT pin and latencies ODTLon and ODTLoff.? When a write command (WR, WRA, WRS4, WRS8, WRAS4, WRAS8) is registered, and if DynamicODT is enabled, the termination is controlled as follows:– A latency ODTLcnw after the write command, termination strength RTT_WR is selected.– A latency ODTLcwn8 (for BL8, fixed by MRS or selected OTF) or ODTLcwn4 (for BC4, fixed by MRS

or selected OTF) after the write command, termination strength RTT_Nom is selected.– Termination on/off timing is controlled via ODT pin and ODTLon, ODTLoff.

需要注意的是,動態ODT并不支持DLL-off模式,用戶必須通過設置MR2{A10, A9}={0,0},來禁用動態ODT功能。

由于時序圖比較長,為了防止圖像壓縮后變得不清晰,所以改成了pdf文件的形式。

DynamicODT.pdf

異步ODT功能因為使用的頻率較低,此處不再詳細介紹。

-

電阻

+關注

關注

87文章

5659瀏覽量

175810 -

DDR

+關注

關注

11文章

735瀏覽量

67108 -

信號完整性

+關注

關注

68文章

1458瀏覽量

96949

原文標題:【博文連載】DDR3中的ODT動態模式詳解

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

DDRx的關鍵技術介紹(中)

Q [17:0]和CQ輸出需要FPGA/ASIC端的ODT嗎?

DDR3 ZQ校準簡單介紹

淺析DDR3?ODT

動態ODT功能

關于ODT與驅動強度的相關知識介紹

ODT在手,DDR5布線可以任性走?

什么是動態同步傳輸模式

聊一聊ODT的幾種操作模式

什么是ODT,它是怎么工作的?

動態Sql介紹

動態無功補償裝置的三種運行模式

評論