接下來,我們來看看阿里云對它進行了怎樣的改造。

阿里云ECS的異構計算團隊和高性能計算團隊一直致力于將計算資源"平民化";高性能計算團隊在做的E-HPC就是要讓所有云上用戶都能夠瞬間擁有一個小型的超算集群,使得超算不再僅僅是一些超算中心和高校的特權;而我們異構計算團隊則致力于將目前最快、最新的計算設備在云上提供給用戶,使得曾經高冷的計算資源不再拒人千里之外:我們推出了FPGA云服務器FaaS 服務, 其中的F1和F2實例已經對外提供服務,可以通過一鍵部署的方式把Intel和Xilinx的小規格的器件計算能力賦予客戶。

今天我們很高興地宣布:新晉的大規格FPGA實例,基于Xilinx 16nm Virtex UltraScale+ 器件VU9P的異構計算實例F3在阿里云上線了!

我們借此機會,對阿里云FPGA計算服務(下面簡稱FaaS)本身,以及這次發布的F3實例的底層硬件架構和平臺架構做一個技術解讀。

FaaS阿里FPGA云服務器平臺FaaS(FPGA as a Service)在云端提供統一硬件平臺與中間件,可大大降低加速器的開發與部署成本。加速器開發商的加速器可以形成服務提供給加速器用戶,消除加速技術與最終用戶的硬件壁壘。用戶則能夠在無需了解底層硬件的情況下,直接按需使用加速服務。

為了給加速器提供方和使用方提供更加高效、統一的開發及部署平臺,FaaS提供兩大套件:HDK和SDK。

HDK給所有的加速器開發者提供統一的FPGA硬件接口,提前幫用戶解決了FPGA開發中難度最大的高速接口開發及調試,例如PCIe、SERDES接口、DDR控制器等等;使得用戶能夠直接得到硬件平臺和FPGA接口的最大性能,不會因為團隊開發能力和經驗的欠缺,造成硬件平臺性能浪費;高效、可靠、統一的接口套件也為云上平臺的安全隔離、設備穩定提供了保障,不會因為用戶的接口設計問題,造成服務器宕機;同時可以杜絕用戶在FPGA端對主機的非法操作,為整個云上安全提供保障。

HDK包括兩個部分,Shell和 Role;Shell部署在靜態區域,提供上述統一接口部分。

在提供統一接口、安全性和便捷性的前提下,阿里云FaaS HDK 也盡最大的努力保證用戶設計的靈活性,Role的概念應運而生。Role部署在動態區域,是在Shell之外,預先開發并提供的,用戶可以配合用戶邏輯(Customer Logic)使用。不同于Shell,用戶可以根據需要,隨時更換Role部分;這種Shell + Role的組合方式,保證了Shell的最輕量化和穩定性,又兼顧了統一性、便捷性和靈活性。

SDKSDK包括兩個部分:

-

和HDK(Shell+Role)對應的主機端驅動(Drivers)和軟件庫(Libraries)

-

FPGA管理工具 faascmd套件

驅動和軟件庫和HDK的Shell以及Role相對應,和HDK一起,為用戶提供統一及靈活的軟件支持,比如DMA驅動、寄存器訪問驅動等等。

faascmd工具套件為用戶提供云上FPGA管理服務,包括安全校驗、FPGA鏡像生成、下載及管理、FPGA加速卡狀態查詢反饋等功能。公有環境使用FPGA,需要考慮用戶FPGA文件的安全,faascmd提供的秘鑰及OSS bucket指定機制,有效保證了用戶的FPGA下載文件的私密性。在線下的開發及應用中,開發者直接對FPGA進行下載操作,但在云上環境,用戶對公有的FPGA資源直接操作對安全造成較大影響。Faascmd工具會對用戶操作申請和物理FPGA資源進行隔離,保證了用戶下載安全的同時,提供給用戶類似線下操作的體驗;同時會對用戶提交的網表進行校驗,提高安全、降低風險。faascmd同時也提供調用接口,用戶能很容易地在自己的App中調用管理工具,結合自身加速器特性實現各種管理功能。

FaaS 的IP市場FaaS降低了FPGA開發者的開發準入門檻:云上即開即用的FPGA資源、靈活的付費模式使得硬件資源觸手可及;同時簡化了開發流程,統一了開發接口,把核心加速邏輯從周邊硬件設備的接口調試中隔離出來,使得FPGA的新興應用可以只關注業務加速的核心邏輯,快速迭代;在這兩點上,阿里云的FaaS 邁出了FPGA計算資源平民化的第一步。

但即便是大大簡化了開發流程、提供了觸手可及的硬件資源,FPGA依然有一定的開發門檻。如何把已有的FPGA 邏輯IP價值最大化,聯通FPGA加速的需求方和提供方來擴大生態呢?重要的一點就是如何解決在公共云數據中心層面保證FPGA加速IP的安全性,特別是對不可信的第三方進行輸出和部署這個難題, FaaS是如何解決這個問題的呢?

答案是通過阿里云FaaS的IP市場。技術上,通過與Xilinx聯合開發的定制虛擬化技術達到IP加速與部署環境的強隔離,IP的用戶與IP的網表文件完全隔離,網表文件的傳輸、部署、加速流程全程對用戶都不可見;同時加速計算能力又可以透明地向使用該IP的第三方用戶開放,這是阿里云在FPGA云上加速服務的另外一個技術創新。這個創新,完全杜絕了FPGA IP在云上輸出的時候被盜版的可能,提供了非常高的安全保護機制。

更加嚴格的保密機制也在規劃中:很快可以通過阿里云的KMS加密服務對IP進行加密保護,每次對IP加載前都需要向KMS服務獲取秘鑰解密,這樣一來針對IP的使用下載有據可查;并且使得IP發布方的IP在數據中心內部都是安全的,因為沒有了IP提供方的KMS秘鑰,即便是阿里云也無法對加密的網表進行解密操作。

在阿里云FaaS IP 市場的幫助下,即便是從來沒有任何FPGA開發經驗的用戶,也可以一鍵從IP市場中獲取相應的加速邏輯,并快速部署到對應的FPGA器件上面去。我們相信,通過即開即用的硬件資源、統一的軟硬件邏輯開發接口和IP市場,阿里云能夠真正兌現FPGA計算資源平民化的承諾。

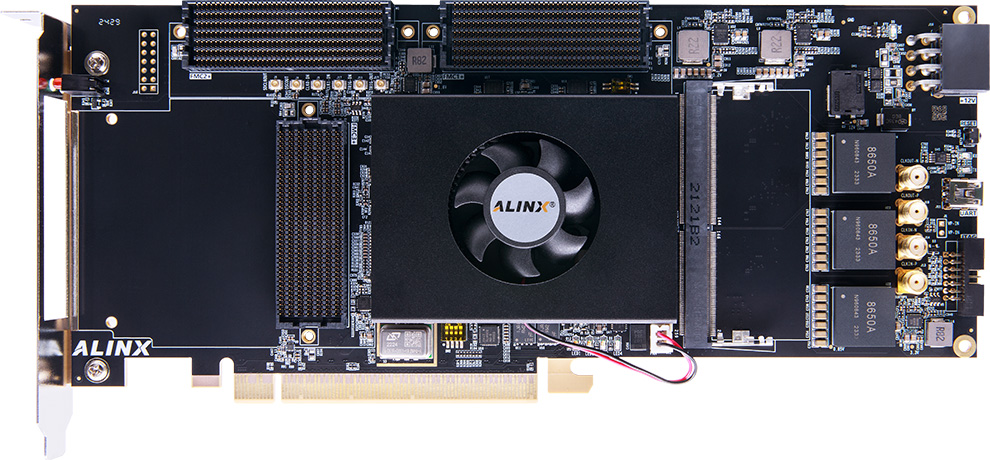

F3硬件架構阿里云FaaS的F3實例在底層硬件上,是使用阿里云自主研發的高性能單卡雙芯片的VU9P的板卡。這里要劃重點啦:單卡雙芯片。一定有用戶要問為什么要這么設計呢?單卡雙芯片的硬件設計有什么好處呢?

首先,對于用戶來說,通過單卡雙芯片這樣的規格設計,與阿里云配套自研的服務器一起,最高可以提供單實例16 塊 VU9P的計算實例。16塊 VU9P是非常高的計算密度了,這是設計單卡雙芯片的第一個目的:通過提高計算密度,在同等計算單元下集成了更多的加速芯片,能夠有效降低單位計算力的成本,從成本大幅降低和單位實例的垂直計算力提升上,客戶可以雙重受益。

單卡雙芯片的兩個VU9P芯片通過PCIe 橋接入系統,那么雙芯片之間的互相通信呢?是不是只能通過PCIe的總線來進行呢,答案是否定的,除了FPGA Direct這種通過PCIe互相通信的能力之外,在阿里云的自研的板卡上也是有特殊考慮的。在兩個芯片之間,我們設計了一個高速互聯通道,使得兩個FPGA之間可以通過這個特殊的通道以高達600Gb/s的速率進行通信,這個通信技術我們稱之為FPGA Link。要知道,現在的數據中心主流部署的接入交換機光口通信也只能達到100Gb/s的通信速率,更高的200Gb/s的交換機還在試部署中。

試想一下,無需額外的交換機和光口硬件,兩個FPGA芯片可以通過FPGA Link技術以超短時延通過6倍于主流光口通信的速率進行通信,這個將會以極低的成本幫助用戶開啟大量新的FPGA加速應用模式。比如,小規模的芯片仿真,需要兩個器件才能部署得下的情況,可以將整體仿真模塊拆解之后部署到兩個芯片上,兩個芯片之間的數據通路和同步信號通過高速通道互聯;還有其他的應用場景,需要把功能模塊部署到兩個FPGA芯片之上,而兩者之間需要大量的數據交換,比如視頻轉碼場景:把小規模但是模塊數目比較多的解碼單元、視頻處理單元部署到一個FPGA之上,把面積占用比較多的編碼單元放到另外一個FPGA上,編解碼模組之間通過高速互聯交換裸視頻流。這將大大改善部署的難度,以及極大的解耦兩個模塊之間的相互依賴和設計難度。以上舉了兩個例子,讀者一定能夠舉一反三地想到,其他需要流水線處理并需要大量數據交換的場景,阿里云的F3實例的雙芯片實例能夠為客戶提供最大的價值。

不少應用場景對板載的DDR存儲還是有要求的。阿里云的F3實例,為每個FPGA搭配了客戶可見的64GB的DDR內存,這64GB的DDR分成4個通道,分別連接到VU9P的3個硅單元上面,其中一個通道對應的16GB DDR保留常駐,其余3個通道對應的48GB存儲以可選的方式可被客戶邏輯加載使用。

目前,我們看到了雙芯片實例除了FPGA Direct技術和高達600Gb/s的FPGA Link高速互聯能力之外,另外值得一提的是:雙芯片的實例與其他的雙芯片實例板卡之間也可以通過400Gb/s的光口進行互聯,而且400Gb/s的以太協議驅動是通過Xilinx預置的MAC硬核來加速,不占用邏輯面積;通過以太或者自定義的輕量級通信協議,能夠在16芯片之間,以及更多的芯片之間搭建2維Mesh或者環形互聯,進一步擴展多片互聯的使用模式和應用場景。

最后,上一張圖,讓大家對上面做的硬件的技術解析有一個更具體的認識:

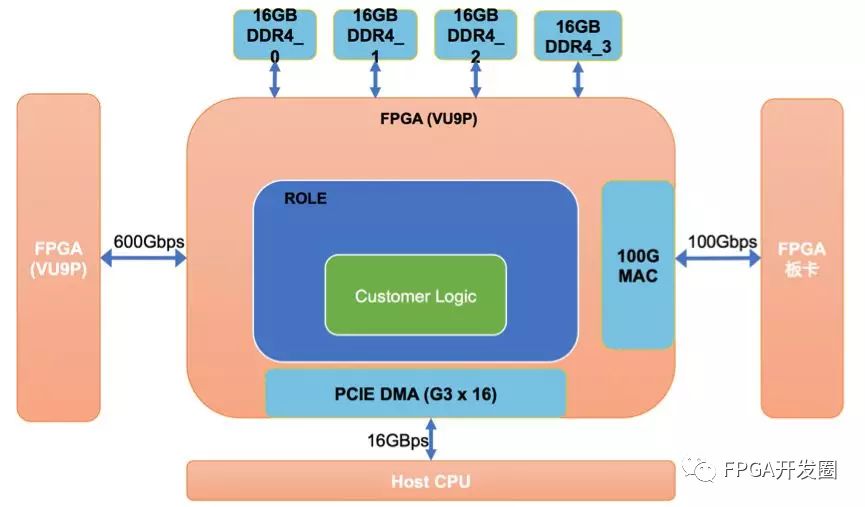

F3邏輯結構,技術分析之前,先給大家上一幅邏輯架構圖:

★SHELL:

Shell是FPGA的靜態區域,內部包含用戶PCIe、管理PCIEe、板卡管理系統和一個DDR訪問通道。為了提高板卡的安全和穩定性,用戶無權修改SHELL區域。

★ROLE:

我們在設計中提出了Role的概念,Role和Shell是類似的封裝。而Role跟Custom Logic一起在動態區域。Role的提出使我們可以更加輕量化Shell。我們通過Role實現了同一個Shell既可以支持OpenCL開發,也可以支持RTL開發;最后就是Role的再次抽象降低了用戶對于FPGA的開發門檻。我們提供基礎的Role,也允許用戶自行設計Role。我們希望更多第三方的設計者通過分享自己Role,使得FaaS平臺更加精彩。

ROLE內部結構簡介Interconnect:該部分主要是提供給用戶四路DDR通道的訪問和USER_PCIe對四路DDR通路的訪問。 該模塊幫助用戶隔離了時鐘域,使用戶邏輯在同一個時鐘域上對4路DDR通道進行訪問。

Inter chip interconnect: FPGA 單卡雙芯片間互聯通路;

Card interconnect: FPGA 卡間互聯通路;

Custom Logic:用戶自定義邏輯部分;

Custom Logic介紹用戶邏輯是屬于Role的一部分,屬于動態加載區域。 為了方便用戶標準化使用,我們在RTL設計中使用了標準的AXI-4和AXI-LITE接口。

1.我們將詳細介紹用戶接口,其列表如下:

|

接口 |

Name |

Direction |

Clock Domain |

Description |

|

時鐘和復位 |

I |

/ |

寄存器通路時鐘50Mhz |

|

|

sys_alite_aresetn |

I |

|||

|

usr_clk |

I |

用戶時鐘,300Mhz,該時鐘固定不可配置 |

||

|

usr_rstn |

I |

|||

|

kernel_clk_300m |

I |

用戶時鐘,300Mhz,該時鐘固定可配置 |

||

|

kernel_clk_rstn |

I |

|||

|

kernel2_clk_500m |

I |

用戶時鐘,500Mhz,該時鐘固定可配置 |

||

|

寄存器通路 |

AXI_LITE |

sys_alite_aclk |

axi4_alite接口,用戶寄存器傳輸,地址空間0x0~0x7fffff |

|

|

DDR AXI4 |

C0_sys_axi* |

/ |

kernel_clk_300m |

dimm0 數據交互訪問接口(base addr:0x0000_0000_0000_0000) |

|

C1_sys_axi* |

/ |

dimm0 數據交互訪問接口(base addr:0x0000_0004_0000_0000) |

||

|

C2_sys_axi* |

/ |

dimm0 數據交互訪問接口(base addr:0x0000_0008_0000_0000) |

||

|

C3_sys_axi* |

/ |

dimm0 數據交互訪問接口(base addr:0x0000_000c_0000_0000) |

||

|

Dma AXI4 |

Dma_axi_* |

/ |

kernel_clk_300m |

用戶邏輯直接dma訪問通路 |

|

Interrupt |

usr_int_en |

I |

kernel_clk_300m |

中斷使能 |

|

usr_int_req |

I |

中斷請求,最大支持16個中斷 |

||

|

usr_int_ack |

O |

中斷應答 |

||

|

錯誤檢測 |

ddr_cal_done |

I |

kernel_clk_300m |

|

|

dma_4k_r_err_flag |

I |

|||

|

dma_4k_w_err_flag |

I |

注:板間互聯,卡卡互聯接口邀測階段缺省不提供,需要特殊申請對外開放。

2.AXI-4 and AXI-Lite 限制

|

AxBURST |

Only INCR burst is supported. |

|

AxLOCK |

Lock is not supported. |

|

AxCACHE |

Memory type is not supported |

|

AxPROT |

Protection type is not supported |

|

AxQOS |

Quality of Service is not supported |

|

AxREGION |

Region identifier is not supported |

3. 正如我們在介紹Role中所述,用戶可以定制化Role操作。我們阿里云FaaS團隊為了方便用戶更有效的使用平臺,多個Role版本正在發布中,敬請關注。降低用戶使用門檻,縮短開發時間,健全FPGA使用生態始終是我們的使命。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

602986 -

加速器

+關注

關注

2文章

796瀏覽量

37839 -

Xilinx

+關注

關注

71文章

2167瀏覽量

121303

原文標題:如何將FPGA資源平民化?阿里工程師有了新突破

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ALINX 發布 AXVU13P:AMD Virtex UltraScale+ 高端 FPGA PCle 3.0 綜合開發平臺

【一文看懂】什么是異構計算?

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評估套件

為兩個Xilinx(TM)LX240 Virtex-6(TM)器件供電

打造異構計算新標桿!國數集聯發布首款CXL混合資源池參考設計

AvaotaA1全志T527開發板AMP異構計算簡介

異構計算:解鎖算力潛能的新途徑

中高端FPGA如何選擇

中國臺灣將資助當地16nm以下芯片研發 最高補貼50%

AMD推出全新Spartan UltraScale+ FPGA系列

基于Xilinx 16nm Virtex UltraScale+器件VU9P的異構計算實例

基于Xilinx 16nm Virtex UltraScale+器件VU9P的異構計算實例

評論