在FPGA設(shè)計過程中,使用好雙口RAM,也是提高效率的一種方法。

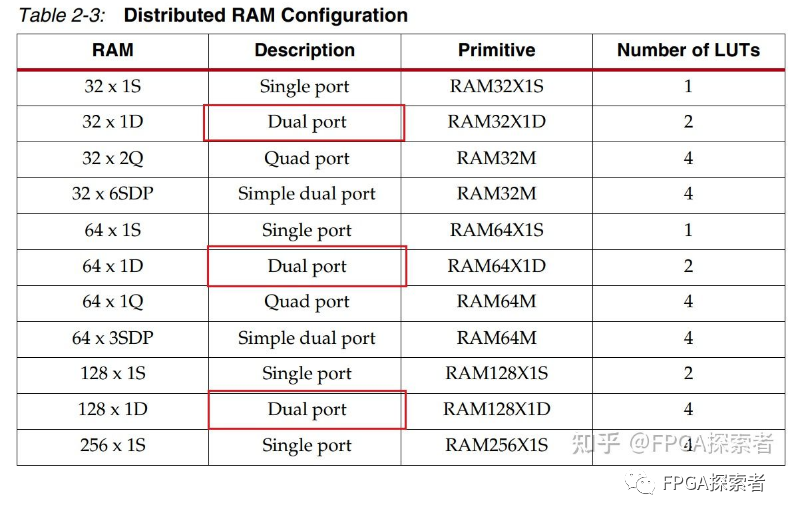

官方將雙口RAM分為簡單雙口RAM和真雙口RAM。

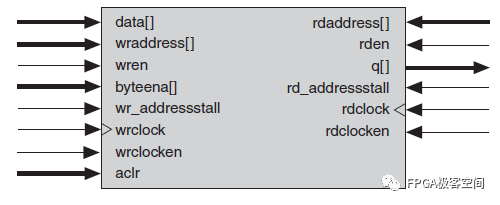

簡單雙口RAM只有一個寫端口,一個讀端口。

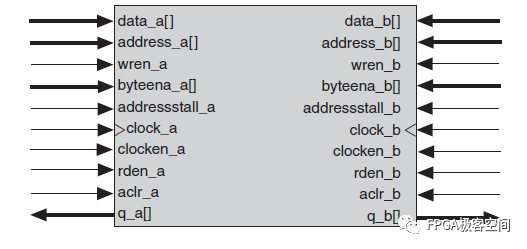

真雙口RAM分別有兩個寫端口和兩個讀端口。

無論是簡單雙口RAM還是真雙口RAM,在沒有讀操作的情況下,應(yīng)將讀使能rden信號拉成低電平,節(jié)省功耗。

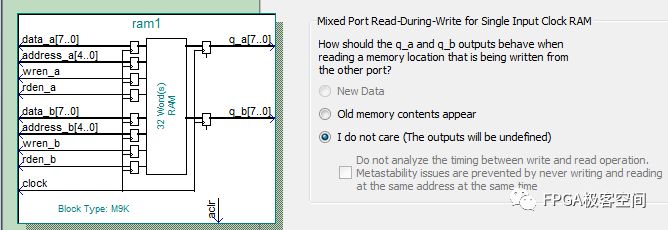

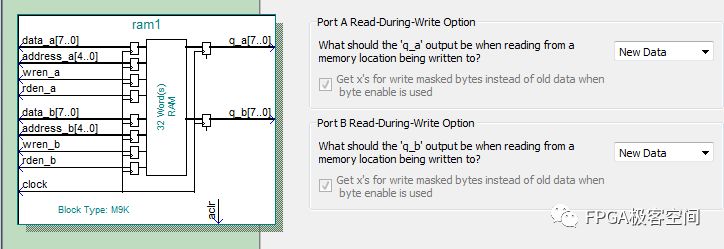

在兩種情況下,都應(yīng)當(dāng)避免read-during-write,雖然可在軟件中進(jìn)行設(shè)置,但是,作為設(shè)計者,應(yīng)當(dāng)盡量避免此種情況。

對于真雙口RAM,還應(yīng)當(dāng)避免兩個讀端口或者兩個寫端口同時操作同一個地址,RAM中并沒有此種沖突解決電路,設(shè)計者應(yīng)該避免這種沖突。

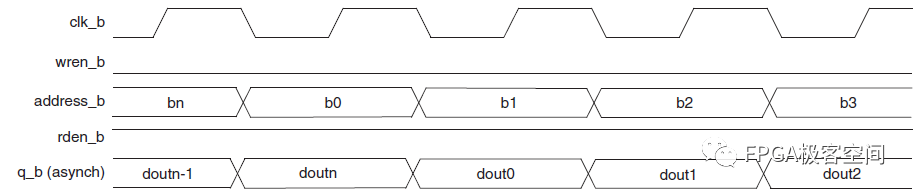

無論是那種雙口RAM,讀時序圖是相同的。

當(dāng)讀使能有效時,數(shù)據(jù)會在時鐘下一個上升沿從Q端輸出。

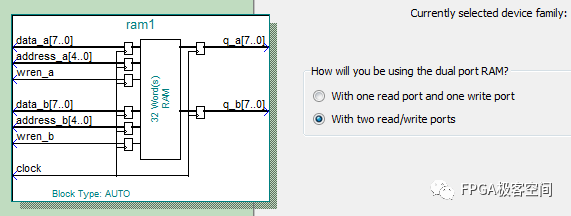

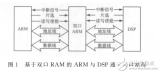

真雙口RAM給設(shè)計帶來很多便利。在高速存儲中,需要對連續(xù)的數(shù)據(jù)同時處理,使用簡單雙口RAM只能讀取一個數(shù)據(jù),而使用真雙口RAM可以同時讀取兩個數(shù)據(jù),這樣明顯提高讀取速度以及處理速度。

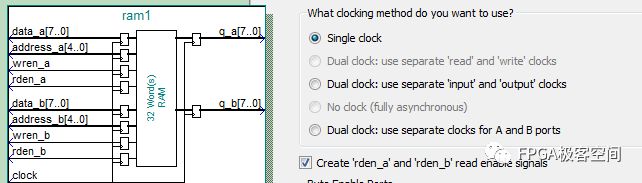

調(diào)用真雙口RAM,如圖設(shè)置。

這里可以設(shè)置時鐘方案,而讀使能rden并非必須信號。當(dāng)使用rden信號時,此信號高電平有效,當(dāng)不使用rden信號時,給定地址,下一個脈沖數(shù)據(jù)從q端口送出。

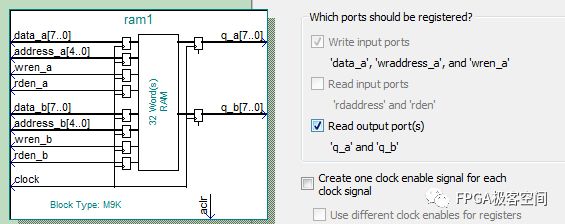

這里的設(shè)置非常重要,當(dāng)選中read output ports時,q端會增加一級寄存器。雖然這樣增加流水線能夠提高電路的速度,但同時從讀使能有效到最終數(shù)據(jù)有效將會多延遲一個時鐘周期。在設(shè)計中要格外注意。根據(jù)設(shè)計自行設(shè)置。

上面兩張圖是指定對同一地址操作時的輸出。作為設(shè)計者,應(yīng)盡量在自己的設(shè)計中避免這種情況發(fā)生。

真雙口RAM用好了是非常省時間的。之前我們文章中提到硬件FFT的實現(xiàn),在實現(xiàn)過程中,使用基2的設(shè)計方案,需要同時讀取兩個RAM數(shù)據(jù),這種情況下可以使用真雙口RAM提高效率。

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603013 -

RAM

+關(guān)注

關(guān)注

8文章

1368瀏覽量

114647 -

電平

+關(guān)注

關(guān)注

5文章

360瀏覽量

39883

原文標(biāo)題:雙口RAM,值得研究

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

利用FPGA實現(xiàn)雙口RAM的設(shè)計及應(yīng)用

基于FPGA的雙口RAM實現(xiàn)及應(yīng)用

求助,雙口RAM選型!

FPGA雙口ram

基于FPGA的雙口RAM實現(xiàn)及應(yīng)用

數(shù)據(jù)采集系統(tǒng)中用SRAM模擬雙口RAM

Xilinx分布式RAM和塊RAM—單口、雙口、簡單雙口、真雙口的區(qū)別

RAM分為簡單雙口RAM和真雙口RAM

RAM分為簡單雙口RAM和真雙口RAM

評論