JESD204B是什么

JESD204B是一種新型的基于高速SERDES的ADC/DAC數(shù)據(jù)傳輸接口。隨著ADC/DAC采樣速率的不斷提高,數(shù)據(jù)的吞吐量也越來越大,對于500MSPS以上的ADC/DAC,動輒就是幾十個G的數(shù)據(jù)吞吐率,而采用傳統(tǒng)的CMOS和LVDS已經(jīng)很難滿足設計要求,這個時候,JESD204B應運而生。現(xiàn)在各大廠商的高速ADC/DAC上基本都采用了這種接口。

使用JESD204B接口的原因

? 不用再使用數(shù)據(jù)接口,時序控制簡單

? 不用擔心信道偏移

? 不用再使用大量IO口,布線方便

? 多片IC同步方便

?減少了PCB布板空間

?減小了器件的引腳和封裝大小

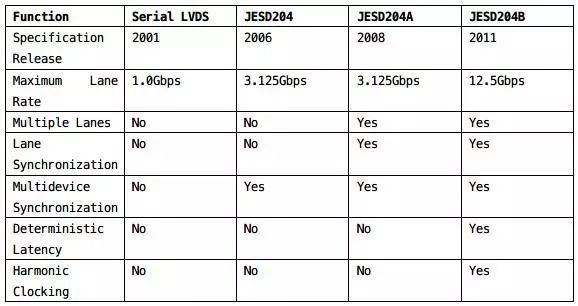

JESD204B與其他接口的對比表

JESD204B種類

JESD204B包括3個子類,分別是子類0,子類1,子類2。三個子類主要是根據(jù)同步方式的不同劃分的。子類0兼容JESD204A,子類1使用SYSREF同步,子類2使用SYNC進行同步。只有子類1和子類2支持確定性延遲——發(fā)送端到接收端之間的鏈路延遲固定。

分層規(guī)范

大部分的ADC和DAC都支持子類1,JESD204B標準協(xié)議中子類1包括:傳輸層,鏈路層,物理層。在少部分資料中也會介紹含有應用層,應用層是對JESD204B進行配置的接口,在標準協(xié)議中不含此層,只是為了便于理解而添加的一個層。傳輸層負責將采樣數(shù)據(jù)映射為數(shù)據(jù)幀。鏈路層負責鏈路的建立,數(shù)據(jù)傳輸。物理層負責數(shù)據(jù)的發(fā)送和接收。

01

傳輸層

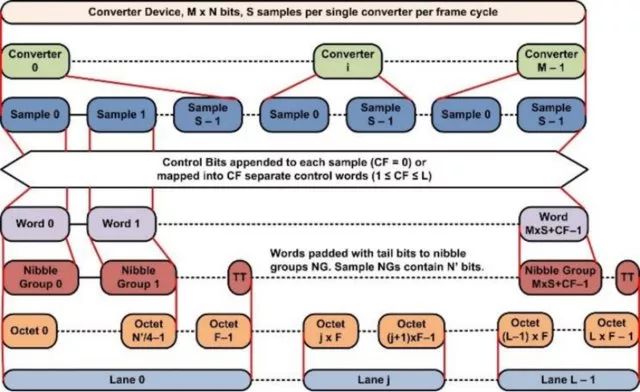

數(shù)據(jù)傳輸層的主要功能將AD轉(zhuǎn)換器采樣的數(shù)據(jù)映射成8bit位寬的字節(jié)數(shù)據(jù)。先將所有的采樣數(shù)據(jù)線性的排開,然后添加控制字和控制位得到words,也可以選擇不加控制字和控制位,則words和之前排列的采樣數(shù)據(jù)相同,添加控制字和控制位有兩種方法,第一種在每一個采樣點的末尾添加控制位;第二種不在采樣點末尾添加控制位,在所有采樣點的末尾添加一個控制字,控制字里面的控制位對應前面的采樣點。通過添加tail將words進行擴展,使每一個word的位數(shù)為N位,這個值是4的倍數(shù),控制字不需要擴展。最后將數(shù)據(jù)劃分得到L*F個字節(jié),對應L個通道。

02

鏈路層

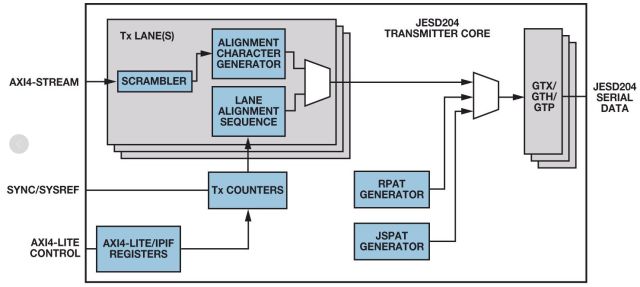

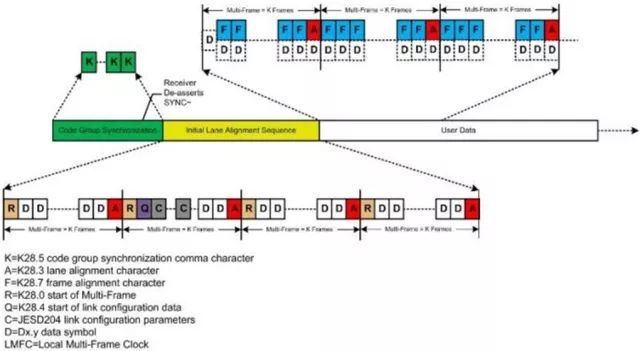

鏈路層主要包括擾碼器加擾,鏈路建立,8b/10b編碼三部分。鏈路建立主要包括代碼組同步(CGS),初始通道對齊序列(ILAS),用戶數(shù)據(jù)。

03

物理層

在物理層中,數(shù)據(jù)進行串行化,8B/10B編碼數(shù)據(jù)以線路速率發(fā)送和接收。物理層包括串行/解串器(SERDES)模塊、驅(qū)動器、接收器和CDR。由于數(shù)據(jù)傳輸速率非常高,這些模塊常常采用定制單元設計。JESD204和JESD204A均支持最高3.125 Gbps的速度。JESD204B規(guī)范支持三種可能的速度等級。速度等級1支持最高3.125 Gbps的速度,基于OIF-SxI5-0.10規(guī)范。速度等級2支持最高6.375 Gbps的速度,基于CEI-6G-SR規(guī)范。速度等級3支持最高12.5 Gbps的速度,基于CEI-11G-SR規(guī)范。

JESD204B缺點

JESD204B也有其不足之處,首先是增加了接口的傳輸延時,其次是其需要特殊的時鐘電路導致更復雜的電路設計。

關于JESD204B串行接口時鐘需求及其實現(xiàn)方法敬請關注下期文章。

-

adc

+關注

關注

99文章

6527瀏覽量

545276 -

物理層

+關注

關注

1文章

152瀏覽量

34456 -

JESD204B

+關注

關注

5文章

76瀏覽量

19154

原文標題:五分鐘讓你認識JESD204B

文章出處:【微信號:gh_873435264fd4,微信公眾號:FPGA技術聯(lián)盟】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關推薦

JESD204B的系統(tǒng)級優(yōu)勢

JESD204B串行接口時鐘的優(yōu)勢

如何讓JESD204B在FPGA上工作?FPGA對于JESD204B需要多少速度?

如何去實現(xiàn)JESD204B時鐘?

如何采用系統(tǒng)參考模式設計JESD204B時鐘

JESD204B協(xié)議介紹

JESD204B的優(yōu)勢

JESD204B SystemC module 設計簡介(一)

JESD204B標準及演進歷程

JESD204B使用說明

JESD204B是什么?JESD204B種類

JESD204B是什么?JESD204B種類

評論