本文導讀

以太網頻繁出現通信異常、丟包等現象,是否會想到是硬件電路設計問題?成熟的以太網電路設計看似簡單,但如何保證通信質量,在通信異常時如何快速定位問題,本文將通過實際案例來講述網絡通訊異常的解析過程和處理方案。

一、案例情況

一日,核心板基于TI公司的DP83848KSQ PHY芯片二次開發時搭建一路百兆以太網電路,在研發測試階段,發現以太網電路頻繁出現通信異常,表現為工作一段時間后網絡自動掉線,無法重連。多臺樣機均表現出同樣的現象,于是研發展開一系列的問題定位。

二、現場排查

軟硬件工程師開始各自的問題定位,本文則談談硬件問題定位。

1、電源電路測試

首先先確定電源電路情況,測試PHY芯片工作時和通信異常時的供電電源的電壓,電源電壓穩定,無跌落,電平為3.3V;其次測試紋波噪聲,測試結果也滿足要求。電源電路影響暫可以排除。

2、原理圖檢查

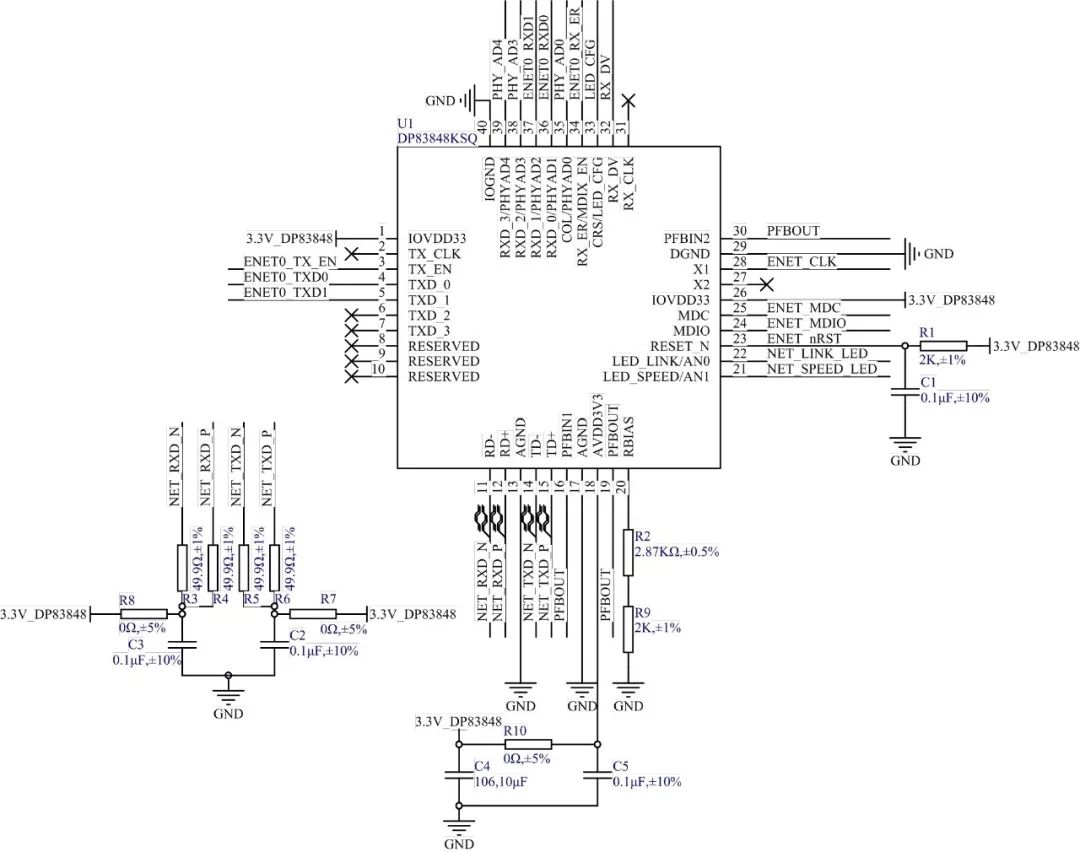

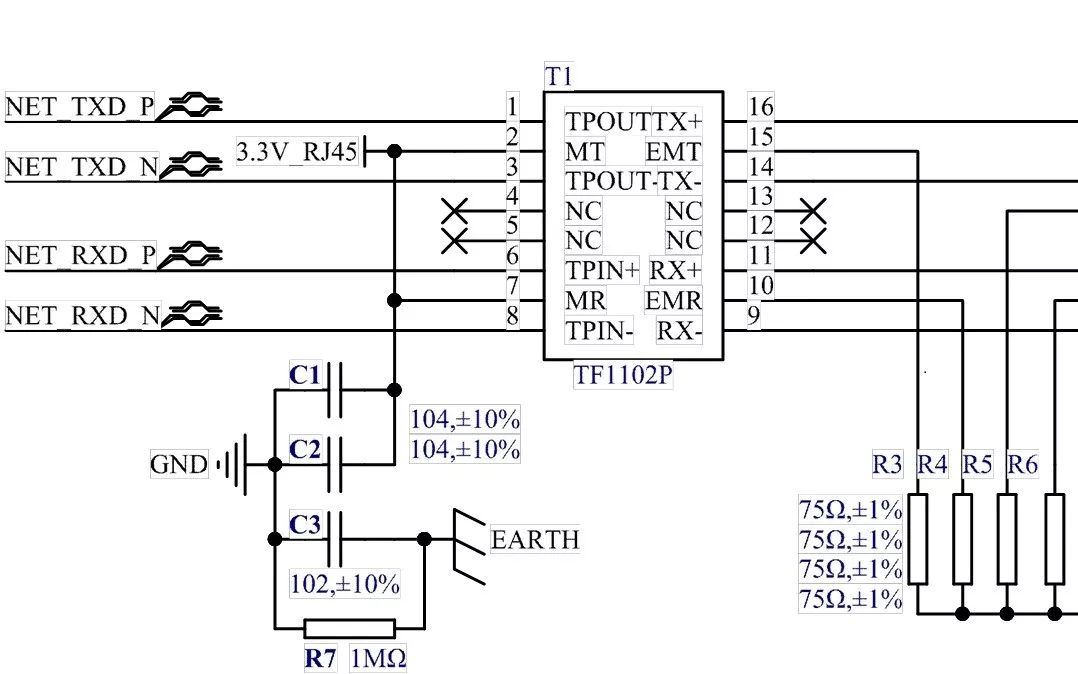

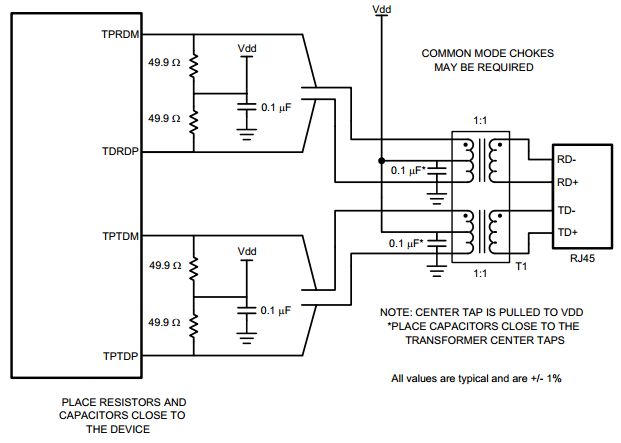

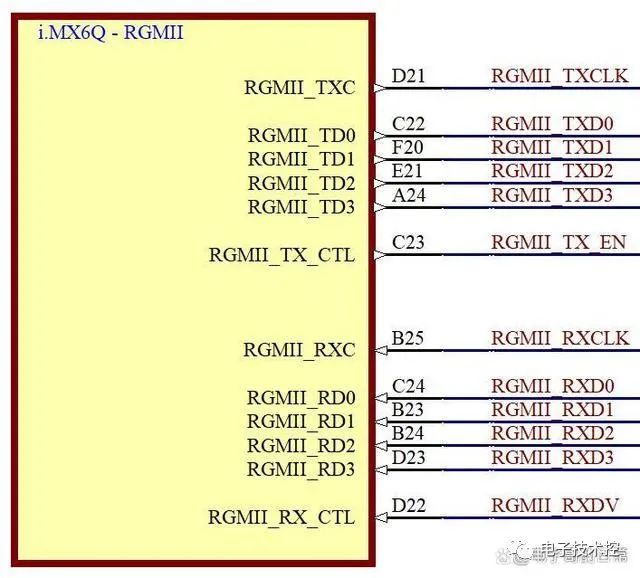

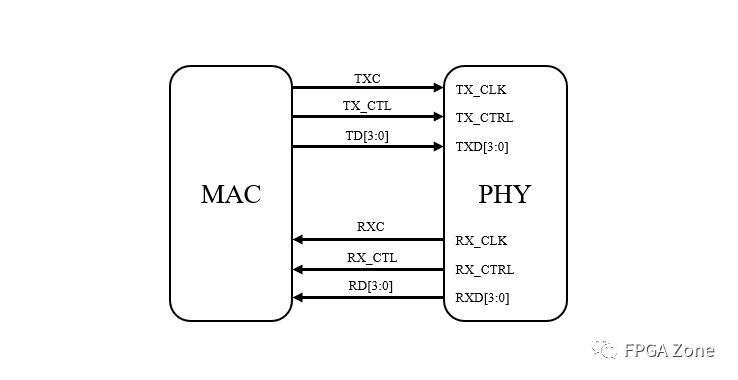

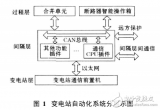

然后從原理圖下手,檢查PHY芯片的外圍電路和對照處理器的引腳順序,如圖1所示,外圍電路接線無誤,設計符合設計規范。繼續檢查以太網的變壓器電路,如圖2所示,該電路也符合設計規范。原理圖設計基本可以排除。

圖1 PHY芯片外圍電路圖

圖2 變壓器外圍電路圖

3、樣機電路測試

-

時序測試:數據信號和控制信號的時序裕量均滿足手冊要求。

-

數據信號波形測試:在信號測試時,發現PHY芯片的數據信號和控制信號有異常的波形,如下圖3、4所示:

圖3 RMII_RXD信號

圖4 RMII_TXD信號

圖5 PHY芯片的IO參數信息

圖6 處理器芯片的IO參數信息

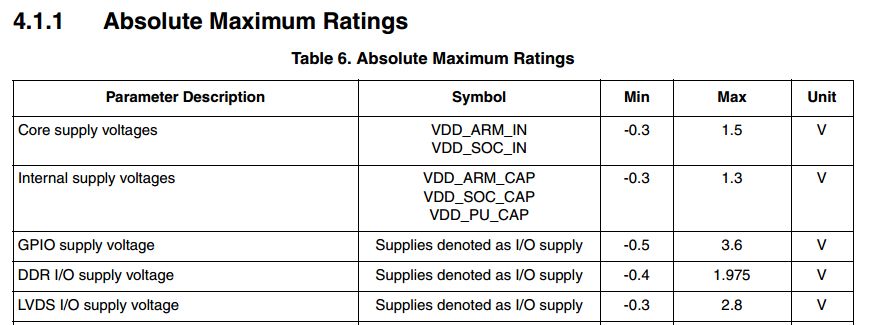

從圖3和圖4可以看出,處理器與PHY端之間的數據信號出現信號完整性問題-反射,均存在振鈴和過沖問題,且過沖的幅值已超出芯片可接受范圍(芯片與處理器的以太網IO均為3.3V供電),可能會導致IO口永久性的損壞,且易產生EMI問題。

于是查看原理圖設計,發現信號線和控制線上均沒有串接電阻,同時PCB上單端信號線沒有做等長和50Ω的阻抗,信號傳輸過程中感受到阻抗突變,導致信號產生反射,繼而產生過沖和振鈴現象。

4、以太網差分電路

差分電路的測試主要是通過物理層一致性測試,通過一致性測試評估差分信號的信號質量。本次測試的目的是為了進一步分析差分信號的設計是否滿足要求。測試結果如下:

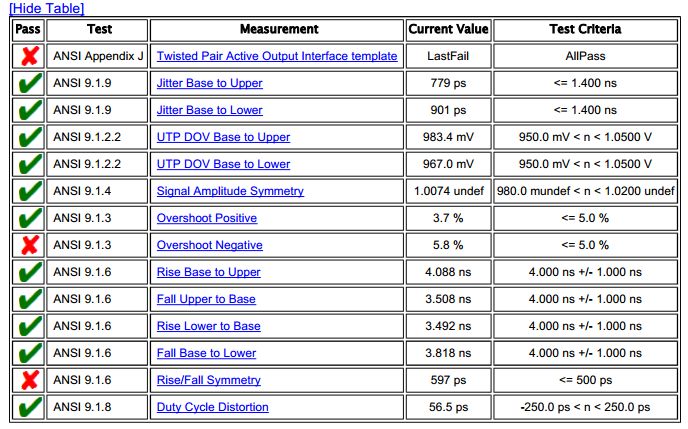

圖7 物理層一致性測試結果

圖8 以太網眼圖模板測試結果

從圖7和圖8可以看出,物理層一致性測試結果為Fail,測試不通過的項主要是以太網眼圖模板測試、負過沖測試、邊沿對稱度測試。從圖8的測試結果可以看出,差分信號的幅值已經超出標準值,已經觸碰到眼圖模板。差分信號的幅值過大,可能是由于信號的反射導致。

變壓器是串聯在差分信號線上的用于隔離的器件,引腳就會產生寄生參數,也會產生阻抗突變,所以也是需要進行考慮的一個方面。于是先排除變壓器的影響,通過更換一個不同型號的變壓器,輸出的結果并沒有太大的差別。繼續著手分析傳輸線的阻抗。

PCB的阻抗又可以從兩方面進行分析。一是走線的阻抗,二是信號線上的匹配電阻。

首先從PCB走線的阻抗進行分析,以太網的差分信號是有差分100Ω阻抗要求,本次采用的是E5071C網絡分析儀進行測試,測試結果如圖9所示:

圖9 差分信號PCB走線阻抗測試結果

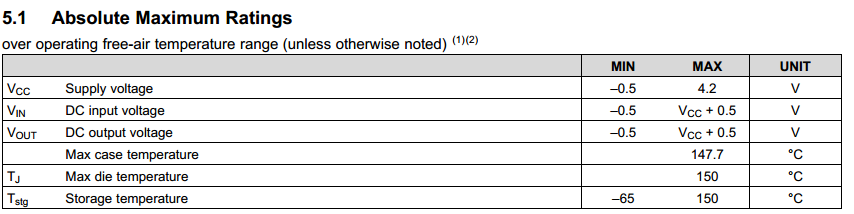

從圖9看出,差分信號的PCB走線阻抗最大值為109Ω,最小值為100Ω,存在這個偏差的原因是在于差分信號線上的保護器件和匹配電阻,有器件必然就會產生焊盤,所以導致實測值與理論值偏差10Ω也是有可能的,由于在PCB設計階段要求差分信號的走線阻抗為100Ω,走線阻抗最大允許偏差±10%,所以實測基本能滿足設計要求。差分信號的阻抗基本符合要求,繼續進行下一項分析。

其次從信號線上的匹配電阻進行分析。由于百兆以太網的PHY芯片到變壓器之間的差分線上有一個49.9Ω的電阻進行匹配走線,如圖10所示。同時隔離變壓器的中間抽頭具有“Bob Smith”終接,通過75Ω電阻和1000pF電容接到機殼地。然而查閱DP83848KSQ芯片的手冊,如圖11所示,提到匹配電阻有Layout要求:49.9Ω電阻和0.1uF退偶電容必須靠近PHY端放置。

圖10 DP83848KSQ芯片差分接口設計圖

圖11 DP83848KSQ芯片Layout指南

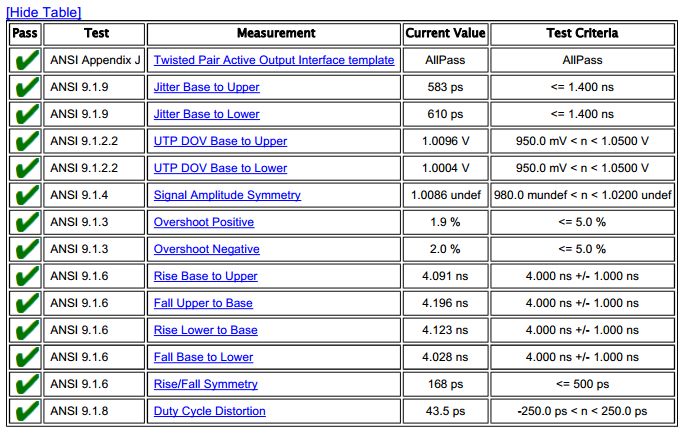

于是查看PCB布局,結果發現實際的布局將電阻電容放置在靠近變壓器的一側。手冊雖然沒有描述到該電阻放置錯誤會有什么影響,于是通過飛線的方法,把電阻電容放置在PHY端,再結合數據線和控制線的反射問題,在信號線的源端串聯一個33Ω的電阻,檢查無誤后,上電進行一致性測試,最終測試結果為Pass,測試結果如圖12、13所示,從圖12可以看出,整改后的眼圖模板測試比整改前的要好,各項測試數據也滿足要求。同時也進行通信穩定性測試,最終通信測試48h后,以太網無掉線現象,同時丟包率為0%。

測試無誤后,重新進行原理圖設計,在信號線和控制線上加入串阻。PCB設計方面,數據線做單端50Ω阻抗匹配,把49.9Ω的電阻和0.1uF電容靠近PHY端放置,差分信號線做100Ω阻抗。重新拿到樣機后進行網絡通信,連續通信三天后無掉線現象,同時丟包率也滿足要求,問題解決。整改后的PCB布局及走線如圖14、15、16所示。

圖12 整改后的以太網眼圖波形

圖13 整改后的以太網一致性測試結果

5、整改后的PCB布局及走線圖

圖14 整改后PHY端數據信號走線及端接電阻布局

圖15 整改后PHY與變壓器端的PCB布局圖

圖16 整改后變壓器與RJ45端的PCB布局圖

三、設計總結

在本次以太網通信異常問題定位時,總結了以下幾點注意事項:

-

PCB走線越短越好;

-

以太網PHY和處理器端的數據線和控制線注意阻抗匹配,避免反射。因為信號在傳輸過程中感受到阻抗不匹配時,容易產生反射,同時驅動能力過大時也會容易產生反射。在原理圖設計時,若無法預測PCB走線長度,建議在信號線和控制線的源端串聯一個22~33Ω的小電阻,且信號線等長和做單端50Ω阻抗處理;

-

PHY端差分信號線上的49.9Ω匹配電阻根據手冊要求放置,盡量靠近PHY端放置;

-

差分信號線需要做差分100Ω的阻抗,同層走線,建議采用4層板PCB;

-

變壓器需靠近RJ45端放置;

-

“Bob Smith”終接需靠近變壓器端放置。

成熟的以太網電路設計看似簡單,但如何保證通信質量,硬件設計也尤為重要。一個很小的降低成本的考慮,可能問題就會在量產時被無限放大,最終面臨的是硬件改版、人力投入、成本增加、項目延期。在設計前期把這些問題考慮進去,就可以避免不必要的問題發生。

圖17 工業品質的M1052跨界核心板

-

以太網

+關注

關注

40文章

5424瀏覽量

171702 -

無線通信

+關注

關注

58文章

4570瀏覽量

143534 -

DP83848

+關注

關注

0文章

4瀏覽量

3919

原文標題:【研發經驗】如何解決以太網故障?

文章出處:【微信號:Zlgmcu7890,微信公眾號:周立功單片機】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

實現以太網通信硬件電路方法

ESP32能否在通過以太網通信的同時保證采樣率和處理能力?

LPC23xx的自適應以太網通信接口設計

S7-200SMART開放以太網通信

基于FPGA的UDP RGMII千兆以太網通信方案

以太網通信網關是什么

保證以太網通信質量,先從硬件設計入手!

保證以太網通信質量,先從硬件設計入手!

評論