工欲善其事,必先利其器。現今的芯片設計已經達到億門級集成度,即便經驗最豐富的設計工程師也無法憑手工完成。在芯片設計過程中,仿真驗證是十分重要的一個環節,以確保芯片進入流片生產環節前符合預期設計性能要求。專門為芯片設計工程師提供仿真和驗證工具的EDA細分行業是整個半導體行業生態鏈中最上游,最高端的節點。全球EDA市場基本上被三家公司霸占:Cadence、Synopsys和Mentor Graphics,其中規模最小的Mentor Graphics已經被西門子收購。經過30多年的行業發展和市場競爭,這三家主要的EDA供應商各有自己的獨特優勢,在全球半導體技術和市場的動態變化中保持相對平衡的格局。

Cadence Protium驗證平臺大顯身手

專注于數字娛樂系統的晶晨半導體(AmLogic)最近推出一款新的多媒體系統級芯片(SoC),其設計周期比傳統設計流程縮短2個月。在競爭異常激烈的消費電子市場,比同行提前2個月上市新產品意味著什么,業界人士應該都很清楚。而實現這一芯片設計背后的功臣就是來自Cadence的FPGA原型驗證平臺Protium S1。

新推出的Protium S1是Cadence基于FPGA的原型驗證平臺,晶晨是該驗證平臺的早期測試參與者之一。受益于該平***有的設計實現和原型驗證加速能力,晶晨可以比以往更早啟動SoC設計的軟件開發。

據晶晨半導體軟件工程總監Jerry Cao稱,使用Protium S1平臺可以同時執行多個設計實例,大大提高了生產力。此外,該平臺與Cadence Palladium Z1企業級硬件仿真加速器共享同一個通用編譯流程,可以充分利用現有Cadence驗證環境,保持平臺間的功能一致性,進一步提高了設計效率。

圖1:Protium S1平臺的完整套件

在最近的深圳新產品媒體發布會上,Cadence公司全球副總裁石豐瑜,以及系統與驗證事業部產品管理與運營副總裁Michal Siwinski,詳細介紹了該公司新推出的這款FPGA原型驗證平臺。Protium S1平臺具有如下性能優勢:

1、高速原型設計:Protium S1平臺具備先進的存儲單元建模和實現能力,可將原型設計啟動時間從數月降至數日,大幅提前固件開發日程。

2、創新的軟件調試能力:Protium S1平臺提供多種提高固件和軟件生產力的功能,包括存儲單元后門讀寫、跨分區轉存波形、force-release語句,以及運行時鐘控制。

3、方便使用與部署:Protium S1平臺和Palladium Z1共享一套通用編譯流程,現有編譯環境的重復利用率最高可達80%,兩個平臺之間可保持前端流程高度一致。

Protium S1采用Xilinx Virtex Ultra Scale FPGA技術,設計容量比上一代平臺提升6倍,性能提高2倍。它與Cadence Palladium Z1企業級仿真平臺前端保持一致,使得初始設計啟動速度較傳統FPGA原型平臺提升80%。除晶晨半導體外,Protium S1已被網絡、消費者類和存儲類市場多家廠商先期采用。相信在大規模SoC設計中,它將成為芯片設計工程師的得力助手。

并行仿真已成今年的EDA設計主流

在硬件仿真和FPGA原型驗證的推動下,軟件環境下的驗證已經成為EDA的關鍵增長領域之一。芯片開發流程越來越需要考慮特定應用的專門需求,現今EDA設計領域的一大主題就是“物聯網(IoT)”。物聯網跨越多個應用領域,包括與移動設備相連的可穿戴電子產品、與機頂盒相連的智能家居、駕駛員輔助系統(ADAS)和車輛互聯等聯網汽車應用,以及用于實現自動化的智能工業、醫療保健、城市和能源管理等。

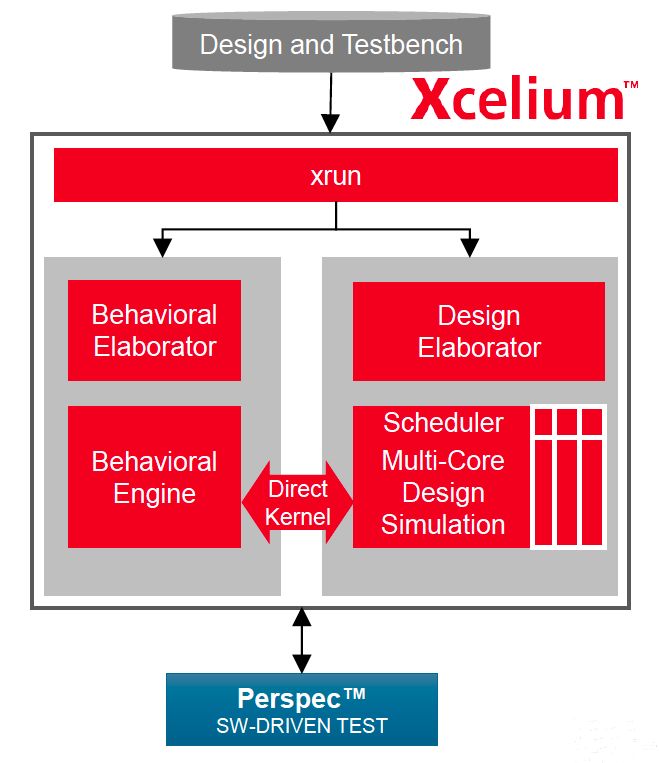

設計驗證的四大核心引擎包括仿真、形式驗證、硬件加速器和FPGA原型驗證,除了繼續改善這些核心引擎外,并行仿真也已經成為今年的EDA主流趨勢。為滿足這一設計需求,Cadence推出了基于多核并行運算技術的并行仿真平臺Xcelium。

Xcelium是已經通過產品流片驗證的第三代并行仿真平臺,其單核版本的性能較Cadence上一代仿真平臺平均可提高2倍,多核版本性能平均可提高5倍以上。這一并行仿真平臺可以大幅加速系統開發,縮短系統級芯片(SoC)的設計時間,其主要亮點如下:

1、多核仿真:Xcelium源于Cadence收購的Rocketick帶來的技術,是基于產品流片的并行仿真平臺。利用Xcelium可顯著縮短執行時間,在寄存器傳輸級(RTL)仿真可平均提速3倍,門級仿真可提高5倍,DFT仿真可提高10倍,節約項目時間達數周至數月。

2、應用廣泛:Xcelium支持多種設計方式和IEEE標準,工程師無需重新編碼即可提升性能。

3、使用方便:Xcelium的編譯流程將設計與驗證測試環境代碼分配至最優引擎,并自動選取最優CPU內核數目,提高執行速度。

4、采用多項專利技術:優化整個SoC驗證時間的新技術包括為達到快速驗證收斂的System Verilog Testbench覆蓋率和多核并行編譯。

圖2:Xcelium的并行仿真架構

Xcelium仿真平臺適用于移動、圖像、服務器、消費電子、物聯網(IoT)和汽車等多個領域,已經在ARM和ST等早期用戶中得到了成功應用,并通過了產品流片驗證。ARM公司技術服務產品部總經理Hobson Bullman表示,Xcelium并行仿真平臺對于基于ARM的SoC設計,在門級仿真可獲得4倍的性能提升,在RTL仿真可獲得5倍的性能提升。基于這些早期試用結果,他相信Xcelium可以幫助ARM及其客戶更快和更可靠地交付復雜的SoC。

“針對智能汽車和工業物聯網應用中復雜的28nm FD-SOI SoC和ASIC設計,快速和可擴展的仿真是滿足嚴苛開發周期的關鍵!”意法半導體公司CPU團隊經理Francois Oswald說,“我們使用Cadence Xcelium并行仿真平臺,在串行模式DFT仿真中得到8倍的速度提升,所以數字和混合信號SoC驗證團隊選擇Xcelium作為標準的仿真解決方案。”

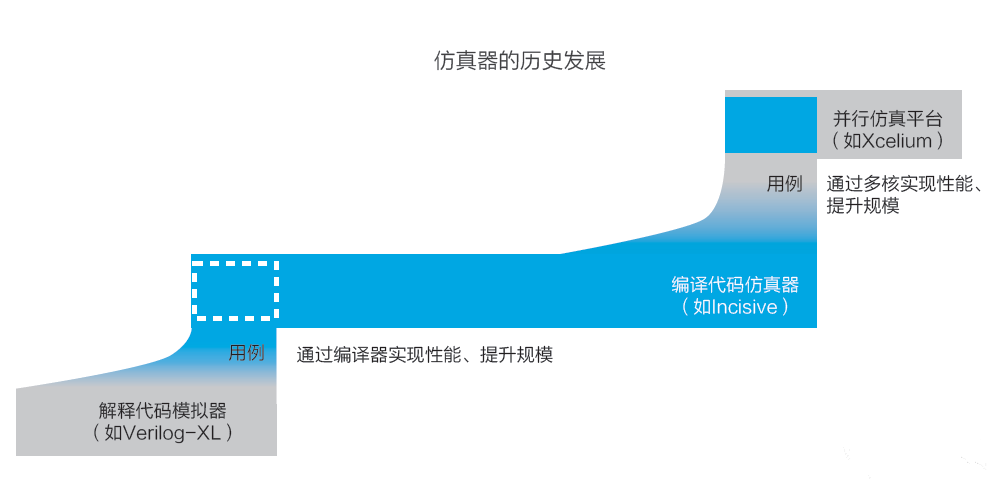

芯片設計仿真技術的發展歷史和未來趨勢

針對芯片設計的第一代商用仿真技術出現于上世紀80年代后期,以Verilog-XL和Rapid Sim等解釋代碼仿真器為代表。其工作機制是先編譯成p代碼再將其解釋執行,因此運行速度極為緩慢,但足夠應付當時的小型設計。

隨著設計規模慢慢變大,90年代中期出現了編譯代碼仿真器來滿足設計對速度、容量的要求。其工作原理是在運行仿真之前,將源代碼轉化為機器代碼。這是第二代仿真技術,開發比較復雜,用了大概三年時間實現對當時的語言和使用模型仿真的支持。自此第二代仿真器一直是業內主流仿真器,并實現了對e、SystemC、SystemVerilog、CPF和UPF等多種新標準的支持。

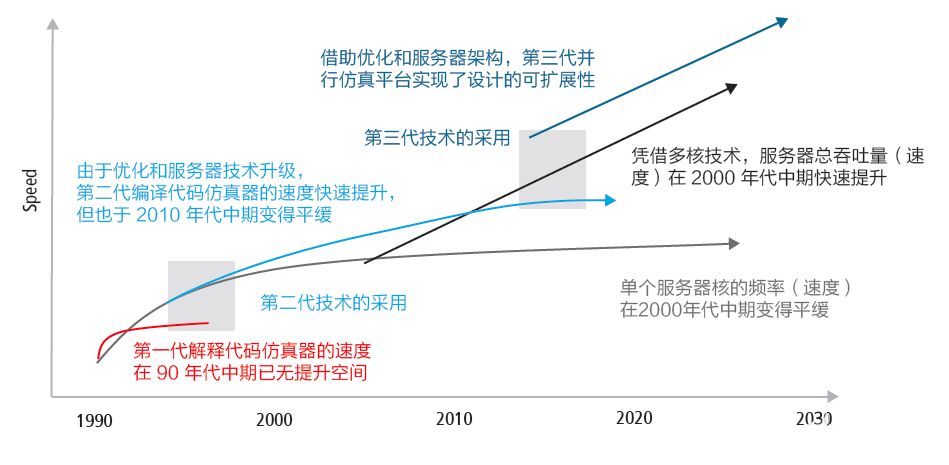

然而,隨著芯片設計尺寸變得越來越大,越來越復雜,第二代仿真技術已無法滿足市場需求。現在的SoC普遍包含百萬門級以上的多核設計,測試這些芯片可能耗費數周之久。幸運的是,為了適應SoC尺寸的增長和復雜度的提升,仿真技術也在迅速發展。最近出現的并行仿真正是這樣一種通過加快測試速度來提高驗證效率的技術。

圖3:三代仿真技術的發展

Cadence推出的Xcelium并行仿真平臺支持標準多核服務器(多達64核)且采用細粒多進程技術,可以將編譯代碼仿真平臺上運行的仿真分解成可加速和不可加速兩個部分。可加速的部分(如門級網標或SystemVerilog RTL部分)由并行引擎處理,驗證工程師無需改變測試平臺、設計或斷言。Xcelium在語言層運作,因此不依賴于工藝節點,也無所謂設計是一個CPU、處理器,還是一個數據通路設計。此外,設計層次也不會造成影響。

圖4:第三代并行仿真技術將成為未來20年的主流

前兩代仿真技術都各自發展了20年左右。我們有理由相信,全新的并行仿真技術將成為未來20年的仿真基礎。

附錄

SoC設計中的主要仿真和驗證工具

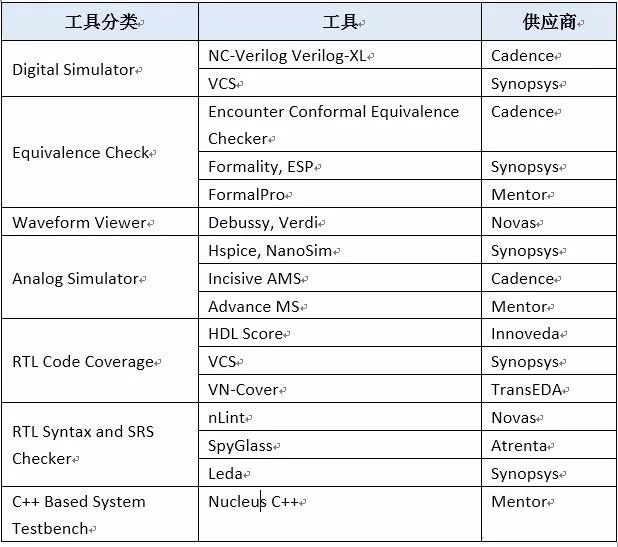

三大EDA供應商都能提供全套的芯片設計解決方案,包括模擬、數字前端、后端、DFT、Signoff等一整套設計工具。Cadence的強項在于模擬和混合信號的模擬仿真和版圖設計,但其Signoff的工具偏弱。Synopsys的優勢在于數字前端、數字后端和PTsignoff,而Mentor的優勢是Calibre signoff和DFT。

此外,Candence和Synopsys還提供IP授權(硬核和軟核),這對中小規模的設計公司很具吸引力。授權的IP通常有memory、Serdes和Power management之類的研發成本或門檻相對較高的硬核。

下表列出了一些SOC設計中常用的主要仿真和驗證工具,供大家參考。

-

仿真

+關注

關注

50文章

4097瀏覽量

133704 -

eda

+關注

關注

71文章

2766瀏覽量

173388

原文標題:未來EDA設計的主流是什么?

文章出處:【微信號:Anxin-360ic,微信公眾號:芯師爺】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

第三代移動通信過渡技術—EDGE

什么是IR-III技術(第三代紅外)?

第三代紅外技術(IR-III)并不是陣列式

第三代紅外(IR3)技術與激光紅外差別

第三代半導體科普,國產任重道遠

EDA技術從何而來?EDA技術發展歷程

第三代半導體材料氮化鎵/GaN 未來發展及技術應用

移動通信向第三代標準的演化與發展討論

第三代移動通信技術定義

什么是射頻EDA仿真軟件?

CAE有限元仿真技術面臨的挑戰有哪些

基于EDA仿真技術的電子時鐘系統設計

基于EDA仿真技術解決FPGA設計開發中故障的方法

EDA未來的的設計主流與三代仿真技術的發展

EDA未來的的設計主流與三代仿真技術的發展

評論